什么是亚稳态

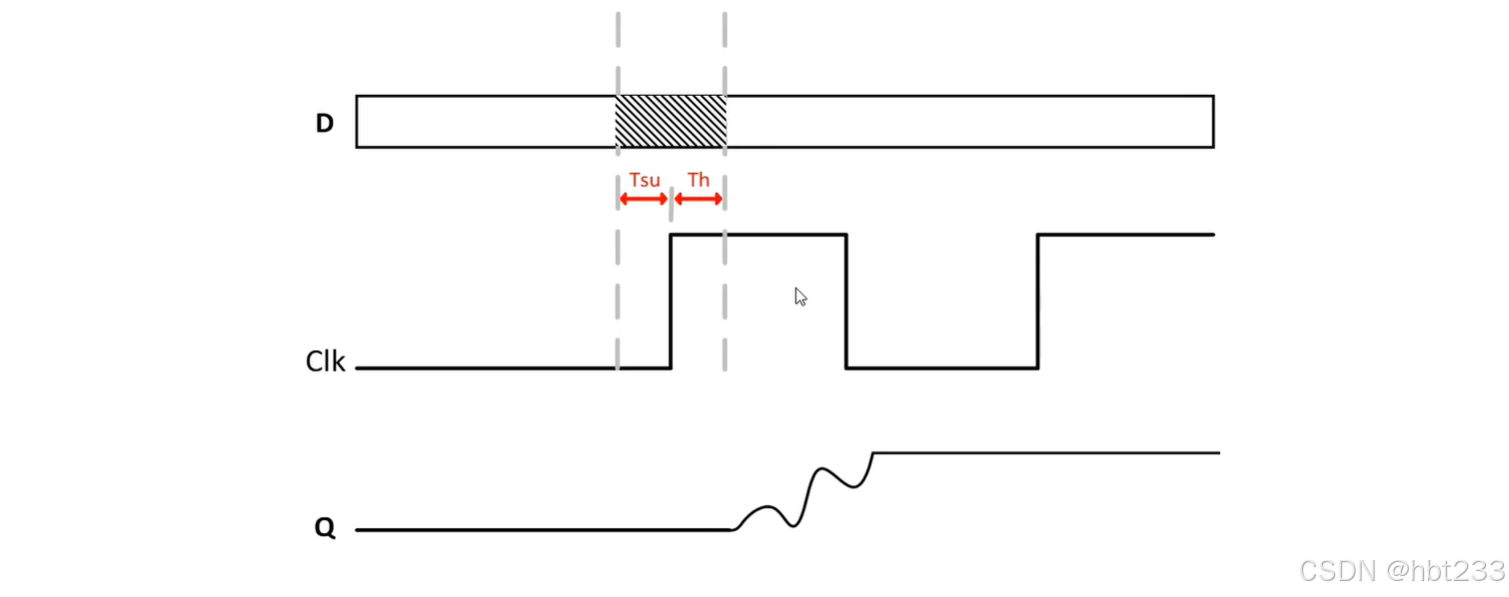

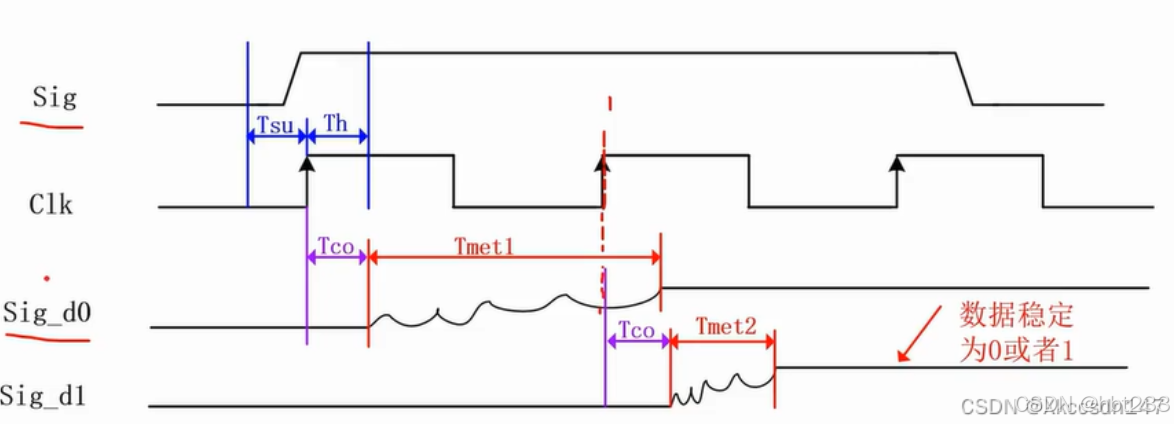

否则D触发器的输出不能快速的到达一个稳定状态。该段时间称为亚稳态窗口

否则D触发器的输出不能快速的到达一个稳定状态。该段时间称为亚稳态窗口

若D端口数据在时钟上升沿前后不稳定,会导致输出Q将是未知的,称为“亚稳态”

若D端口数据在时钟上升沿前后不稳定,会导致输出Q将是未知的,称为“亚稳态”

(具体原理与D触发器内部电路结构有关,不作具体分析)

一个触发器一旦进入亚稳态状态,则无法预测触发器的输出电平,也无法预测什么时候可以稳定在某个确定的电平上,此时触发器的输出端Q在较长时间内处于振荡状态,不等于输入端D。稳定之前的这段时间称作决断时间(resolution time)。经过resolution time之后,输出端Q将会稳定在某个电平上,但是这个稳定之后的电平与输入端D是没有关系的,可能是0也可能是1,结果完全是随机的。

芯片工艺的不同导致震荡的程度不同,还由温度,干扰,辐射,等等一系列的因素。

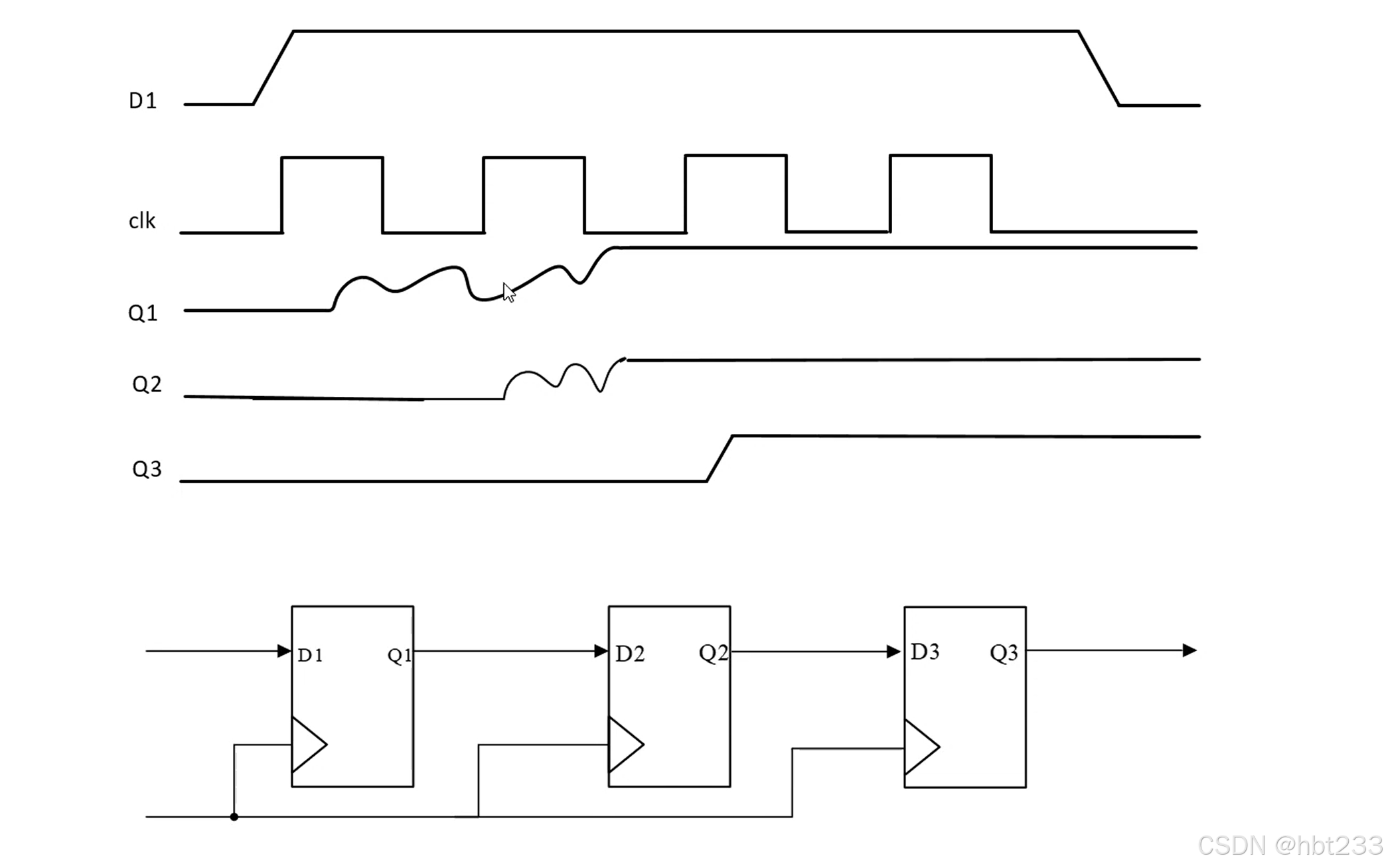

如果时钟频率过高,震荡就会传到下一级D触发器,下一级触发器的输出也会震荡。

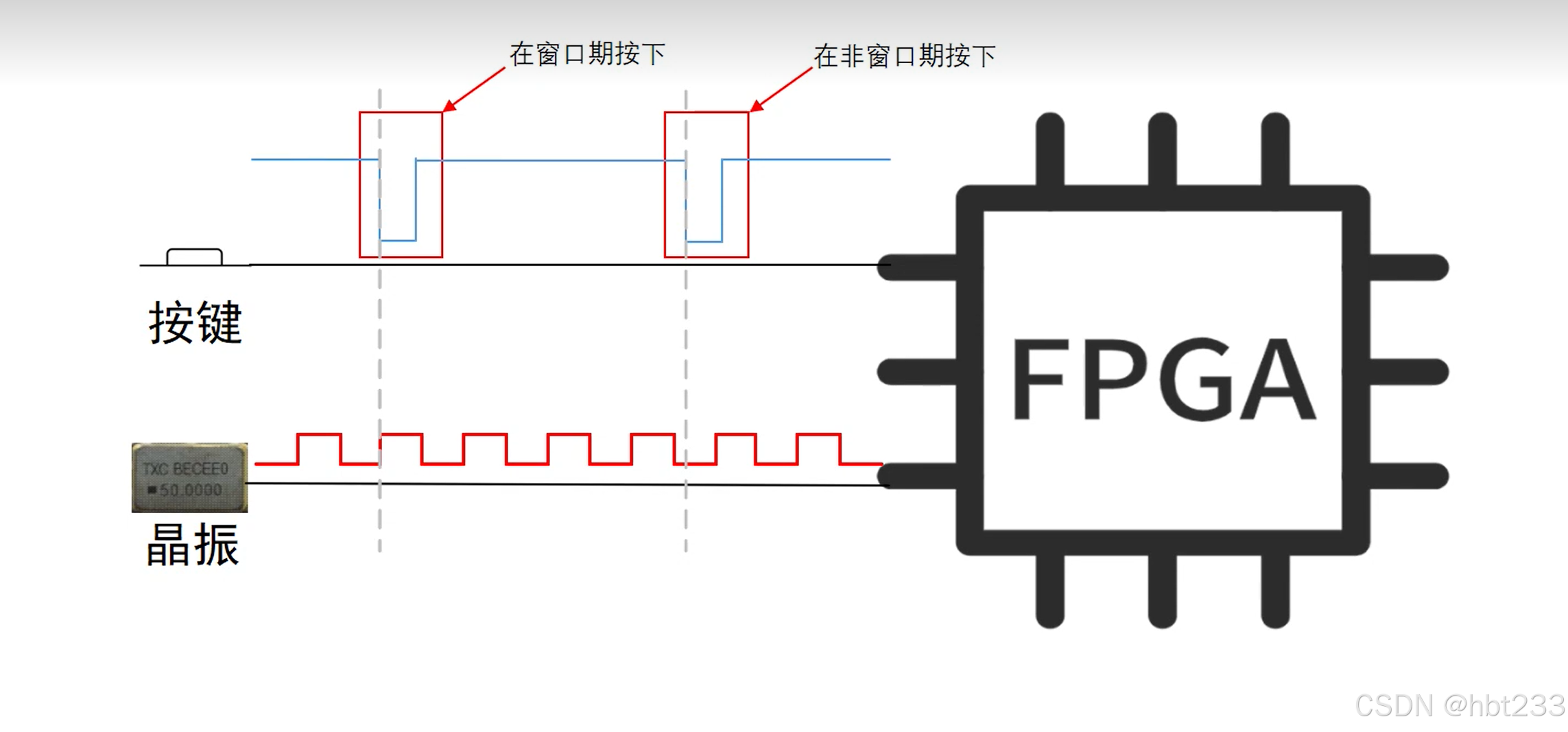

UART串口接收的是异步信号,而异步信号更容易导致亚稳态

异步信号就是信号的驱动端或者是发送方不是与信号的接收端由同一个时钟域的时钟驱动,那么这个信号什么时候发生变化完全就是未知的,是不可控的。所以该数据有更大的概率在D触发器的数据窗口期发生变化,所谓的数据窗口期就是上面讲的D端口的数据在时钟上升沿的前Tsu时间和时钟上升沿之后的Th时间,所以信号在数据窗口期发生变化,就会可能导致接收的D触发器发生亚稳态。

总结就是,异步信号和D触发器不是工作在同一个时钟域,就有更大的概率在数据窗口期发生变化,就跟容易导致D触发器出现亚稳态。

亚稳态导致的危害

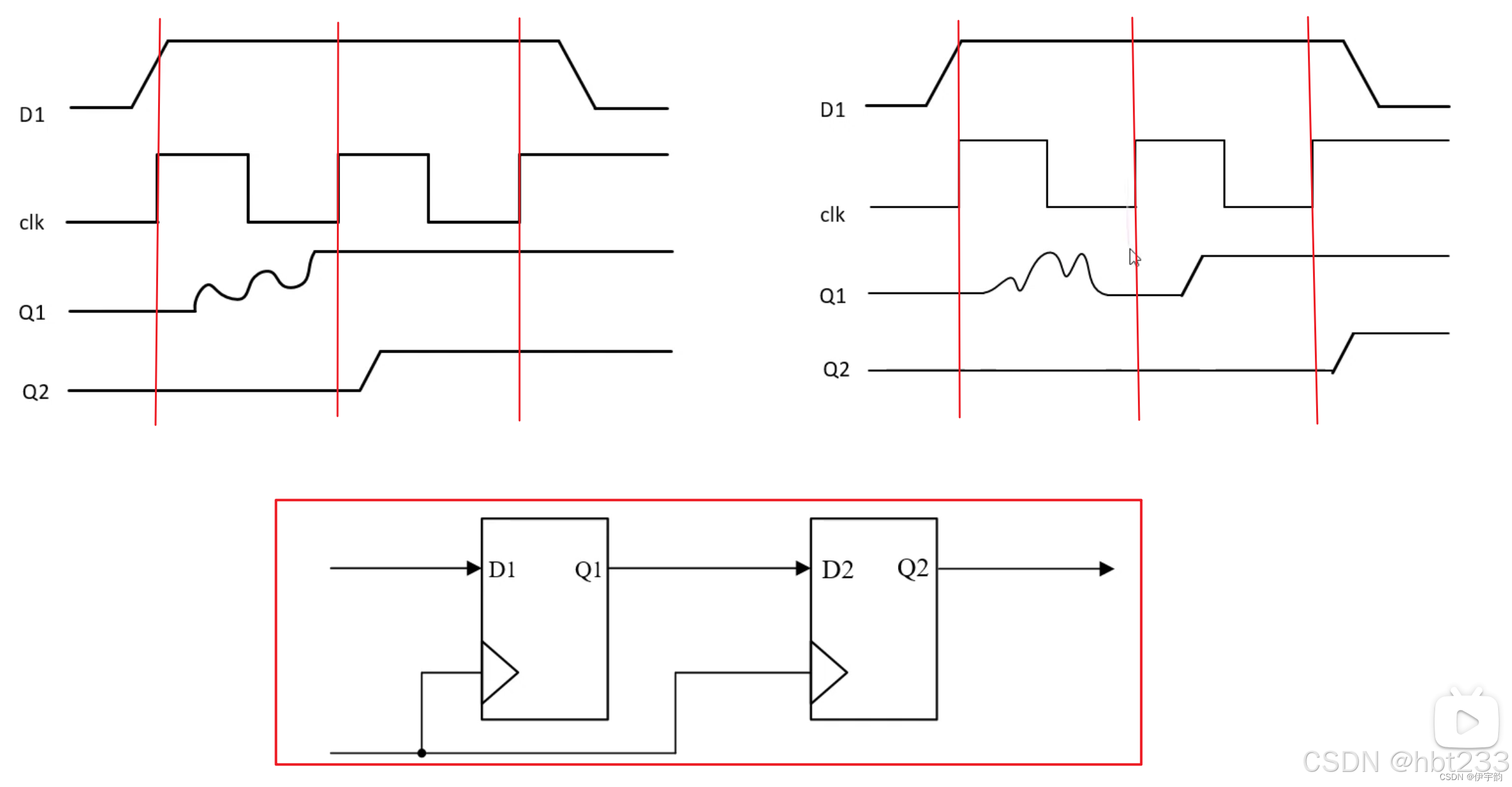

D0在数据窗口期内发生了变化,导致输出出现亚稳态,输出经过dff1和dff2后还没有稳定下来,导致dff1和dff2都进入了亚稳态,进而可能使得在一段时间内dff1和dff2的输出不一致。

解决方法

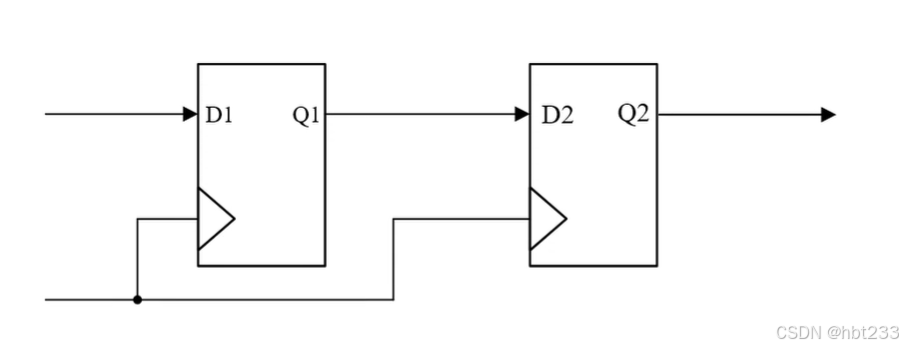

用2个D触发器级联,打2拍,将异步信号转为同步信号,将同步后的信号拿来使用。

至于为什么双触发器可以用作同步器呢?下面就来解释这个问题:

我们将触发器链的第一个触发器称为FF1第二个称为FF2 。异步信号进入本地时钟域的FF1的D端,由于是异步信号,存在亚稳态的风险,输出是非高非低的一个中间态。此时亚稳态传递到后面的电路。如果第一级寄存器输出亚稳态,恢复时间为T1,如果clk的周期小于T1,那么亚稳态将会在第二级寄存器输出,由于第一级亚稳态已经经过clk一个周期的恢复,所以在第二级寄存器输出时,亚稳态恢复至稳态的时间T2将会缩短。T2< T1。

但靠二级触发器也能不能完全避免亚稳态的发生,以上提到亚稳态信号总会由亚稳态自己变成稳态,但是这个时间不是完全确定的。所以只能说双触发器搭建的同步电路只能一定程度上避免亚稳态的发生(不过经过概率计算,双触发器号称将亚稳态发生的概率减少到了几年发生一次)。不过根据以上分析可以很明显发现触发器链越长发生亚稳态的概率越低。

一般系统使用二级触发器做同步化处理已经是足够。但注意双触发器作为同步器只能用在单比特数据的传递中。原因很简单,因为同步器输出只能保证是一个稳态不能不能保证是一个确定的值。故多比特数据使用同步器还是会出现乱码的情况。对于多比特数据的操作一般使用异步FiFO。

其实避免亚稳态的发生主要就是避免异步信号的时钟,使用双触发器同步电路的精华就是将异步信号同步化操作。

总结

3125

3125

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?