目录

2.1CMOS逻辑设计

2.1.1基本的MOS结构

2.1.2 CMOS逻辑门

2.1.3 标准单元

2.1CMOS逻辑设计

2.1.1基本的MOS结构

都知道的NMOS、PMOS,源漏区之间的距离就是晶体管的长度,最短的长度就是流程的特征尺寸。例如,0.25μm技术允许制造具有0.25μm或更大通道长度的MOS晶体管。通过减小尺寸,相同面积内可以集成更多的晶体管,速度也就会更快。

2.1.2 CMOS逻辑门

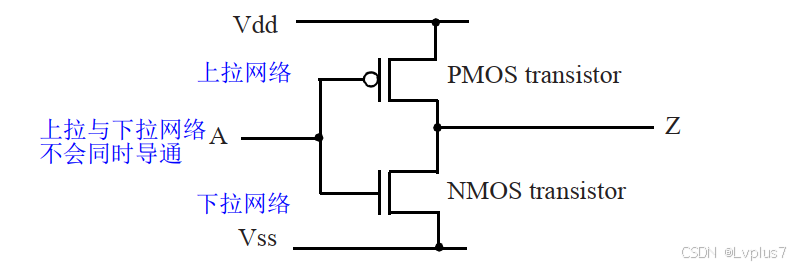

由NMOS PMOS共同构成,CMOS反相器的工作原理在此处省略。

主要了解一下上拉网络PUN、下拉网络PDN的有关概念吧。

CMOS逻辑的一个特点是,不会给前级带来电阻负载,只会带来容性负载,因为前级的输出直接接CMOS的栅,视为电阻无穷大断路。

2.1.3 标准单元

标准单元如与或非门等等,这些单元的功能以及延时都是提前设计好的,设计者可以事先知道。

CMOS逻辑门在输入信号处于稳定逻辑状态时,不会从电源抽取电流(除了漏电流)。这意味着在静态情况下,CMOS电路几乎不消耗电能。可以理解为节点电容充满了电,或者已经完全放电,所以在稳态情况下不会有电流。功耗的主要来源是电路中活动信号的切换。当输入信号变化时,需要对输入端的电容进行充电和放电,这会导致瞬时电流的流动,从而引起功耗。

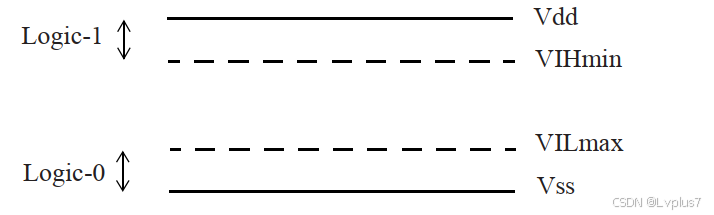

下面的图片表示了逻辑0以及逻辑1的范围:

2.2 CMOS单元的建模

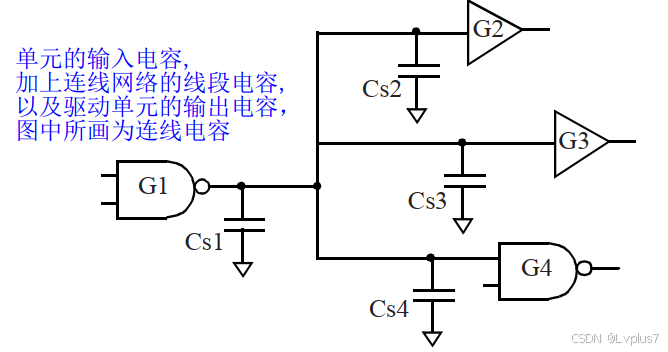

如果一个单元的输出驱动了很多别的单元的输入,那么这个输出引脚上总的电容就是三部分的电容之和:单元的输出电容,驱动单元的输入电容,以及连线电容。

Total cap (Output G1) = Cout(G1) + Cin(G2) + Cin(G3) + Cin(G4) + Cs1 + Cs2 + Cs3 + Cs4

# Cout is the output pin capacitance of the cell.

# Cin is the input pin capacitance of the cell.

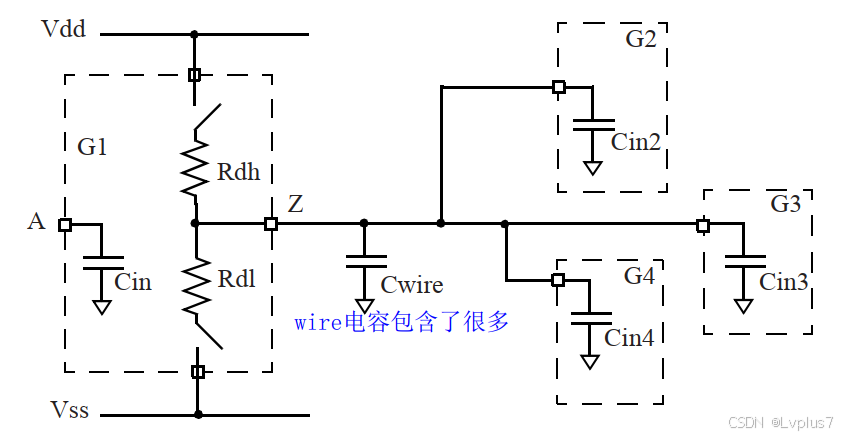

CMOS单元切换电平状态时,切换的速度取决于输出引脚上的 电容被充放电的速度 。输出引脚上的电容分别通过上拉和下拉结构充电和放电。上下拉的通道会对充放电的路径造成电阻,这是影响充放电速度的重要因素。

我们定义:

上拉电阻的倒数称为高电平输出驱动(因为上拉了所以输出就是高电平了,名词由此得来)

输出上拉结构越大,上拉电阻就越小,即单元的输出高电平驱动就越大,较大的输出结构也意味着该单元的面积较大。而输出上拉结构越小,单元的面积就越小,其输出高电平驱动也就越小。相同的道理同样适用于下拉网络,在此不赘述。总之,上下拉的能力通常都是设计的相近。

输出的驱动能力,决定了他能驱动多少的负载,也就是他的扇出(Fanout)。一个单元如果他的输出具有较强的驱动能力,那么他的上下拉网络的阻值必然很小。(可理解为RC一定时,R如果小,C肯定大,CMOS单元只会给前级电路带来容性负载,所以扇出就多了)

Cwire = Cs1 + Cs2 + Cs3 + Cs4

Output charging delay (for high or low) = Rout * (Cwir

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5246

5246

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?