本章主要解决的问题:

什么是STA(静态时序分析)?

串扰以及噪声会对电路产生如何的影响?

分析的有关方法在哪个阶段使用?并且是如何使用的?

目录

1.1纳米级设计

1.2什么是 STA

1.3 为什么是它

1.4设计流程

1.4.1 CMOS数字设计流程

1.4.2 FPGA设计流程

1.4.3 异步设计

1.5 不同阶段的STA

1.6 STA的缺陷

1.7 考虑一下功耗的问题

1.8 可靠性的要求

1.1纳米级设计

在半导体器件的设计中,金属互连线普遍存在。当器件的尺寸缩小的时候,这些互连线将会影响器件的性能。对于深亚微米或纳米级的设计,互连线之间的耦合会引起串扰和噪声,相比于之前的大尺寸设计,这些因素对于纳米级的设计的性能,影响更为关键。

1.2什么是 STA

静态时序分析(Static Timing Analysis)是用于验证数字设计的时序问题的一种工具,作为替代的另一种工具是时序仿真(Timing Simulation)。我们一般所说的时序分析,指的就是以上的两种工具(STA & TS)

静态时序分析:不依靠于外部的输入。主要目的是验证设计能否在给定的频率下工作。

时序仿真:依靠于外加信号源的激励,观察输出的变化情况。

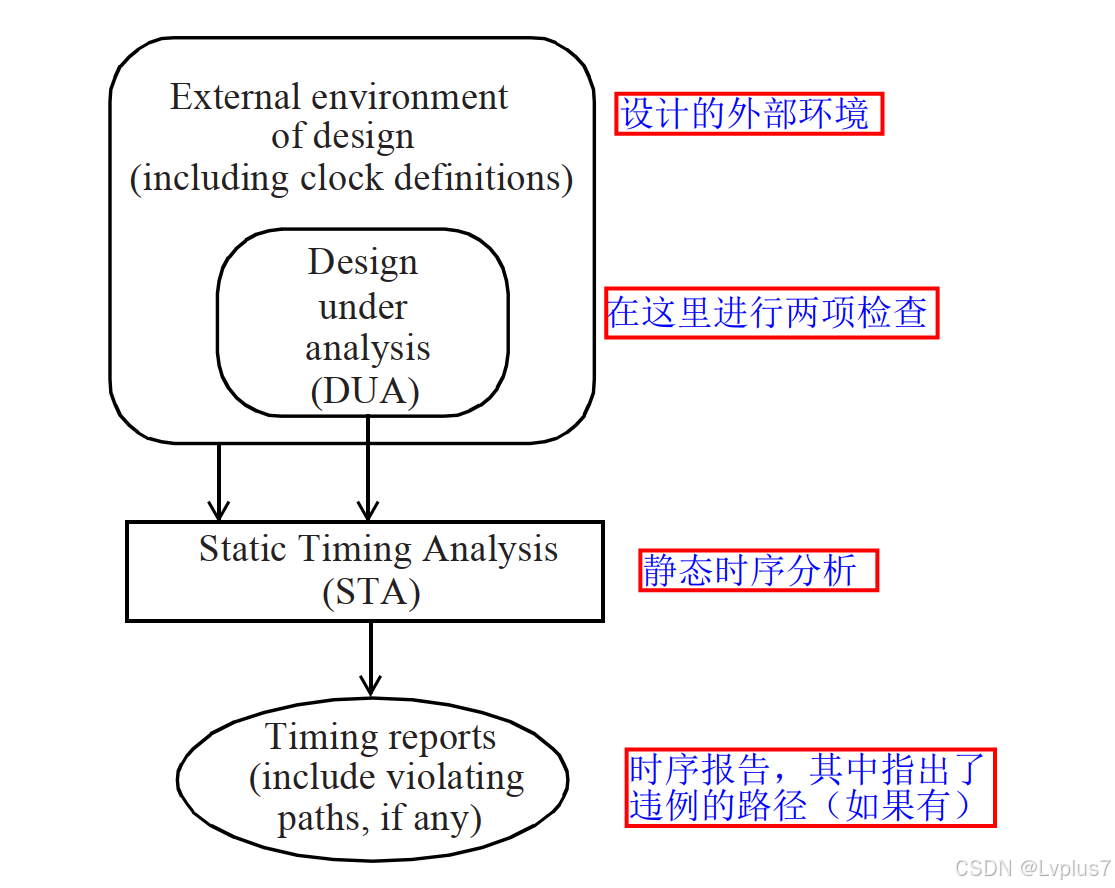

其中的两项检查:tsu建立时间 & thold保持时间 (需要满足两大时序方程,在此处省略)

DUA指定使用硬件描述语言,外部环境如时钟指定使用SDC。

进行STA,设计中所有可能存在的路径都会被检查一遍,所以说STA是一种很彻底很详尽的检查,后一小节也提到了 会更快!

1.3 为什么是它

噪音会对设计的性能造成影响,而逻辑仿真并不能将噪音、串扰和片上差异化的问题考虑在内,所以要选择STA。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1108

1108

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?