这章节介绍了一些特别的STA分析:时间借用(time borrowing),时钟门控(clock gating),非时序检查(non-sequential timing checks)。此外,先进的STA概念如片上变化(on chip variation),统计时序(statistical timing),时序和功耗之间的折中平衡(trade off between timing and power)。

之前的文章 STA 静态时序分析 第十章——鲁棒性分析(1)

之前的文章 STA 静态时序分析 第十章——鲁棒性分析(2)

目录

互连走线差异(Interconnect Variations)

10.9.2 统计分析(Statistical Analysis)

统计时序库(Statistical Timing Libraries)

10.9 统计静态时序分析

迄今为止描述的静态时序分析技术是确定性的,因为分析基于设计中所有时序路径的固定延迟。每条路径的延迟是基于工作条件(condition)以及工艺和互连模型来计算的。虽然可能存在多个模式和多个角点,但在给定的情境下,时序路径延迟是确定性的。

实际上,用于STA的工艺和操作角点的WCS(Worst-Case Slow)或BCF(Best-Case Fast)通常对应于极端的3σ角点,即设计的极限条件。时序库是基于厂商提供的工艺角点模型,并根据操作条件进行表征,从而得出相应角点的单元时序值。例如,最佳情况快速库(best-case fast library)是使用快工艺模型、最高电源电压和最低温度进行表征的。

10.9.1 工艺以及互连差异

全局工艺差异

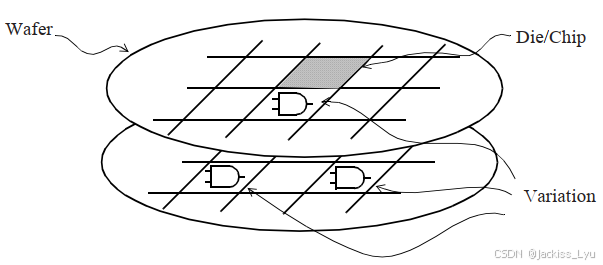

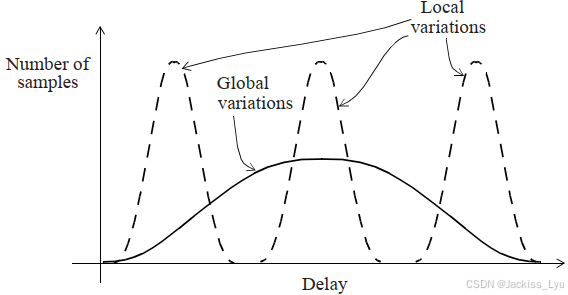

全局工艺变化,也称为晶圆内器件差异,指的是影响整个晶圆上所有器件的工艺参数变化,见下图。整个晶圆上的所有器件都受到这些工艺变化的类似影响——每个器件可能会变慢、变快,或处于两者之间。因此,由全局工艺参数建模的变化旨在捕捉不同晶圆之间的变化。

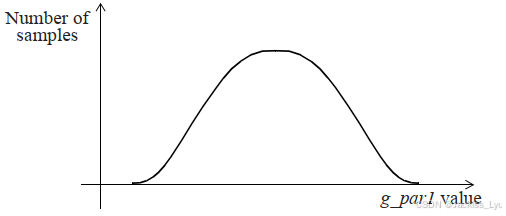

全局参数值例如,g_par1变化的示意图如下图所示。例如,参数g_par1可能对应于标准NMOS器件的饱和电流(IDSsat)。由于这是一个全局参数,晶圆上所有单元实例中的所有NMOS器件都将对应于相同的g_par1值。可以换一种表述方式:所有单元实例中g_par1的变化是完全相关的,或者可以说,晶圆上的g_par1变化是相互关联的。需要注意的是,可能还会有其他全局参数(如g_par2等),例如用于描述PMOS器件饱和电流以及其他相关变量的参数。

不同的全局参数如g_par1,g_part2,彼此是不相关的。不同的全局参数的差异,彼此之间行为不存在关联。这意味着,g_part1 和 g_part2 的变化是相互独立的。在芯片中,g_part1参数可能为其最大值;但是g_part2可能是最小值。

在确定性分析(也就是非统计分析)中,慢工艺模型(slow process models)可能对应于+3σ角点条件,用来描述器件在芯片间变化下的极端慢速情况;而快过程模型(fast process models)则可能对应于-3σ角点条件,用来描述器件在芯片间变化下的极端快速情况。

局部工艺差异

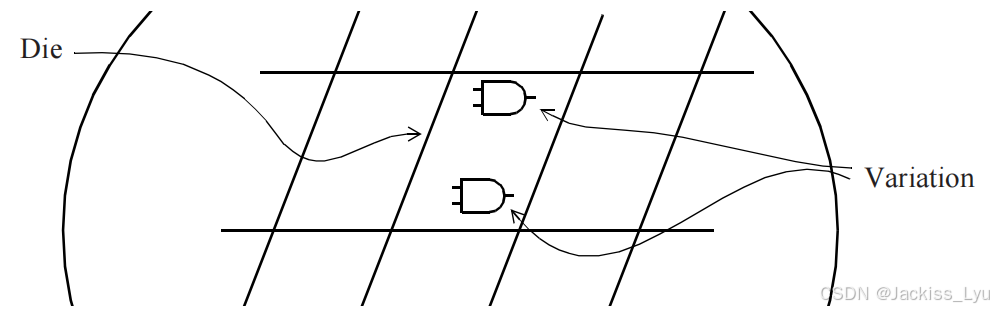

局部工艺差异,也叫做芯片内器件差异,指的是工艺参数的差异导致给定同一晶圆上器件受到不一样的影响。下图中,这意味着,芯片上挨着的两个相同的器件可能有着不同的行为。由局部工艺变化建模的变化旨在捕获晶圆内的随机工艺变化。

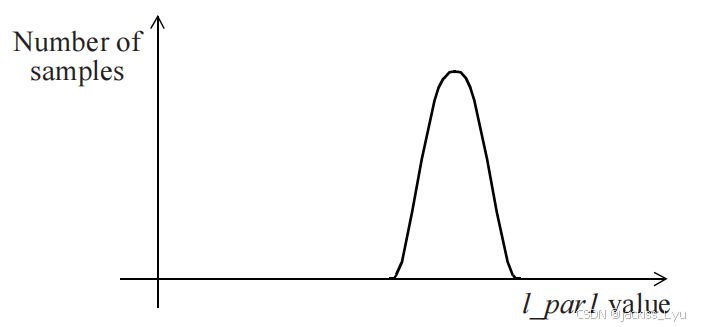

下图显示了局部工艺参数的变化。晶圆上的局部参数变化不会相互影响,并且它们从一个单元实例到另一单元实例的变化是不相关的。这意味着对于同一芯片上的不同器件,局部参数可能具有不同的值。例如,芯片上的不同NAND2单元实例可能会具有不同的局部工艺参数值。即使其它参数(例如输入压摆和输出负载)相同,这也可能导致同一NAND2单元的不同实例具有不同的延迟值。

由于全局参数差异、局部参数差异导致的NAND2单元延时,在下图中展现了。图中说明了,全局参数差异比起来局部参数差异,将会导致更大延迟。

时序分析中的OCV建模(On Chip Variation),旨在捕捉局部工艺差异。由于统计时序模型通常包含了局部工艺差异,使用统计分析模型的OCV分析,不应当在OCV设置中包含局部工艺差异。

互连走线差异(Interconnect Variations)

正如在前几节中所述,有多个互连角点(interconnect corners),这些角点代表了每个金属层的参数变化,这些变化影响了互连的电阻和电容值。通常,这些参数变化包括金属和介电层的厚度,以及金属刻蚀(etch),它会影响金属走线的宽度和间距。通常,影响某一金属层的参数会影响该金属层所有走线的寄生效应,但对其他金属层走线的寄生效应影响较小或没有影响。

第10.8节描述的互连角点用于对互连的变化进行建模,使得所有金属层都映射到同一个互连角点。当使用统计方法建模互连变化时,每个金属层的参数可以独立变化。统计方法会对互连空间中的所有可能变化组合进行建模,因此能够捕捉到那些仅通过分析指定互连角点无法捕捉到的变化。例如,时钟树的启动路径可能在METAL2上,而时钟树的捕获路径则在METAL3上。传统的互连角点时序分析会考虑多个角点,这些角点会一起变化所有金属层的参数,因此无法模拟METAL2位于导致最大延迟的角点,而METAL3位于导致最小延迟的角点的情况。这种组合对应于时序路径的最坏情况,只有通过统计建模互连变化,才能捕捉到这种情况。

10.9.2 统计分析(Statistical Analysis)

上述描述的变化建模是可行的,前提是单元时序模型和互连寄生参数都采用统计建模。除了延迟之外,单元输入端的引脚电容值也采用统计建模。这意味着时序模型是通过有有关于工艺参数 (包括全局和局部工艺参数) 的均值和标准差来描述的。同样,互连的电阻和电容也是通过有关于互连参数的均值和标准差来描述。在第5章中描述的延迟计算过程会获取每个时序弧(包括单元和互连)的延迟,并将其表示为相对于各种参数的均值和标准差。因此,每个延迟都用一个均值和N个标准差来表示(其中N是被统计建模的独立工艺和互连参数的数量)。

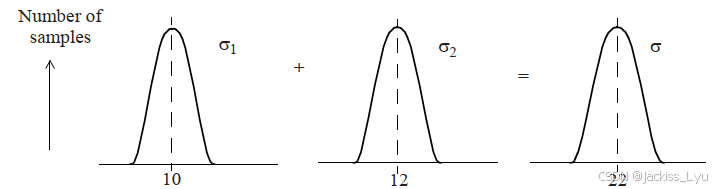

由于每个时序弧的延迟是以统计形式表示的,统计静态时序分析过程会将各时序弧的延迟组合起来,得到路径延迟,路径延迟同样以统计形式表示(包含均值和标准差)。SSTA会将相对于独立工艺和互连参数的标准差映射到一起,得到路径延迟的整体标准差。例如,考虑一个由两个时序弧组成的路径延迟,下图所示。由于每个延迟组件都有其变化,这些变化的组合方式取决于它们是否相关。如果变化来自同一个源(例如由g_par1引起,这些变化是相互关联的),则路径延迟的标准差将简单地等于s1 + s2。然而,如果这些变化是无关的(例如,由l_par1引起),则路径延迟的标准差将等于sqrt(s1² + s2²),这比s1 + s2要小。通过建模局部 (不相关) 工艺变化时路径延迟的标准差变小的现象,也被称为个体延迟变化的统计消除。

在实际设计中,既有相关变化也有不相关变化,这两种变化都需要适当的结合。

启动时钟和捕获时钟的时钟路径延迟也以相同的统计方式进行表示。基于数据和时钟路径延迟,时序裕度作为一个统计变量被得到,并具有其标准值和标准偏差。

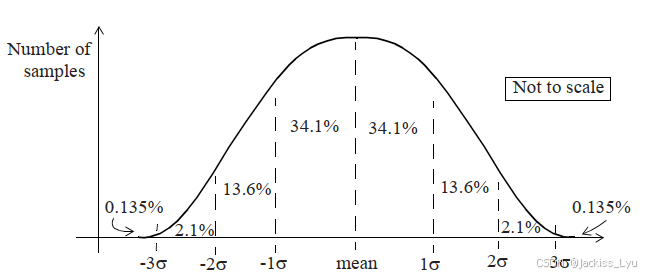

假设数据服从正态分布,基于±3σ,可以获得有效的最小值和最大值。正态分布中的(均值 ± 3σ)对应的量化值为 0.135% 和 99.865%,如下图所示。0.135% 的量化值意味着在该值(均值 - 3σ)以下的结果仅占 0.135%;类似地,99.865% 的量化值意味着 99.865% 的结果小于该值,或者只有 0.135%(100% - 99.865%)的结果大于该值(均值 + 3s)。在 SSTA(静态时序分析)报告中,实际的上下限被称为量化值,设计师可以选择用于分析的量化值,比如 0.5% 或 99.5%,这对应于(均值 ± 2.576s)。

在噪声和串扰分析中,路径延迟和使用的时序窗口都通过统计方法建模,并根据不同的参数使用均值和标准偏差来表示。基于路径的时序裕量分布,SSTA报告每条路径的时序裕量的均值、标准偏差以及量化值,通过这些数据可以根据所需的统计置信度判断路径是否满足时序要求。

统计时序库(Statistical Timing Libraries)

在统计STA中,标准单元库以及设计中用到的其他宏的库,提供了不同环境下的时序模型。例如,在最小Vdd-高温角下进行的分析使用了在此条件下进行表征的库,但是工艺参数进行了统计建模。库中包含了既有标准的参数值,也有参数的变化值的时序模型。对于N个工艺参量,一个在电源电压为0.9V,温度为125C下进行表征的时序库,可能包括:

- 具有标准工艺参数的时序模型

- 参数i为(标准值+1σ)的时序模型,其他参数保持为标准值;

- 参数i为(标准值- 1σ)的时序模型,其他参数保持为标准值;

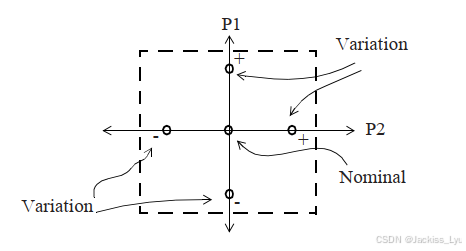

对于一个简化的例子,其中有两个互不相关的工艺参数,时序模型是以标准参数值以及参数值的变化来表征的,如下图。

互连统计差异

对于每个金属层,有着三个互不相关的参数。

- 金属刻蚀:控制了金属线宽,以及与临近导体的空间距离。金属层上大的刻蚀可以减小金属线宽(同时增大了电阻),增大了与临近走线的距离(减少了与临近网络的耦合电容)。该参数表示为导体宽度的差异。

- 金属层厚:更厚的金属,意味着与下层金属之间更大的电容。该参数表示为导体厚度的差异。

- 金属间介质层厚度(Inter Metal Dielectric Thickness):更大的介质层厚度,减少了金属与下层之间的耦合。该参数表示为金属间介质层厚度的变化。

SSTA 结果

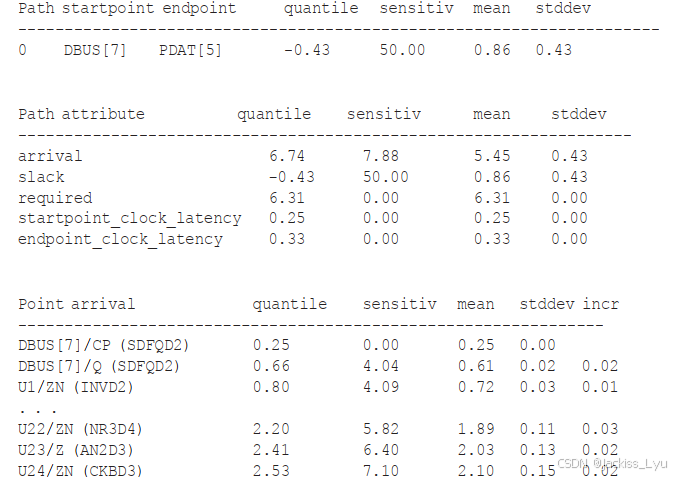

统计分析的输出结果提供了路径裕度的均值和有效的角值(effective corner values)。下面展示了一个SSTA报告示例,适用于建立时间检查,也就是最大路径分析。

注解:报告中的quantile(分位值), sensitiv(敏感值), mean(均值), stddev(标准差)

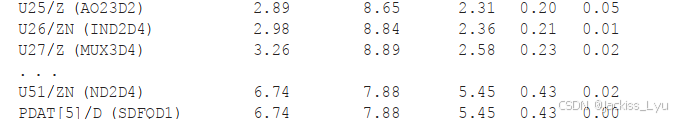

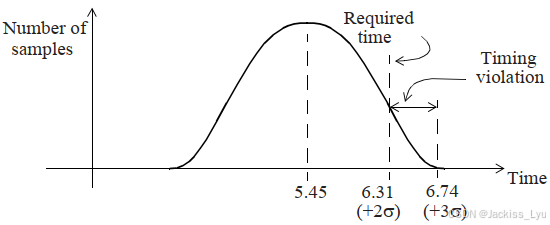

上述报告显示,虽然时序路径的均值满足要求,但0.135%分位值出现了0.43ns的违例——路径余量分位值为-0.43ns。路径余量的均值为+0.86ns,标准差为0.43ns。这意味着分布的±2σ范围内满足要求。由于95.5%的分布位于±2σ变动范围内,这表明仅有2.275%的制造零件会出现定时违例(其余的2.275%分布具有较大的正路径余量)。因此,设置2.275%的分位值将显示余量为0或没有时序违例。到达时间和路径余量的分布下图所示。

需要注意的是,上述报告是针对建立时间路径的,因此分位值列提供了上界分位值(例如路径延迟的+3σ值)——保持时间路径将指定等效的下界分位值(例如路径延迟的-3σ值)。报告中的“敏感度(sensitiv)”列指的是敏感度,它是标准差与均值的比率(以百分比表示)。在路径裕度方面,通常希望敏感度较小,这意味着即使存在变化,路径仍然能够通过。如果敏感度较高,则路径的可靠性会受到较大波动的影响。报告中的“增量(incr)”列指定了该行的增量标准差。

通过使用单元和互连的统计模型,统计时序方法分析设计在角点环境条件下的表现,并探讨由于工艺和互连参数变化导致的空间变化。例如,在最坏情况下的电压和温度(VT)进行统计分析将探索整个全球工艺和互连空间。同样,在最佳情况下的电压和温度(VT)进行的统计分析也会探索整个工艺和互连空间。这些分析可以与传统的角点分析进行对比,传统的角点分析只会探索工艺和互连空间的单一点。

10.10 时序违例路径

在本节中,我们提供了一些示例,突出设计人员在调试 STA 结果时需要关注的关键方面。这些示例中有些仅包含了 STA 报告中的相关摘录。

没有找到时序路径

有可能STA报告中,出现了没有找到路径,或者是裕度无穷大的情况。可能由于以下原因:

- 时序路径中断了

- 路径不存在

- 伪路径

在这些情况下,需要仔细调试约束,以识别导致路径被隔断的约束。一种方法是移除所有伪路径设置和时序中断,然后查看该路径是否可以被时序分析。(时序中断是从 STA 中移除一个时序弧,可以通过使用第7.10节中描述的 setdisabletiming 规格来实现。)

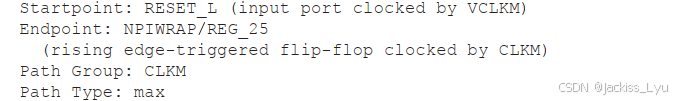

跨时钟域

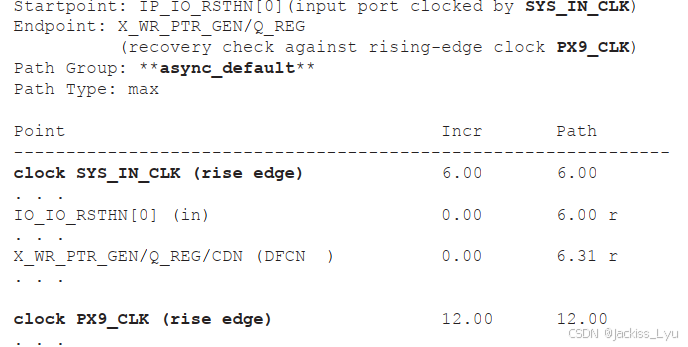

![]()

首先需要注意的是,这条路径从输入端口开始,最终到达触发器的清除引脚,而且正在验证该清除引脚的恢复时间(参见库恢复时间)。这条路径跨越了两个不同的时钟域,一个是SYS_IN_CLK(启动输入的时钟),另一个是PX9_CLK(在触发器处检查恢复时序的时钟)。尽管从时序报告中看不到这一点,但从设计的角度来看,可以检查这两个时钟是否是完全异步的,以及这两个时钟域之间的路径是否应被视为虚假路径。

经验: 验证启动时钟和捕获时钟,以及它们之间的路径是否有效。

翻转衍生时钟

当在创建衍生时钟的时候,-invert 选项需要谨慎使用。如果对于衍生时钟使用了这个选项,STA就会假设在指定位置生成的时钟符合指定的类型。然而基于指定的逻辑,有可能这样的波形在设计中无法出现。STA通常会生成错误或者警告信息表示这样的衍生时钟是无法实现的,但是分析通常是会继续的。

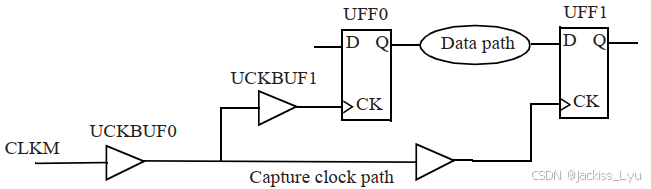

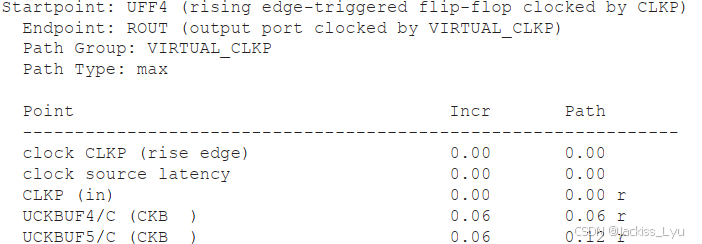

假设我们如下定义,使用下图的电路图:

create_clock -name CLKM -period 10 -waveform {0 5} \

[get_ports CLKM]

create_generated_clock -name CLKGEN -divide_by 1 -invert \

-source [get_ports CLKM] [get_pins UCKBUF0/C]

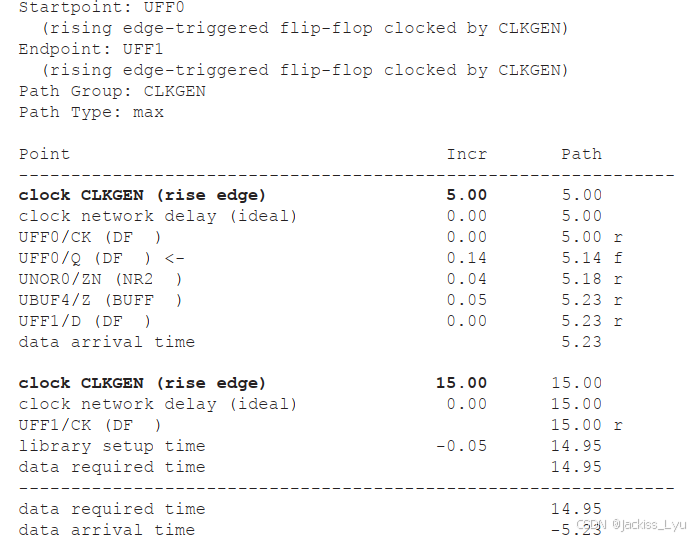

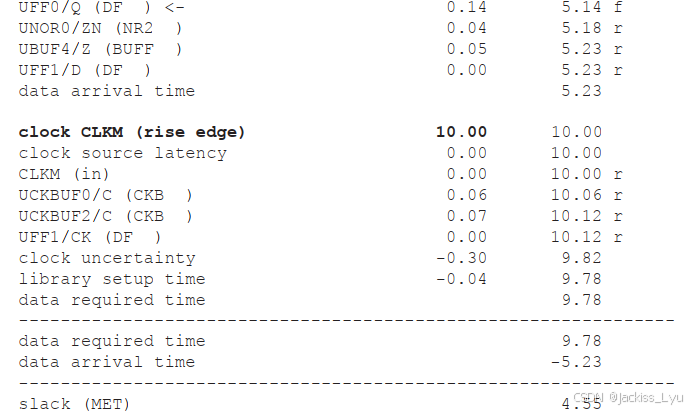

下面是基于以上代码的建立时间检查时序报告

![]()

可以注意到,STA坚定认为UCKBUF0输出的波形是CLKM时钟的翻转时钟。因此,上升沿在5ns,而且建立时间中捕获时间的边沿在15ns。除了时钟的上升沿出现在5ns而不是0ns之外,从时序报告上看不出来有啥错误。我们需要注意,出现错误的部分是发起时钟和捕获时钟所在的共同路径,所以建立时间检查,保持时间检查全都执行的很好。由STA产生的警告和错误需要被认真的分析和理解。

STA将会按照要求创造一个衍生时钟无论他是否可以实现。

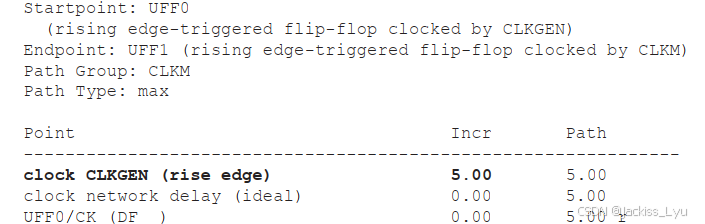

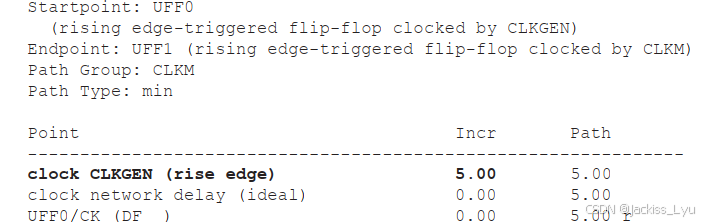

现在来把 -invert 选项移动到 UCKBUF1 单元的输出,看看发生什么。此时的UCKBUF1不在公共路径上。

create_clock -name CLKM -period 10 -waveform {0 5} \

[get_ports CLKM]

create_generated_clock -name CLKGEN -divide_by 1 -invert \

-source [get_ports CLKM] [get_pins UCKBUF1/C]

这个路径看起来像一个半周期路径,但是这不对,因为在实际的逻辑中,并没有反相。STA认为UCKBUF1随后产生的时钟就如create_generated_clock 指令指定的一样。因此上升沿在5ns。捕获时钟使用的是CLKM,它的下个有效边沿在10ns。下面是保持时间报告:

通常STA的输出会包含一个警告或者错误,提示用户衍生时钟是无法实现的。调试这种时序路径的最好办法就是去真实画出捕获寄存器、发射寄存器上的时钟波形,尝试去理解时序报告中展示出来的边沿,是否真的有效。

经验:检查捕获时钟、发射时钟的边沿,看看他们是否真正存在。

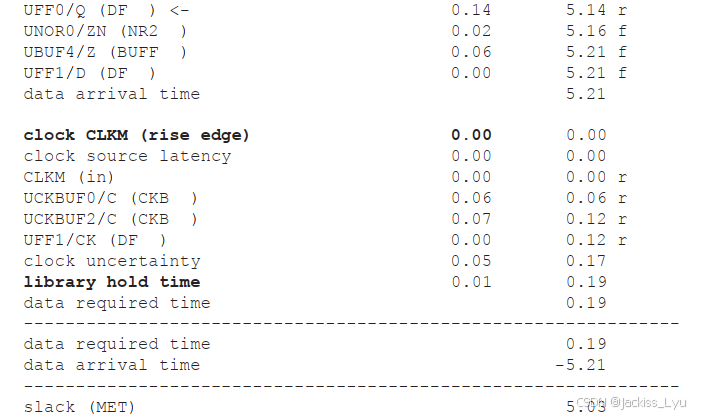

缺少虚拟时钟延迟

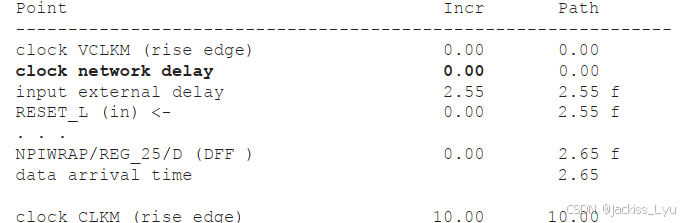

考虑下面的时序报告

这是从一个输入引脚开始的路径,请注意开始到达时间标记为0,这就意味着用于定义在RESET_L引脚上输入到达时间的VCLKM时钟,不存在延时。最有可能的是这是一个虚拟时钟,这也就是他到达时间缺失的原因。

经验:当使用虚拟时钟的时候,确保虚拟时钟的延时已经指定。或者使用了 set_input_delay , set_output_delay进行了约束。

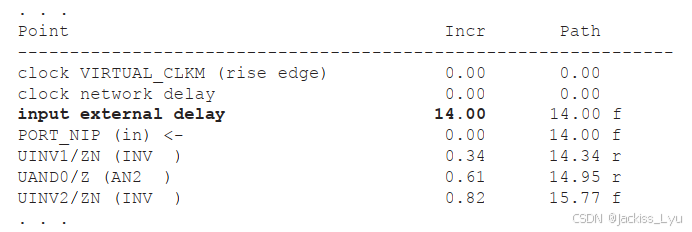

极大的IO延时

当输入或输出路径存在时序违例的时候,第一个需要检查的是时钟的延迟,它作为指定输入到达时间或要求的输出时间的参考。

第二需要检查的是输入、输出延时,也就是在某条输入路径上的输入到达时间,或在某条输出路径上所要求的输出时间。在指定的频率下,我们会发现这些延时经常无法满足要求。输入到达时间通常是报告中的第一个值,要求的输出时间通常是报告中的最后一个值。

注意这里的输入到达时间为14ns,在这个例子中,输入到达时间的设定中存在错误,因为这个值被设置的太大了。

经验:查看输入、输出路径的时候,检查一下外部延时是否在合理的区间内。

不正确的 IO 缓冲延时

当一条路径经过输入或输出buffer的时候,有可能因为大的buffer延时,从而导致错误。下面的例子中,请注意输出buffer的延时为18ns,这是由于输出引脚大的负载值导致的。

经验:注意大的不合理的buffer延时,以及不合理的负载值。

错误的延迟值

时序路径违例的时候,需要去检查发射时钟以及捕获时钟的延时值是否合理。这是为了保证这些时钟的压摆值在一个合理的区间内。不论是错误的延时值,还是时钟树建立过程中错误的时钟平衡都会导致发射时钟、捕获时钟路径的大的压摆,从而导致时序违例。

经验:检查压摆值是否合理

半周期路径

我们需要检查违例的时序路径的时钟域。更深一步,我们需要去检查发射时钟以及捕获时钟所使用的边沿,某些情况下,可能存在半周期路径,上升沿到下降沿,或者是下降沿到上升沿,它无法满足时序的要求,或者是半周期路径不存在。

经验:保证数据路径有充足的时间传播。

大的延时及转换时间

这可能是由于

- 网络扇出较大:未适当缓冲

- 网络较长:网络需要插入缓冲器

- 内存路径:由于内存输入路径的较长的建立时间,输出路径较长的输入延时。

- 低强度单元:由于在设计中标有“don’t touch”,因此未被更换的单元;

缺少多周期保持

对于N周期的建立时间约束,通常我们会看到N-1周期的保持时间约束没有写,这就会导致工具在修复保持时间违例的时候插入需要没有必要的延时单元。

路径没有优化

这种路径可能存在STA的违例。可以通过检查数据路径来分析这个问题。有可能数据路径上延时较大的逻辑单元可以经过优化,从而达到延时更小的逻辑,同时保持功能不变。

仍然无法满足时序要求的路径

如果数据路径具有强驱动能力的单元,而该路径仍然时序违例,则需要检查布线延迟和线负载较高的引脚。这可能是下一个改进方法:也许可以将单元移动得更近一些,从而可以减少线负载和布线延迟。

如果路径仍然无法满足时序要求,怎么办?

可以利用有效偏移(useful skew)来帮助时序收敛。有效偏移是指故意使时钟树失衡,尤其是时序违例路径的发起时钟和捕获时钟路径,从而使时序在该路径上收敛。通常,这意味着可以延迟捕获时钟,以使捕获触发器的时钟在数据准备就绪稍后到达。当然,这假定了后续数据路径,即下一级触发器到触发器的数据路径上有足够的裕量。

也可以尝试相反的操作,也就是说,可以使发起时钟路径更短,以便更早地发起来自发起触发器的数据,从而帮助满足建立时间要求。同样,只有在前一级触发器到触发器路径具有多余的裕量时,才能做到这一点。

有效偏移技术不仅可用于修复建立时间违例,还可用于修复保持时间违例。此技术的一个缺点是,如果设计具有多种操作模式,则有用偏斜可能会在另一种模式下引起问题。

10.11 验证时序约束

当芯片的规模增大的时候,这也就要STA的时序签核。只依赖于STA的风险在于,STA依赖于时序约束是否好。因此,我们就需要仔细考虑有关于时序约束的验证。

检查路径例外

部分工具可以基于设计的网表,检查伪路径以及多周期路径的真实性。他可以决定对于给定的伪路径或者多周期路径的约束是否是有效的。此外这些工具可以基于设计的网表,告诉设计者潜藏的伪路径以及多周期路径,但是其中的部分路径不是有效的。这是因为工具根据电路的逻辑结构去决定是否存在伪路径或者多周期路径,通常会使用一些验证方法;但是设计人员对于电路的逻辑功能有着更深入的了解,更清楚其中哪些是伪路径,哪些是多周期路径。因此工具指出的伪路径和多周期路径在STA应用之前,需要被设计人员检查。此外,还存在着一些路径的例外,他们是基于电路的逻辑功能的,无法被工具所提取,设计人员需要自行进行定义。

时序约束中最大的风险就在于路径例外,因此,需要格外认真地检查伪路径和多周期路径。在同时能选择伪路径和多周期路径的时候,更推荐使用多周期路径,因为这样做起码能够保证该路径有一定的时序约束,然而设置为伪路径存在时序优化过程中路径完全被忽略的风险。实际上,这些时序路径需要经过若干个周期进行采样,因此设置为多周期路径是更为保险的做法。

检查时钟域交叉

工具可以保证设计中的所有时钟域交叉都是有效的。这些工具也有能力进行伪路径的时序约束。工具还能检测出来违规的时钟域交叉,也就是数据经过两个不同的时钟域,但不存在时钟同步逻辑。这种情况下,工具可以自行添加时钟同步逻辑来修改时序的违例。请注意,并不是所有的异步时钟域交叉都需要时钟同步逻辑。这取决于数据的性质,以及数据是否需要在一个周期或者几个周期后进行捕获。

使用STA去检查异步时钟域交叉的另一个方法是,设置比较大的时钟不确定度,令其与采样时钟的周期相等。这样可以确保至少存在一些时序违例行为,根据这些时序违例行为,可以确定适当的路径例外,或者将时钟同步逻辑添加到设计中。

验证 IO 和时钟约束的有效性

这是个挑战。时序仿真通常去检查设计中所有时钟的有效性。系统时序仿真是为了验证IO时序,保证芯片不存在任何时序问题的情况下,可以与外围设备交流。

至此,STA 正文部分已经翻译完毕

部分内容翻译自“Static Timing Analysis for Nanometer Designs A Practical Approach” 欢迎指正!

5971

5971

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?