【致读者】

为了帮助大家更好的理解FPGA中的高速数据总线接口:我创建了一个【FPGA硬件技术交流群】,群内聚焦:

FPGA技术分享

实战问题讨论与答疑

行业动态与职业发展交流

我们致力于打造一个共同攻克FPGA开发中各种“疑难杂症”的优质社区。若您对本专题感兴趣,欢迎私信我 “FPGA” 加入群聊

————————————————

一 引言

在复杂的FPGA系统设计中,不同IP核之间的通信需要一套标准化的接口协议。AXI4-Lite作为ARM AMBA协议家族中的轻量级成员,专门为简单的控制寄存器访问而优化,是每个FPGA工程师必须掌握的基础知识。

二 AXI4-Lite的定位

AXI4-Lite是AXI4协议的简化版本,专为低带宽、简单的控制寄存器访问而设计。它移除了AXI4-FULL的复杂特性,保留了最基本的读写功能,实现了硬件接口的极大简化。

适用场景分析:

- IP核的配置寄存器访问

- 状态寄存器的读取

- 低速外设的控制

- 需要简单总线接口的定制逻辑

与AXI4-FULL的"重型卡车"相比,AXI4-Lite更像是城市中的"配送小车"——灵活、简单、高效地完成点对点的配送任务。

三 AXI4-Lite接口信号全解析

1 全局信号

- ACLK - 全局时钟信号

- ARESETn - 全局复位信号(低电平有效)

2 写通道

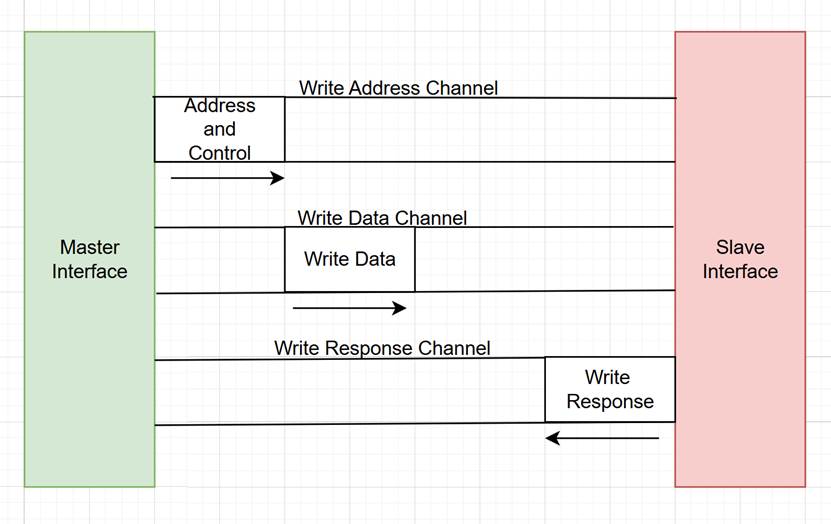

AXI4_LITE的写通道如下图所示,可以看出包括写地址通道、写数据通道、和写响应通道

写地址通道(主→从):

- AWVALID - 写地址有效

- AWREADY - 写地址就绪

- AWADDR - 写地址(通常32位)

- AWPROT - 保护类型(可选)

写数据通道(主→从):

- WVALID - 写数据有效

- WREADY - 写数据就绪

- WDATA - 写数据(32位或64位)

- WSTRB - 字节选通信号

Ps: WSTRB信号指示哪些字节 lane 是有效的,WSTRB[3:0] 对应 WDATA[31:0] 的4个字节每个bit为1表示对应的字节有效。

写响应通道(从→主):

- BVALID - 写响应有效

- BREADY - 写响应就绪

- BRESP - 写响应状态

BRESP 响应类型如下:

2'b00 - OKAY:正常访问成功

2'b01 - EXOKAY:独占访问成功

2'b10 - SLVERR:从设备错误

2'b11 - DECERR:互连解码错误

3 读通道

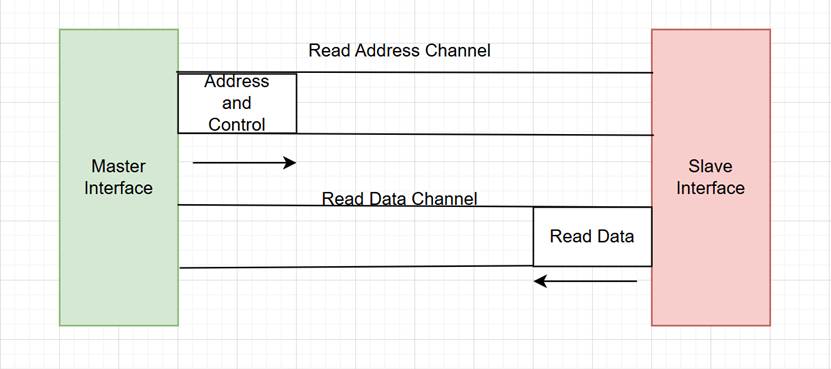

AXI4_LITE的读通道如下图所示,可以看出主要包括读地址通道、读数据应答通道。

读地址通道(主→从):

- ARVALID - 读地址有效

- ARREADY - 读地址就绪

- ARADDR - 读地址

- ARPROT - 保护类型(可选)

读数据通道(从→主):

- RVALID - 读数据有效

- RREADY - 读数据就绪

- RDATA - 读数据

- RRESP - 读响应状态

RRESP 响应类型如下:

2'b00 - OKAY:正常访问成功

2'b01 - EXOKAY:独占访问成功

2'b10 - SLVERR:从设备错误

2'b11 - DECERR:互连解码错误

四 AXI4-Lite事务时序详解

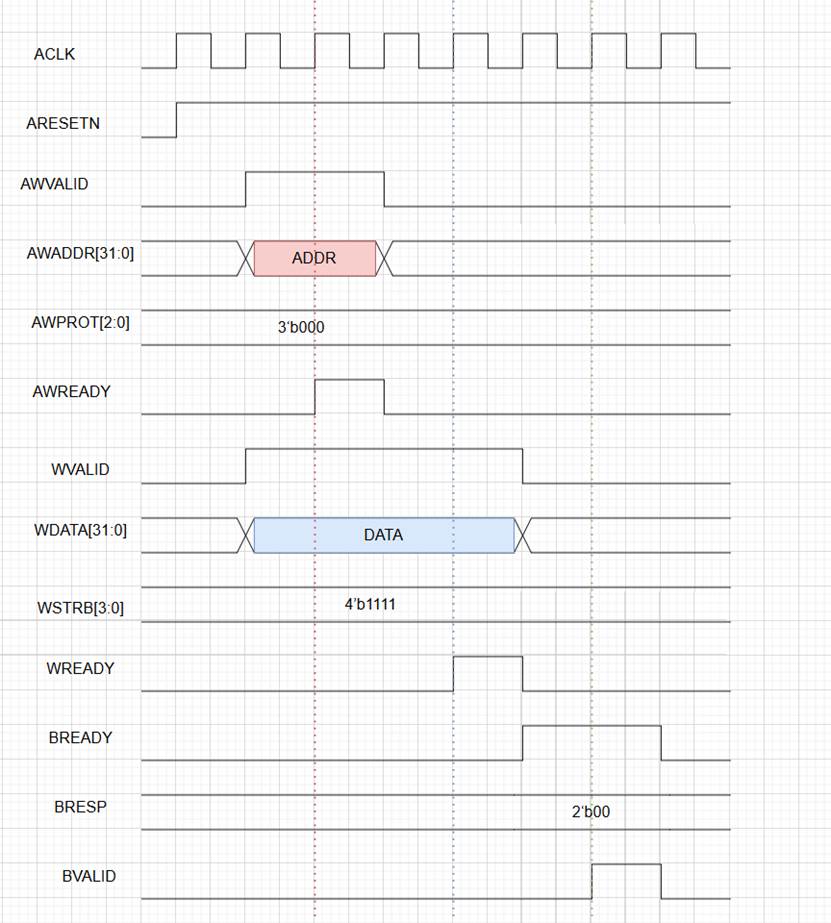

1 写事务时序

- 主设备在AWVALID有效时提供地址AWADDR

- 从设备在准备好接收地址时置位AWREADY

- 主设备在WVALID有效时提供数据WDATA和字节选通WSTRB

- 从设备在准备好接收数据时置位WREADY

- 从设备完成写入后,通过BVALID和BRESP提供响应

注意:虽然说AWREADY信号可能会提前拉高,但是主机写入地址后必须主动拉高AWVALID信号,AWVALID不能等待AWREADY拉高后才拉高

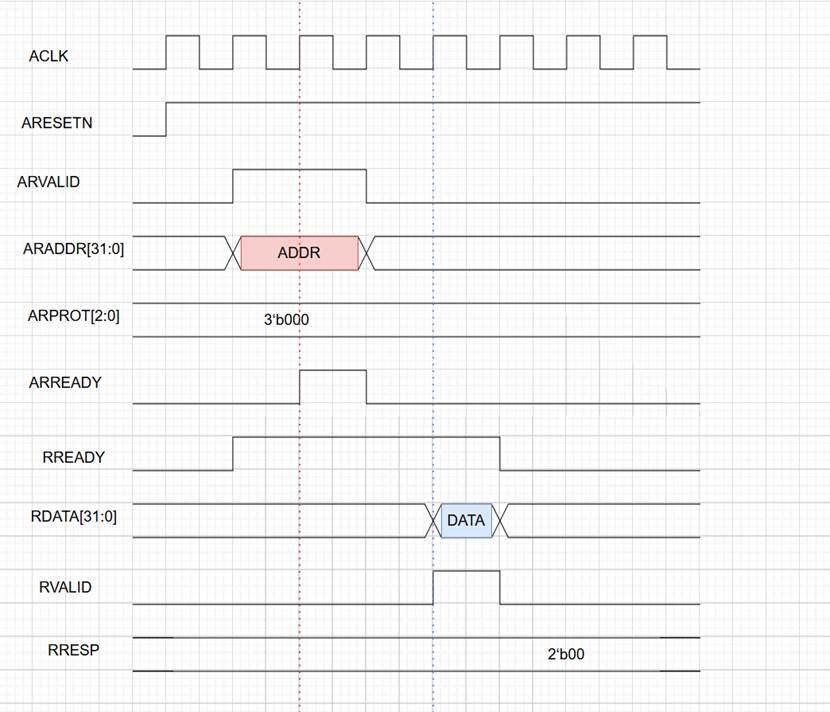

2 读事务时序

- 主设备在ARVALID有效时提供地址ARADDR

- 从设备在准备好接收地址时置位ARREADY

- 从设备在数据准备好时置位RVALID并提供RDATA和RRESP

- 主设备在准备好接收数据时置位RREADY

五 AXI4_LITE的核心特性

1. 架构非常简化

与AXI4_FULL对比,仅保留了ADDR/DATA/READY/VALID 等信号,结构比AXI4_FULL简化太多,以下代码是AXI4LITE的从设备接口示例

// AXI4-Lite从设备接口示例

module axi4_lite_slave #(

parameter ADDR_WIDTH = 32,

parameter DATA_WIDTH = 32

)(

// 全局信号

input wire ACLK,

input wire ARESETn,

// 写地址通道

input wire [ADDR_WIDTH-1:0] AWADDR,

input wire AWVALID,

output reg AWREADY,

// 写数据通道

input wire [DATA_WIDTH-1:0] WDATA,

input wire [DATA_WIDTH/8-1:0] WSTRB,

input wire WVALID,

output reg WREADY,

// 写响应通道

output reg [1:0] BRESP,

output reg BVALID,

input wire BREADY,

// 读地址通道

input wire [ADDR_WIDTH-1:0] ARADDR,

input wire ARVALID,

output reg ARREADY,

// 读数据通道

output reg [DATA_WIDTH-1:0] RDATA,

output reg [1:0] RRESP,

output reg RVALID,

input wire RREADY,

// 用户逻辑接口

output reg [DATA_WIDTH-1:0] reg_data_out,

input wire [DATA_WIDTH-1:0] reg_data_in,

output reg write_enable,

output reg read_enable

);

2. 无突发传输

AXI4-Lite不支持突发传输,每次事务只传输一个数据。这大大简化了控制逻辑,但限制了带宽。

3. 固定的数据位宽

通常使用32位或64位数据总线,无需处理动态位宽调整。

六 实际应用案例

如下是一个寄存器控制模块。

module register_bank #(

parameter NUM_REGS = 16

)(

// AXI4-Lite从设备接口

input wire ACLK,

input wire ARESETn,

// ... 其他AXI4-Lite信号

// 寄存器输出

output reg [31:0] control_regs [0:NUM_REGS-1]

);

// 内部信号

reg [31:0] register_file [0:NUM_REGS-1];

reg write_active, read_active;

// 写事务处理

always @(posedge ACLK or negedge ARESETn) begin

if (!ARESETn) begin

// 复位寄存器

for (int i = 0; i < NUM_REGS; i = i + 1)

register_file[i] <= 32'h0;

write_active <= 1'b0;

end else if (AWVALID && AWREADY) begin

write_active <= 1'b1;

end else if (write_active && WVALID && WREADY) begin

// 根据字节选通写入数据

for (int i = 0; i < 4; i = i + 1) begin

if (WSTRB[i])

register_file[AWADDR[5:2]][(i*8)+:8] <= WDATA[(i*8)+:8];

end

write_active <= 1'b0;

end

end

// 读事务处理

always @(posedge ACLK or negedge ARESETn) begin

if (!ARESETn) begin

RDATA <= 32'h0;

read_active <= 1'b0;

end else if (ARVALID && ARREADY) begin

read_active <= 1'b1;

RDATA <= register_file[ARADDR[5:2]];

end else if (read_active && RREADY && RVALID) begin

read_active <= 1'b0;

end

end

endmodule

七 调试技巧与常见问题

1. 死锁避免

- 确保VALID信号不会无限期等待READY

- READY信号应该在一定周期内响应VALID

2. 时序收敛

- AXI4-Lite接口通常不是时序关键路径

- 但仍需满足建立和保持时间要求

3. 仿真验证

使用AXI Verification IP验证设计正确性。

总结

AXI4-Lite以其简洁性、易用性和低资源消耗,成为FPGA系统中寄存器控制的理想选择。掌握AXI4-Lite意味着:

- 理解标准化接口:为学习更复杂的AXI协议打下基础

- 提高代码复用性:基于标准接口的设计更容易集成和重用

- 加速系统集成:在复杂系统中快速实现控制通路。

AXI4-LITE总线详解与应用

AXI4-LITE总线详解与应用

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?