《FPGA基础知识》系列导航

本专栏专为FPGA新手打造的Xilinx平台入门指南。旨在手把手带你走通从代码、仿真、约束到生成比特流并烧录的全过程。

本篇是该系列的第二篇内容

上一篇:FPGA基础知识(一):FPGA的并行世界always/assign

下一篇:FPGA基础知识(三):彻底理解阻塞赋值与非阻塞赋值

一 引言

在数字电路设计中,时钟与复位是构建任何稳定可靠的FPGA系统的基石。它们如同系统的心跳与重启键,共同确保了电路的正确启动和有序运行。本文将深入探讨这两个核心概念,帮助您从根本上掌握FPGA设计的关键要素。

二 时钟:数字电路的心跳节拍

1 时钟的本质

时钟信号是周期性的方波信号,为同步数字电路提供统一的时间基准。在FPGA中,时钟的每个上升沿(或下降沿)标志着寄存器采样数据的时刻,所有的状态变化都发生在此时钟边沿。

2 时钟的关键参数

- 频率:决定系统运行速度

- 占空比:高低电平的时间比例

- 抖动:时钟边沿的不确定性

- 偏移:时钟到达不同寄存器的时间差异

3 时钟管理技巧

- 使用PLL/MMCM生成所需频率

- 注意时钟之间的相位关系

- 合理约束时钟时序

三 复位: 系统的初始化保障

1 复位的重要性

复位电路确保系统从上电开始就处于已知的确定状态。没有可靠的复位机制,寄存器可能处于随机状态,导致系统行为不可预测。

2 同步复位 vs 异步复位

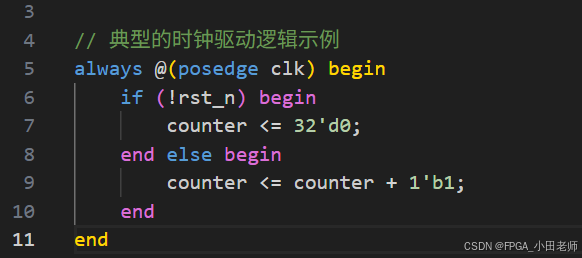

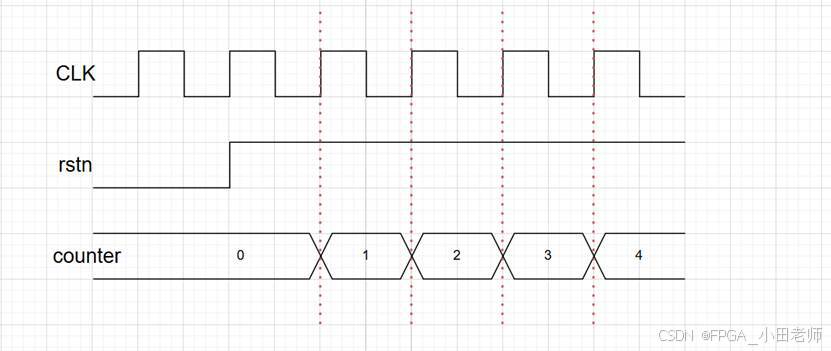

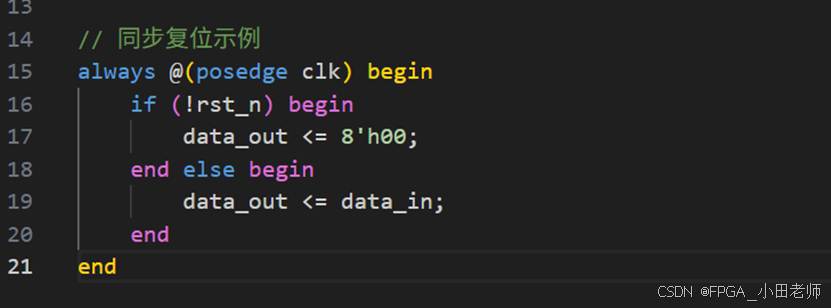

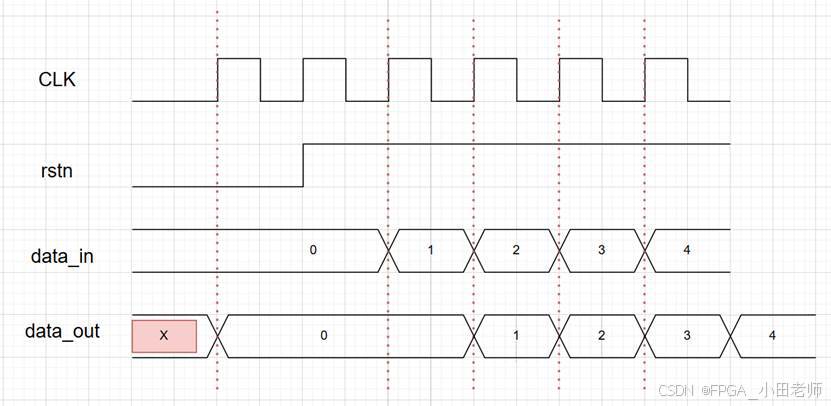

2.1 同步复位:

- 复位信号仅在时钟有效边沿生效

- 避免复位毛刺引起的异常

- 需要时钟信号才能完成复位

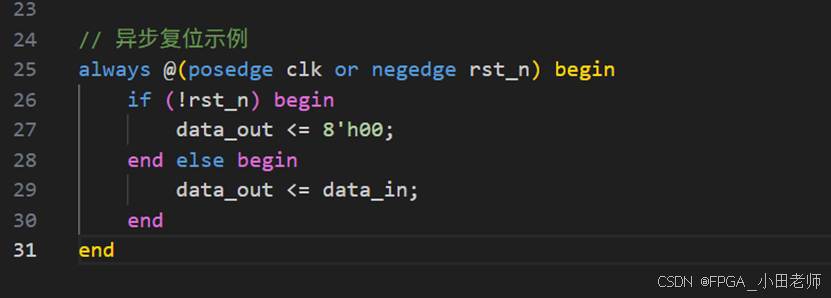

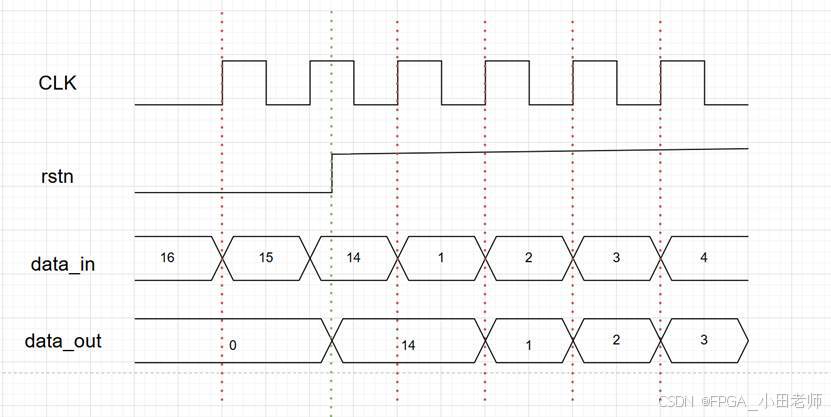

2.2 异步复位:

- 复位信号立即生效,不受时钟控制

- 响应速度快,确保立即进入已知状态

- 需要注意复位释放时的时序问题

3 复位策略与最佳实践

3.1 全局复位设计

- 使用专门的复位引脚

- 确保复位脉冲足够宽

- 考虑上电复位时序

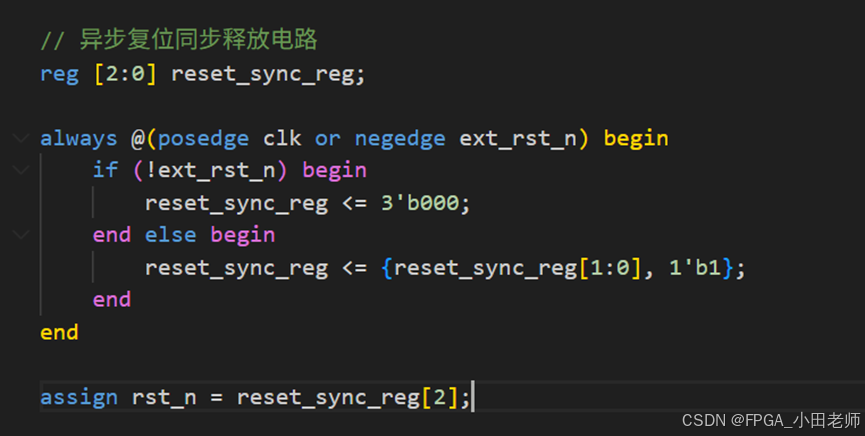

3.2 复位同步化技术

异步复位同步释放,结合两种复位的优点:

四 常见问题与调试技巧

1 时序违例

- 检查时钟约束是否合理

- 分析关键路径逻辑

2 复位相关问题

- 复位信号抖动

- 复位释放时机不当

五 工程实践建议

时钟设计原则

- 明确时钟架构

- 合理约束时钟关系

- 避免时钟毛刺

复位设计原则

- 统一复位策略

- 确保复位可靠性

- 测试复位边界情况

总结

时钟与复位是FPGA设计中最基础却最重要的概念。正确的时钟设计确保了系统的性能,可靠的复位机制保证了系统的稳定性。掌握这些基础知识,将为后续复杂系统的设计打下坚实基础。

在实际工程中,建议根据具体需求选择合适的时钟复位方案,并通过充分的仿真和测试验证其正确性。良好的时钟复位设计是FPGA项目成功的重要保障。

本文由「射频&FPGA&PCB硬件技术研习社」原创,关注我们获取更多FPGA与硬件设计干货分享。

1352

1352

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?