【致读者】

理论是骨架,实践是血肉。为了帮助大家更好地将AXI4-FULL理论应用于实际:我创建了一个【FPGA硬件技术交流群】,群内聚焦:

FPGA技术分享

实战问题讨论与答疑

行业动态与职业发展交流

我们致力于打造一个共同攻克FPGA开发中各种“疑难杂症”的优质社区。若您对本专题感兴趣,欢迎私信我 “FPGA” 加入群聊

一 引言:从“道路”到“高速公路”

熟悉AXI4总线家族的同学都知道,其构建了FPGA系统内部的“交通网络”。其中,AXI4-FULL 协议,就是我们这个网络中的 “双向八车道高速公路” 。它专为高带宽、低延迟的存储器映射数据传输而设计,是连接CPU、DMA、DDR控制器等高性能单元的首选。

本文将参考《IHI0022C_amba_axi_v2_0_protocol_spec》深入AXI4-FULL的每一个细节,带你彻底掌握这把开启高性能FPGA系统设计的钥匙。

需要《IHI0022C_amba_axi_v2_0_protocol_spec》源文件的可以后台私信我。

二 AXI4-FULL的定位与核心特性

首先,我们必须明确:通常所说的AXI4,指的就是AXI4-FULL。它是AXI4-Lite的完全体,增加了实现高带宽所需的所有高级特性。

其核心特性可以概括为以下几点:

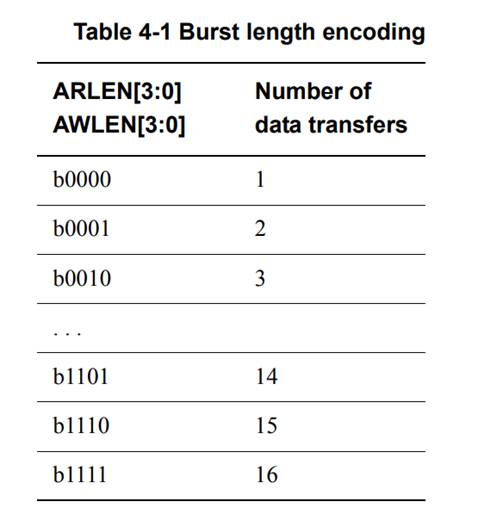

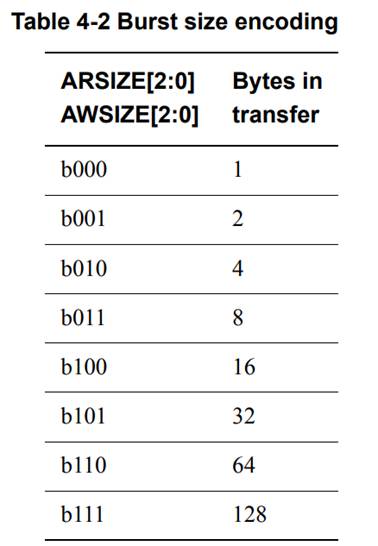

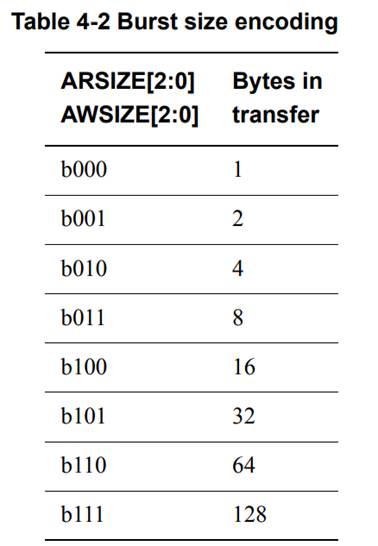

- 支持突发传输:核心特性,允许一次地址握手后传输大量数据(一次握手传输数据量:2^AxSIZE * (AxLEN+1) 个 Byte)。

- 独立的读写通道:读和写拥有完全独立的地址、数据通道,可以并行操作。

- 精密的写响应通道:为每次写事务提供明确的成功/失败状态回复。

- 强大的系统特性:支持包裹传输、窄传输、非对齐传输、原子操作、存储类型等,以适应复杂的系统需求。

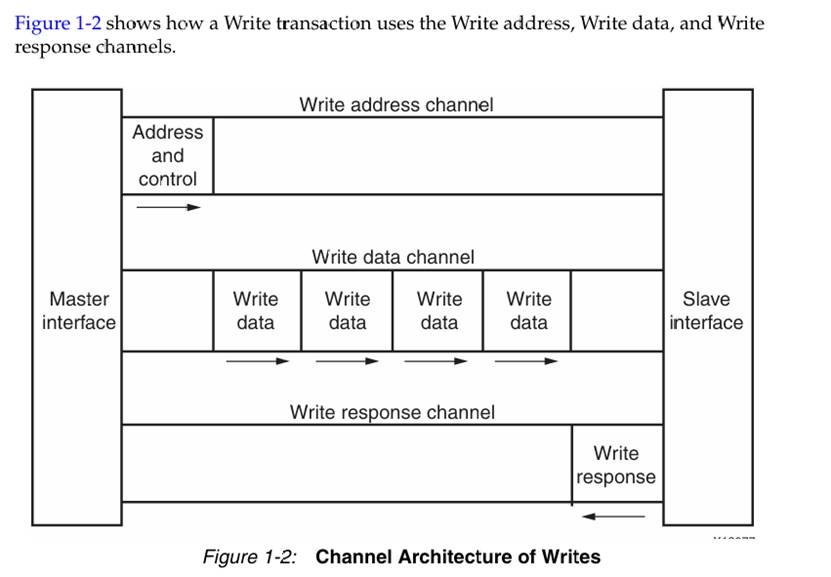

为了更直观地理解其架构,我们通过下图来审视AXI4-FULL的完整通道结构:

上图清晰地展示了AXI4-FULL的5个独立通道及其交互关系。接下来,我们将深入每个通道的细节。

三 AXI4-FULL通道深度剖析

1. 全局信号

- ACLK:全局时钟,所有信号在此时钟上升沿采样。

- ARESETn:全局复位,低有效。

2. 写通道

AXI4_FULL的写通道如下图所示,可以看出主要包括写地址通道、写数据通道、和写响应通道。

2.1 写地址通道

此通道用于主设备向从设备发送本次写操作的地址信息。

|

信号 |

方向 |

描述 |

|

AWID |

M -> S |

写地址ID,用于区分不同的事务流。 |

|

AWADDR |

M -> S |

写地址的起始字节地址。 |

|

AWLEN |

M -> S |

突发长度。AWLEN = N 表示突发 N+1 个数据传输。 |

|

AWSIZE |

M -> S |

每次传输的字节数(如 3'b010 表示 2^AWSIZE即4字节)。 |

|

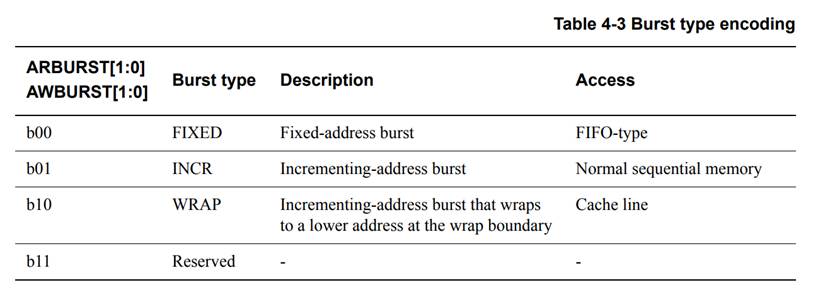

AWBURST |

M -> S |

突发类型:00固定地址,01递增突发,10回环突发。 |

|

AWLOCK |

M -> S |

锁定的原子访问,通常不使用。 |

|

AWCACHE |

M -> S |

存储类型,指示事务的可缓存性、缓冲性等。 |

|

AWPROT |

M -> S |

访问保护级别,用于特权级和安全性检查。 |

|

AWQOS |

M -> S |

服务质量标识,用于优先级仲裁。 |

|

AWREGION |

M -> S |

区域标识,用于逻辑分区。 |

|

AWUSER |

M -> S |

用户自定义信号。 |

|

AWVALID |

M -> S |

地址和控制信息有效。 |

|

AWREADY |

S -> M |

从设备准备好接收地址和控制信息。 |

2.2. 写数据通道

此通道承载实际要写入的数据。

|

信号 |

方向 |

描述 |

|

WID |

M -> S |

写数据ID,应匹配AWID。但在实践中常被省略,依赖顺序。 |

|

WDATA |

M -> S |

写数据。 |

|

WSTRB |

M -> S |

字节线选通。WSTRB[n] 对应 WDATA[8n+7:8n],为1时表示该字节有效。 |

|

WLAST |

M -> S |

必须拉高,指示这是本次突发的最后一个数据。 |

|

WUSER |

M -> S |

用户自定义信号。 |

|

WVALID |

M -> S |

写数据和选通有效。 |

|

WREADY |

S -> M |

从设备准备好接收数据。 |

2.3. 写响应通道

从设备通过此通道告知主设备写事务的完成状态。

|

信号 |

方向 |

描述 |

|

BID |

S -> M |

响应ID,与AWID匹配。 |

|

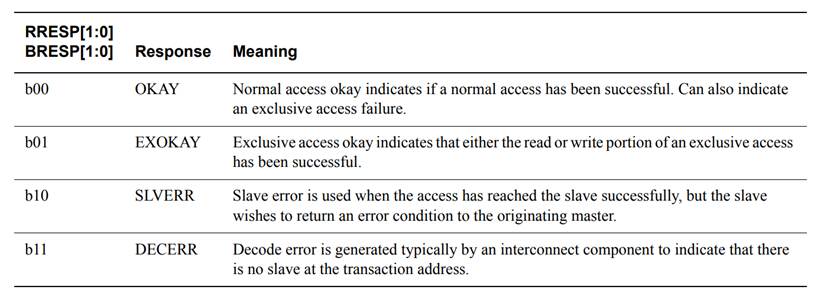

BRESP |

S -> M |

写响应:00 OKAY, 01 EXOKAY, 10 SLVERR, 11 DECERR。 |

|

BUSER |

S -> M |

用户自定义信号。 |

|

BVALID |

S -> M |

写响应有效。 |

|

BREADY |

M -> S |

主设备准备好接收响应。 |

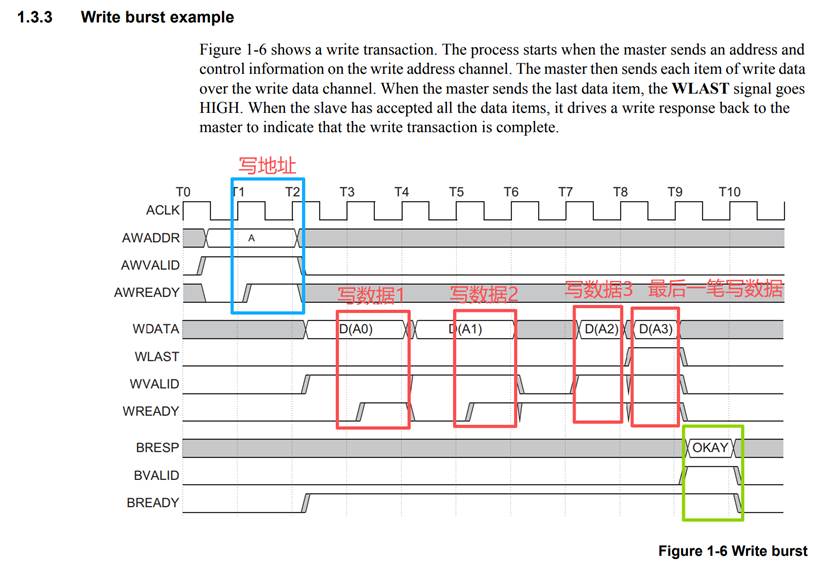

2.4 写通道时序详解

这是一次写4个数据的写通道时序。

当AWVALID和AWREAY同时为高的时候,写地址AWADDR有效,此外对应的AWSIZE、AWLEN等信号均是此时有效,传输4笔数据,对应的AWLEN应该是3,图中虽然没有显示,但是大家需要知道有这个信号的存在;

当WVALID和WREADY同时为高时,写数据WDATA有效,此次突发传输4个数据,故最后一笔数对应的WLAST为高,标识为最后一笔数据完成,当WDATA为32bit位宽时,对应的AWSIZE应该是2,图中虽然没有显示,但是大家需要知道有这个信号的存在;

最后是应答通道,当BVALID和BREADY同时为0是,BRESP有效。

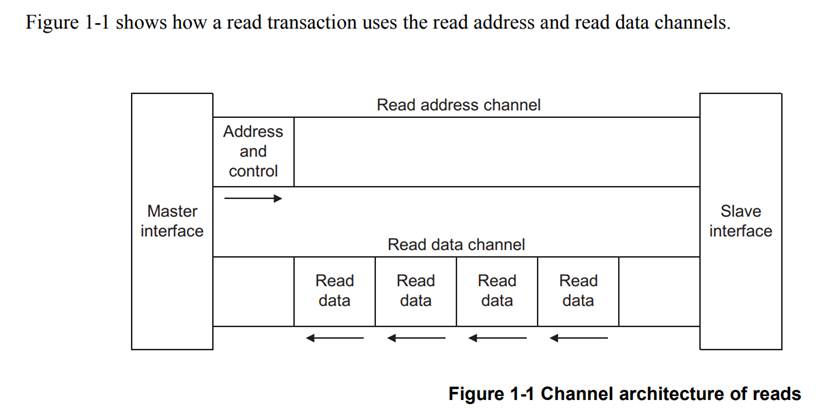

3. 读通道

AXI4_FULL的读通道如下图所示,可以看出主要包括读地址通道、读数据应答通道。

3.1. 读地址通道

与写地址通道类似,用于发起读事务。

|

信号 |

方向 |

描述 |

|

ARID |

M -> S |

读地址ID。 |

|

ARADDR |

M -> S |

读地址的起始字节地址。 |

|

ARLEN |

M -> S |

读突发长度。 |

|

ARSIZE |

M -> S |

每次读取的字节数。 |

|

ARBURST |

M -> S |

读突发类型。 |

|

... |

... |

其他信号与写地址通道类似。 |

|

ARVALID |

M -> S |

读地址和控制信息有效。 |

|

ARREADY |

S -> M |

从设备准备好接收读地址。 |

3.2. 读数据应答通道

从设备通过此通道返回主设备所请求的数据。

|

信号 |

方向 |

描述 |

|

RID |

S -> M |

读数据ID,与ARID匹配。 |

|

RDATA |

S -> M |

读出的数据。 |

|

RRESP |

S -> M |

读响应(同BRESP)。 |

|

RLAST |

S -> M |

指示这是最后一个读数据。 |

|

RUSER |

S -> M |

用户自定义信号。 |

|

RVALID |

S -> M |

读数据有效。 |

|

RREADY |

M -> S |

主设备准备好接收读数据。 |

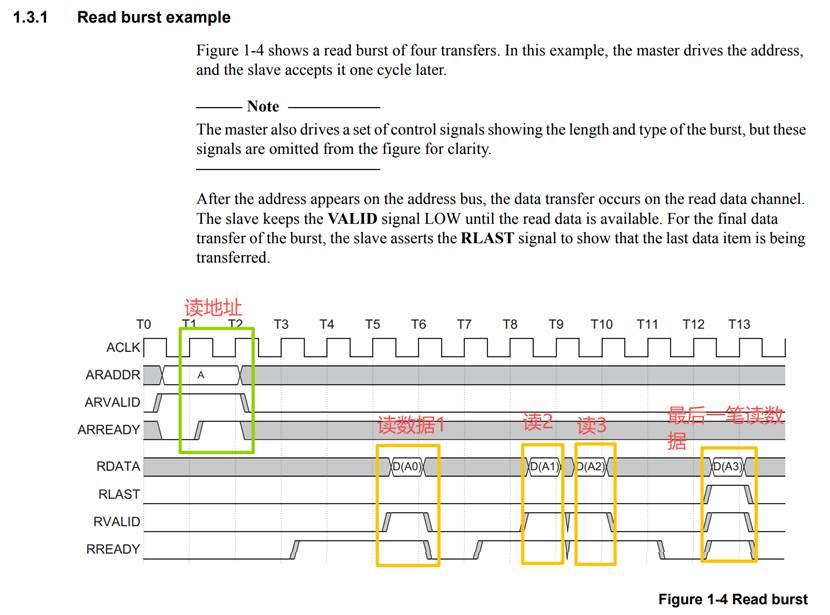

3.3 读通道时序详解

这是一次读4个数据的读通道时序。

当ARVALID和ARREAY同时为高的时候,读地址ARADDR有效,此外对应的ARSIZE、ARLEN等信号均是此时有效,读4笔数据,对应的ARLEN应该是3,图中虽然没有显示,但是大家需要知道有这个信号的存在;

当RVALID和RREADY同时为高时,读数据RDATA有效,此次突发传输4个数据,故最后一笔数对应的RLAST为高,标识为最后一笔数据完成,当RDATA为32bit位宽时,对应的ARSIZE应该是2,图中虽然没有显示,但是大家需要知道有这个信号的存在;

四 高级特性详解

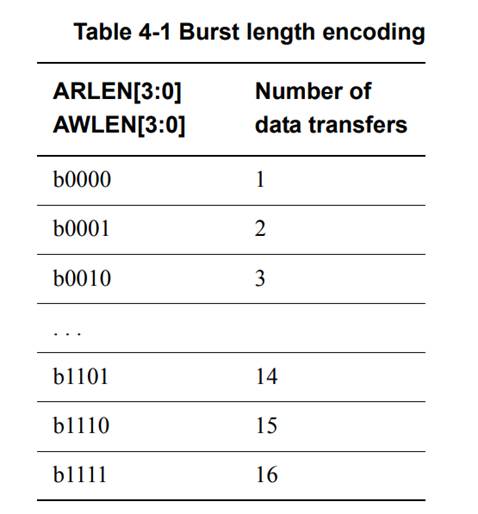

1. 突发传输(Burst trans)

这是AXI4-FULL的灵魂。AxLEN、AxSIZE、AxADDR和AxBURST共同定义了一次突发传输的所有行为。

- INCR(递增):最常用的模式,地址根据AxSIZE在每个周期后递增。

- FIXED(固定):所有数据传输到同一个地址,适用于FIFO或外设寄存器访问。

- WRAP(回环):地址在达到边界后回环,用于缓存行填充。

2. 窄传输

当数据总线位宽(如128bit)大于每次传输的字节数(AxSIZE,如4字节)时,就是窄传输。主设备使用 WSTRB 信号来指示哪些字节是有效的。这使得主设备可以高效地使用宽数据总线来更新小数据。

3. 非对齐传输

一次传输的起始地址不是本次传输字节数的整数倍,即为非对齐传输。AXI4-FULL硬件自动处理此类传输,对软件透明,极大简化了编程模型。

4. 存储类型

AxCACHE信号极为重要,它定义了内存的属性,直接影响系统性能和一致性。

- 可缓冲:事务可以通过中间缓存。

- 可缓存:事务可以被分配到缓存。

- 读分配:在缓存未命中时,是否应进行缓存行填充。

- 写分配:在写未命中时,是否应进行缓存行填充。

总结

AXI4-FULL的精髓在于其“解耦”与“并行”的架构思想:

- 通道解耦:独立的读写通道使得读和写可以同时进行,互不阻塞。

- 地址/数据解耦:在一个通道内,地址和数据也可以并行传输。

- 基于握手的流控:VALID/READY机制确保了数据传输的可靠性,不受频率差异影响。

掌握AXI4-FULL,意味着你能够设计、连接和验证FPGA系统中的高性能数据通路。它是你驾驭基于Zynq/Gigerbyte的SoC、实现高速数据采集、图像处理等应用的基石。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?