《FPGA DDR3权威指南》系列导航

《FPGA DDR3权威指南》系列旨在从零到一带你彻底掌握DDR3设计精髓,关注我,你可以:

- 系统学习,避免知识碎片化。

- 获得更新提醒,不错过任何一篇干货

本篇是该系列的第二篇内容

上一篇:FPGA DDR3实战(一):详解Xilinx MIG IP核配置_mig ip核轻松配置ddr3-优快云博客

下一篇:FPGA DDR3实战(三):使用AXI VIP作为主设备进行DDR3工程级仿真-优快云博客

一:引言

在上一篇《FPGA DDR3实战(一):详解Xilinx MIG IP核配置》中,我们成功配置并生成了一个MIG IP核。然而,直接将未经充分验证的逻辑下载到板卡上是极其危险的——时序违例、初始化失败等问题轻则导致功能异常,重则损坏硬件。

本篇将为你解锁FPGA开发的“安全区”:通过仿真,在不依赖硬件的情况下,深入观察MIG IP核的初始化过程、读写时序,并验证用户逻辑的正确性。 我们将使用Vivado自带的仿真工具,一步步搭建一个DDR3仿真环境。

二、仿真环境搭建:获取DDR3仿真模型

这是仿真成功的第一步!

1 .Open IP Example Design

按照之前的配置生成好IP核之后,右键点击Open IP Example Design(我这个是在BlockDesign中添加的IP核,所以界面是这样子的,大家直接使用IP Catalog添加的,右键打开也是一样的,但是使用DDR3还是建议大家在BlockDesign中进行添加,因为AXI总线如果自己去接信号比较麻烦,放在BlockDesign里面直接接线会比较方便一些)

之后会打开这样一个工程,这个是xilinx自带的一个仿真工程

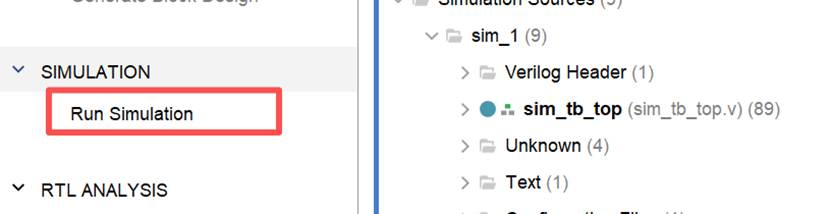

2 Run Simulation

点击Run Simulation我们可以跑一下

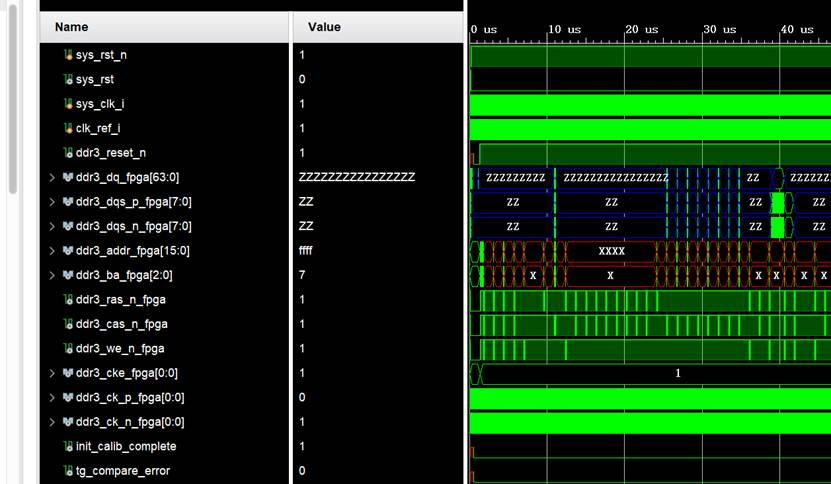

会打开如下仿真界面

三:关键时序分析

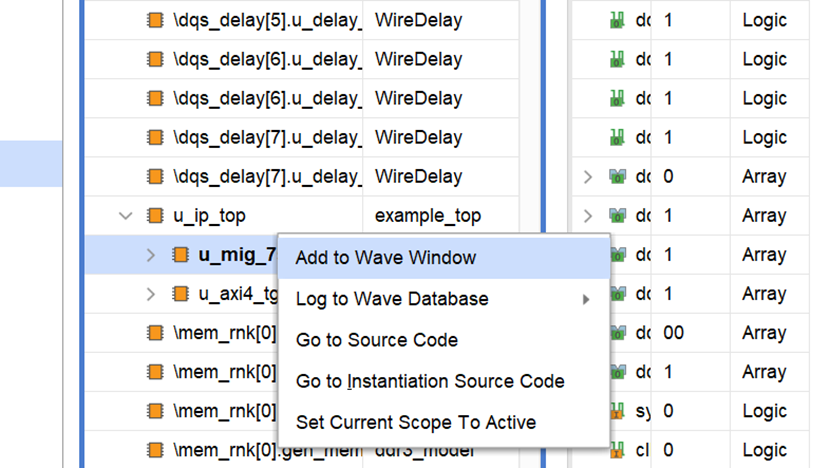

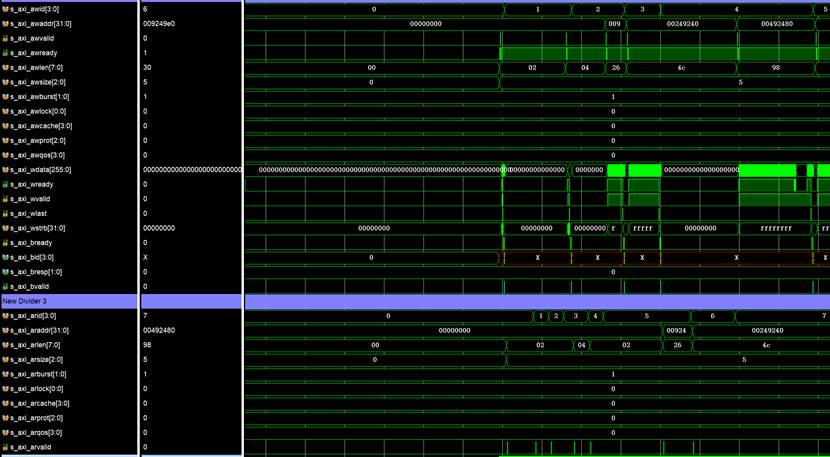

我们从左侧,选择我们要看的IP核,右键 Add to Wave Window,就可以打开mig的时序

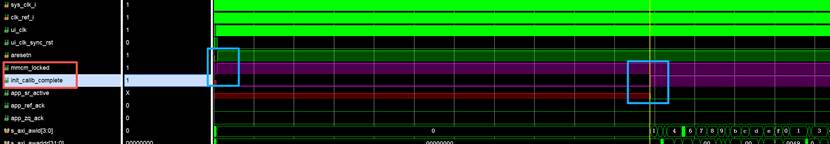

如下图所示,我们可以看到几个关键信号

Mmcm_locked:拉高说明时钟输入正常

Init_calib_Complete:拉高说明DDR初始化已经完成,可以进行正常的数据传输。

这也是咱们硬件调试的时候两个关键信号,最好可以直接接到一个LED灯上,显示DDR的状态。

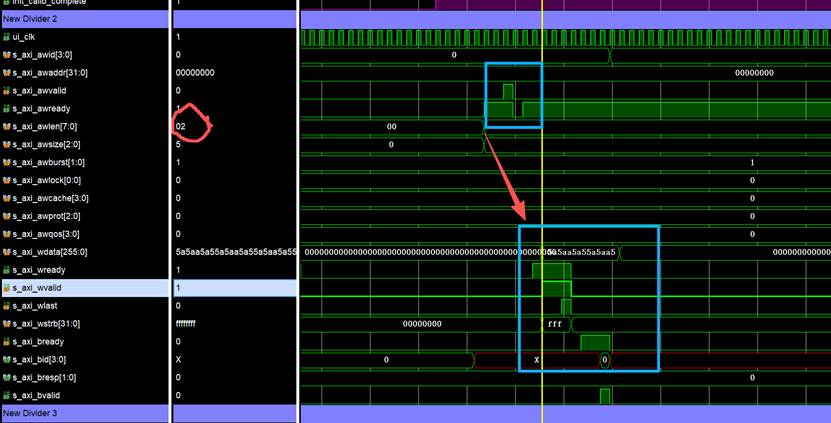

当DDR初始化完成之后,我们在AXI4总线上可以看到如下数据传输。

展开之后可以看到,第一笔是在0x0000_0000地址上写了3笔0x5a5aa5a5………的数据,为什么这里写的是3笔?因为这是burst传输,awlen配置为2,所以传输数据为awlen+1个

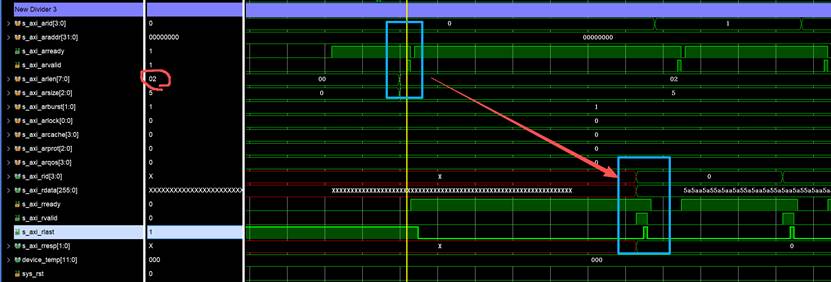

写完之后,接着就读了一次地址0x0000_0000, 读出来的值也是0x5a5aa5a5………,读写一致,即此地址的DDR3读写正常

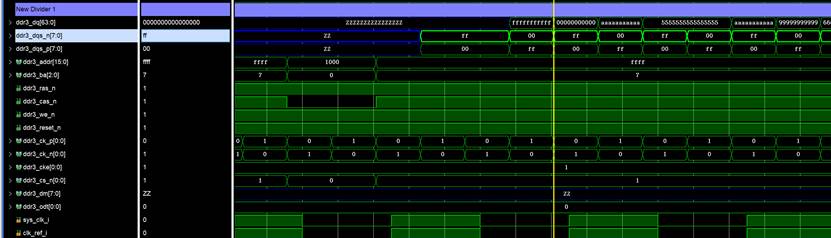

其实初学者理解到此就可以的,只要保证通过AXI4写入的DDR3的数据与从DDR3读取的数据一致就可以了,如果要深究可以看到,如下,通过AXI4写入DDR3的数据转成了如下总线形式,传给了硬件的DDR3颗粒,这里如果有需要详细了解的也可以给我留言,但其实一般也不用了解这些。

【精髓】:关键仿真波形观测要点

在仿真波形窗口中,添加并观察以下关键信号组,这能让你清晰地把握整个数据传输过程:

-

初始化状态:

ui_clk,ui_clk_sync_rst,init_calib_complete。 -

AXI写通道:

S_AXI_AW*,S_AXI_W*,S_AXI_B*。重点观察VALID/READY握手。 -

AXI读通道:

S_AXI_AR*,S_AXI_R*。重点观察VALID/READY握手以及RLAST信号。 -

DDR3颗粒接口:

ddr3_dq,ddr3_addr,ddr3_ba等,可以直观看到底层命令和数据的流动。 -

仿真速度:DDR3仿真模型非常复杂,仿真速度很慢,大家务必耐心等待。

总结

通过本篇的学习,你已经掌握了在“软环境”中验证DDR3的基础功能。但xilinx自带仿真我们也可以看出,写地址其实是随机的,很难去覆盖所有的地址空间,FPGA DDR3实战(三):使用AXI VIP作为主设备进行DDR3工程级仿真会给大家再讲到如果使用AXI_VIP搭建DDR3仿真环境,这样的仿真就会更贴近于咱们实际工程使用,欢迎大家在评论区留言,多多点赞关注,您的互动是我前进的动力!!!

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?