《FPGA DDR3权威指南》系列导航

《FPGA DDR3权威指南》系列旨在从零到一带你彻底掌握DDR3设计精髓,关注我,你可以:

- 系统学习,避免知识碎片化。

- 获得更新提醒,不错过任何一篇干货

本篇是该系列的第一篇内容

下一篇:FPGA DDR3实战(二):手把手教你仿真DDR3(MIG IP核)_fpga怎么模拟ddr3-优快云博客

一:引言 我们为什么需要使用DDR3

在我们追逐更高、更快、更强的FPGA系统时,总会遇到一个无法回避的“内存墙”。

如果你试图使用FPGA内部的Block RAM来解决,你会发现它的容量如同一个小水杯,试图去接住打开的水龙头——瞬间就会满溢而出。而片外传统的SRAM,虽然速度快,但容量小、价格昂贵,性价比极低。

于是,我们迎来了今天的主角:DDR3 SDRAM。

它并非最新的技术,但无疑是当前在成本、容量、带宽和可靠性上最平衡的选择。你可以把它理解为一个在FPGA片外的、“海量”且“廉价”的“数据中转仓库”。

-

【海量】:以GB为单位的容量,轻松容纳海量数据,让FPGA得以处理复杂的任务。

-

【高速】 通过双倍数据速率 等技术,提供远超普通SDRAM的传输带宽,满足高速数据吞吐的需求。

-

【廉价】:技术成熟,产业链完善,单位容量的成本极具竞争力。

然而,驾驭这片“海洋”并非易事。 DDR3的复杂性远非简单的UART或SPI可比:

-

它需要复杂的初始化序列。

-

它通过命令、地址总线进行复用访问,时序关系极其严格。

-

它依赖MIG这样的专用IP核来管理底层物理层接口。

因此,本系列文章的目的,就是作为你的“领航员”,带你穿越DDR3开发的迷雾。我们将从Xilinx MIG IP核的深度解读开始,一步步教你如何搭建测试环境、编写读写控制器,并最终压榨出DDR3的极致性能。

准备好了吗?让我们开始这趟深入DDR3核心的旅程。

二:MIG IP核配置向导逐页精讲

本次我们以xillinx的A7200t作为硬件平台,进行MIG ip核配置

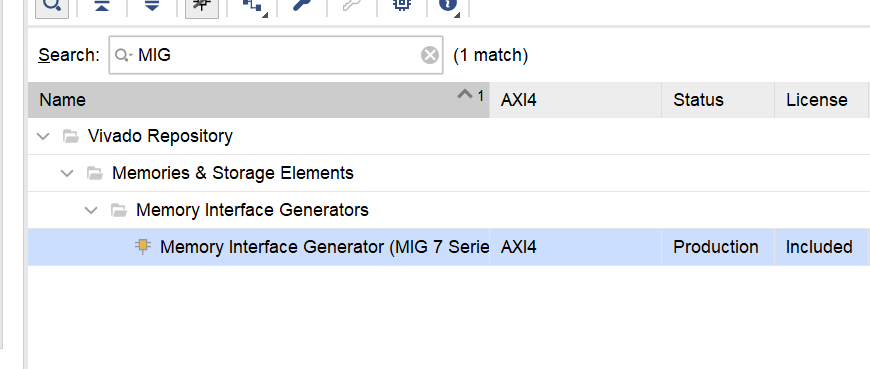

1 打开IP Catalog,搜索MIG

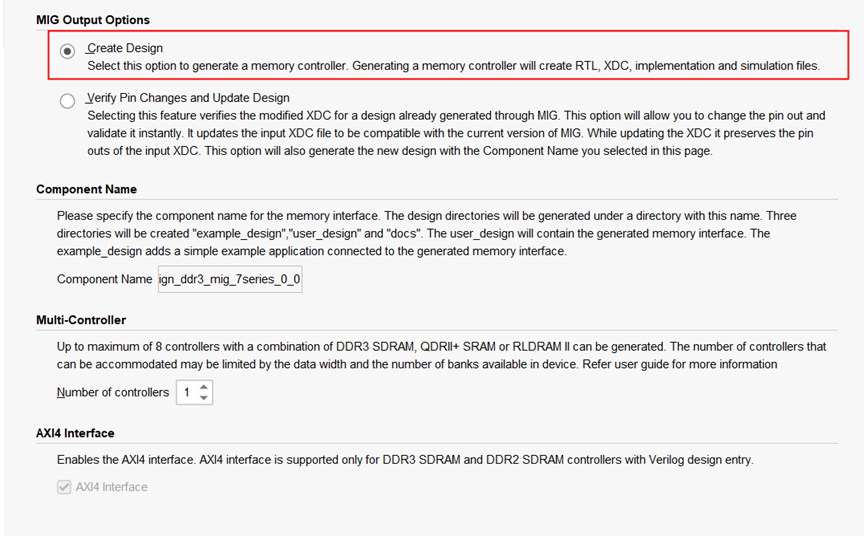

2 MIG ip核,点击下一步,选择Create Design

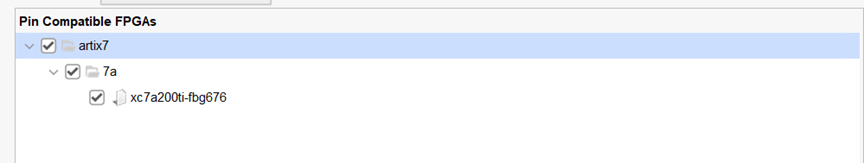

3 选择FPGA型号

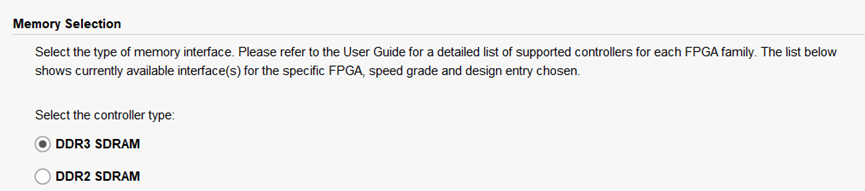

4 选择DDR3

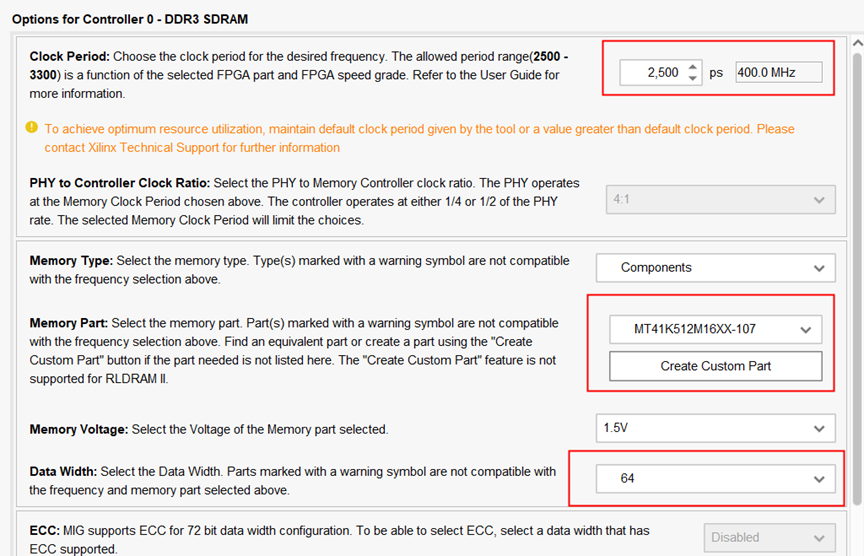

5 选择DDR3的工作频率,Memory的型号,此处需要注意的是,我们内部是没有MT41K512M16这个型号的,需要使用Create Custom Part进行创建,我这里使用的方法是,在MT41K256M16XX-107的基础上,将Row address修改为16即可,选择数据位宽为64bit。

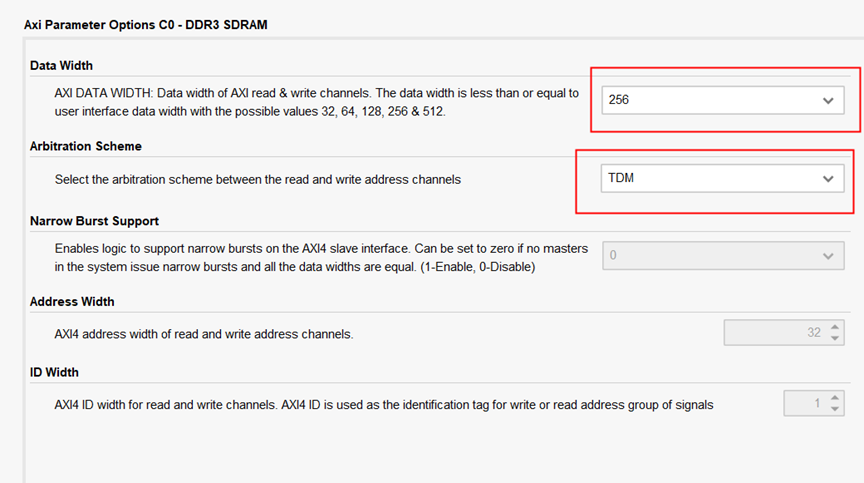

6 配置AXI接口的数据宽度

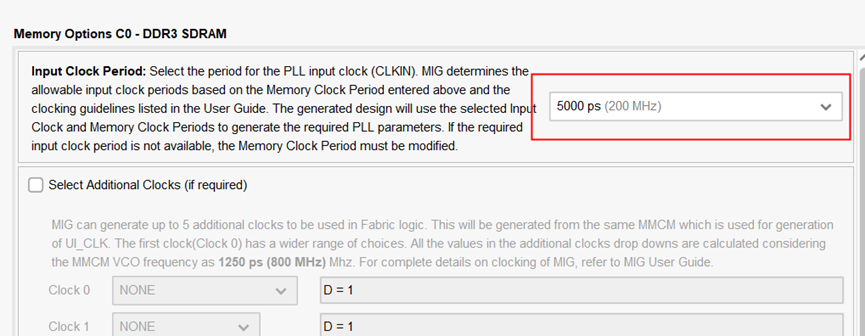

7 配置输入时钟频率,这个是输入MIG核的频率,IP核内部会自己调用PLL来产生自己的工作时钟,此处设置200MHz

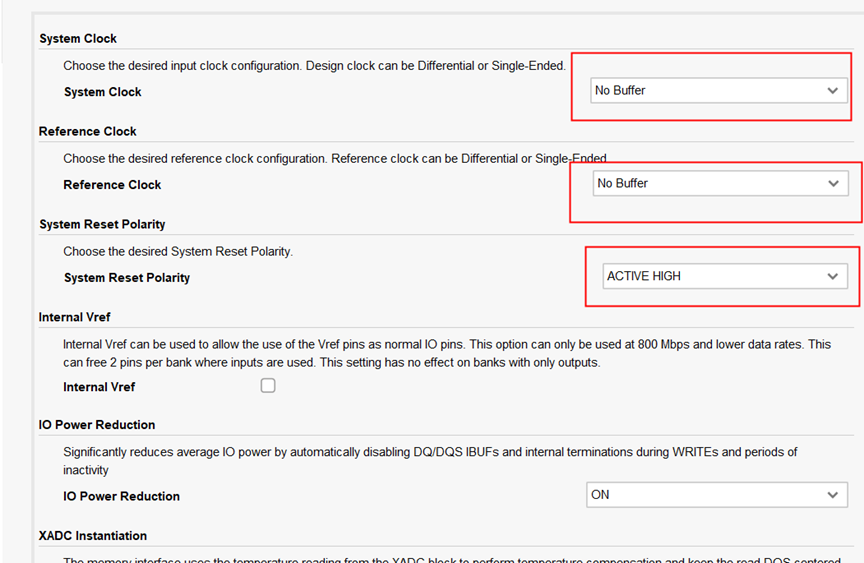

8 设置系统时钟、参考时钟、复位信号的属性

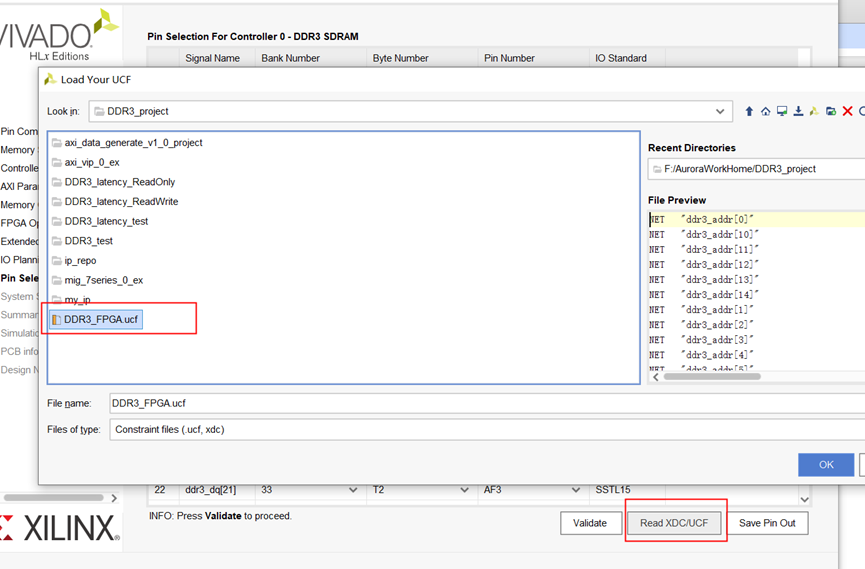

9 引脚选择固定引脚,点击Read XDC/UDF,导入提前准备好的引脚约束文件,引脚约束按照原理图进行约束,导入之后点击Validate

10 直点击next知道最后完成Generate即可生成本次使用的ddr3 ip。

三 :MIG IP核 核心信号解读(AXI4接口版本)

当你在MIG IP核的配置中选择“AXI4”作为用户接口时,IP核会化身为一个AXI从设备,而你的用户逻辑则成为AXI主设备。这意味着,你将使用行业标准的AXI4协议来与DDR3内存通信,这大大简化了与其它支持AXI4的IP核(如PCIE、DMA控制器等)的集成。

AXI4协议的核心是通道架构和握手机制。我们将信号组按照通道进行划分。

1. 全局信号与初始化状态

-

ui_clk(输出)-

功能:所有AXI4信号都必须与此时钟同步。

-

-

ui_clk_sync_rst(输出)-

功能:与

ui_clk同步的复位信号,高有效。用于复位你的AXI主控逻辑。

-

-

init_calib_complete(输出)-

功能:生命线信号。在DDR3初始化校准完成之前,AXI总线上的任何事务都会被忽略。你的设计必须等待此信号拉高。

-

2. 写地址通道 - 发起一次写操作的“目的地”

主设备通过此通道告诉从设备“我要往哪里写”。

-

S_AXI_AWID(输入)-

功能:写地址ID,用于区分多个同时进行的事务。在简单应用中可设固定值。

-

-

S_AXI_AWADDR(输入)-

功能:起始字节地址。这是与原生接口的关键区别之一,AXI使用字节寻址。

-

-

S_AXI_AWLEN(输入)-

功能:突发传输的长度。

AWLEN = N表示本次突发传输 N+1 个数据周期。

-

-

S_AXI_AWSIZE(输入)-

功能:每次传输的字节数。例如,3‘b101 表示32字节(256bit),必须与你的数据位宽匹配。

-

-

S_AXI_AWBURST(输入)-

功能:突发类型。通常使用

2‘b01(INCR,递增模式)。

-

-

S_AXI_AWVALID(输入)-

功能:主设备信号,表示地址和控制信息有效。

-

-

S_AXI_AWREADY(输出)-

功能:从设备信号,表示已准备好接收地址信息。

-

握手: 一次成功的地址传输发生在 S_AXI_AWVALID 和 S_AXI_AWREADY 同时为高的时钟上升沿。

3. 写数据通道 - 输送要写入的“货物”

-

S_AXI_WDATA(输入)-

功能:写数据。

-

-

S_AXI_WSTRB(输入)-

功能:字节选通信号,用于指定

WDATA的哪些字节是有效的。WSTRB[n]对应WDATA[(8*n)+7 : (8*n)]。

-

-

S_AXI_WLAST(输入)-

功能:必须拉高,以指示这是本次突发传输的最后一个数据。

-

-

S_AXI_WVALID(输入)-

功能:主设备信号,表示写数据和WLAST有效。

-

-

S_AXI_WREADY(输出)-

功能:从设备信号,表示已准备好接收数据。

-

握手: 一次成功的数据传输发生在 S_AXI_WVALID 和 S_AXI_WREADY 同时为高的时钟上升沿。

4. 写响应通道 - 确认“货物”已送达

-

S_AXI_BID(输出)-

功能:响应ID,与写地址的AWID对应。

-

-

S_AXI_BRESP(输出)-

功能:写事务状态。

2‘b00(OKAY)表示成功。

-

-

S_AXI_BVALID(输出)-

功能:从设备信号,表示写响应信息有效。

-

-

S_AXI_BREADY(输入)-

功能:主设备信号,表示已准备好接收响应。

-

握手: 一次成功的响应接收发生在 S_AXI_BVALID 和 S_AXI_BREADY 同时为高的时钟上升沿。

5. 读地址通道 - 发起一次读操作

-

S_AXI_ARID,S_AXI_ARADDR,S_AXI_ARLEN,S_AXI_ARSIZE,S_AXI_ARBURST-

功能:与写地址通道类似,用于发起读请求。

-

-

S_AXI_ARVALID(输入) -

S_AXI_ARREADY(输出)-

功能:握手信号,逻辑与写地址通道完全相同。

-

6. 读数据通道 - 返回请求的“数据”

-

S_AXI_RID(输出)-

功能:读数据ID,与读地址的ARID对应。

-

-

S_AXI_RDATA(输出)-

功能:读出的数据。

-

-

S_AXI_RRESP(输出)-

功能:读事务状态。

2’b00(OKAY)表示成功。

-

-

S_AXI_RLAST(输出)-

功能:从设备信号,指示这是本次突发传输的最后一个数据。

-

-

S_AXI_RVALID(输出)-

功能:从设备信号,表示读数据有效。

-

-

S_AXI_RREADY(输入)-

功能:主设备信号,表示已准备好接收数据。

-

握手: 一次成功的读数据接收发生在 S_AXI_RVALID 和 S_AXI_RREADY 同时为高的时钟上升沿。

【精髓】:AXI4接口的优势与设计要点

-

去耦合与高效率:

与原生接口不同,AXI4的五个通道是独立的。这意味着你可以先发送读地址,然后在数据返回之前,立刻发送下一个写地址。这种乱序处理能力极大地提高了总线利用率和系统并行性。 -

简化设计:

你不再需要像处理原生接口那样,亲自管理app_rdy和app_wdf_rdy之间复杂的时序关系。AXI4的VALID/READY握手机制在每个通道内都是统一的,逻辑更清晰。 -

突发传输是核心:

AXI4是为突发传输而设计的。ARLEN/AWLEN信号允许你通过一次地址握手,完成大量数据的连续传输。这对于发挥DDR3的带宽性能至关重要。

总结:

本节我们完成了IP核的创建,“现在内存已经准备好,但我们还不知道如何与它正确通信,更不知道它的实际性能如何。

在下一节FPGA DDR3实战(二):手把手教你仿真DDR3(MIG IP核),我们将利用这些知识,向DDR3写入一个测试Pattern并读出验证,大家点赞关注多多互动!谢谢大家

5165

5165

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?