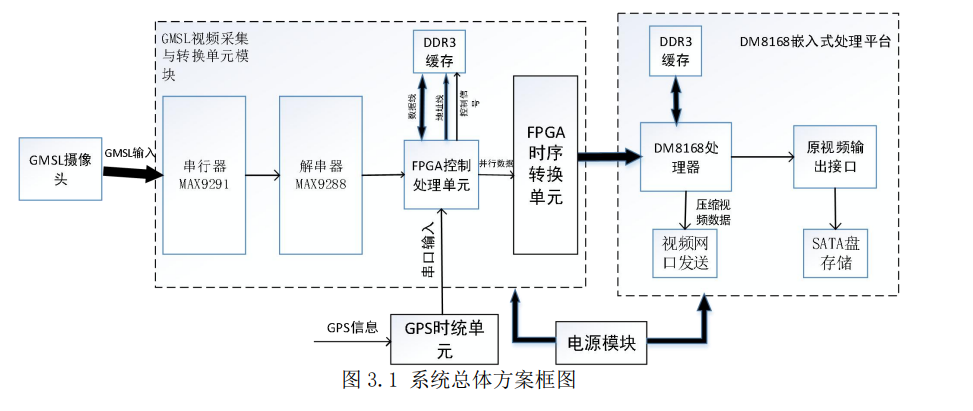

3.1 系统总体方案及工作原理 3.1.1 系统总体方案 基于 GMSL 的车载视频采集与存储系统总体方案框图如下图 3.1 所示,主要由 GMSL 视频采集与转换单元、DM8168 嵌入式数字视频采集单元、GPS 时统单元和电 源模块共四个功能模块构成。 其中,系统核心处理平台采用 FPGA+DM8168 架构,整个硬件系统由 FPGA 处理 器、DM8168 异构多核 SoC 片上系统、外围接口电路和各功能模块电路组成。 图 3.1 系统总体方案框图 各功能模块的主要功能如下: (1)GMSL 视频采集传输链路单元 GMSL 视频采集传输链路单元模块主要包括 GMSL 串行器、GMSL 解串器、FPGA 控制器、DDR3 缓存单元和 FPGA 接口时序转换模块等子模块。其主要功能是将 GMSL 相机采集的视频数据通过 GMSL 链路传输,由 FPGA 对视频数据进行时标叠加,然后 通过FPGA接口时序转换模块完成对视频数据接口转换方便后端处理器对视频信号数 据进行采集处理。 (2)DM8168 嵌入式数字视频采集单元 DM8168 嵌入式数字视频采集单元模块主要包括 DM8168 处理器、SATA 盘存储 模块、网口发送模块和 DDR3 缓存单元。DM8168 处理器负责对 FPGA 输出的数字视 频信号进行采集,然后对视频数据作图像处理。SATA 存储模块负责将原始视频数据 存储到 SATA 电子盘。网口发送模块主要是利用千兆以太网将 DM8168 处理器压缩编码后的视频数据发送到上位机。 (3)GPS 时统单元 GPS 时统单元模块主要是将上位机传输来的标准时间模码信息通过串口发送到 FPGA 控制器,FPGA 控制器再将时间模码叠加到视频图像上,完成视频图像时标叠 加。 (4)电源模块 其中主要有三路电源芯片进行电源分流,分别对整个系统的各个模块电路进行供 电。 3.1.2 系统工作原理 GMSL 相机获取原始模拟视频图像经过图像处理模块转换成数字视频信号通过 GMSL 接口传输给 MAX9291 串行器。串行器对并行视频信号数据进行串行化,串行 数据通过双绞线传输。然后解串器对串行数据解串得到并行的原始数据,FPGA 对解 串后的视频数据进行时标叠加。叠加完时标的视频数据由 FPGA 接口时序转换模块对 视频信号数据进行接口时序转换。在视频采集单元中,解串器传输到 FPGA 的数据先 由 DDR3 缓存单元缓存,再传输给 FPGA 进行视频数据处理。这使 FPGA 处理数据更 加高效有序,不会出现数据混乱。DM8168 嵌入式处理器通过 GMPC 接口与 FPGA 模 块相连,由 FPGA 进行接口时序转换后的视频信号数据通过 GMPC 接口将视频数据 传输给 DM8168 嵌入式处理器。DM8168 处理平台对视频数据进行图像处理,然后存 储到 SATA 电子盘中,实现对视频数据的存储回放功能;另一路视频在 DM8168 处理 器中经过 H.264 压缩编码后通过网口发送到上位机。 3.2 GMSL 视频采集与转换模块设计 GMSL 车载视频采集与转换模块主要是对 GMSL 接口视频进行采集,通过 GMSL 链路传输到 FPGA 控制器进行数据处理,利用接口时序模块完成对视频数据接口的转 换。该模块主要器件有 GMSL 串行器、解串器和 FPGA 处理器。 3.2.1 FPGA 选型 FPGA 是 1980 年左右出现的一种设计非常灵活的新型可编程逻辑组合器件,用户 可以根据实现功能的需要进行编程来设计芯片内部的门阵列组合。与传统的单片机相 比,FPGA 的运算速度非常快,在视频图像处理方面它有着得独特的优势。FPGA 发 展到目前,它拥有的功能已经非常多并且很成熟,在 FPGA 的芯片里面不但集成了视 频信号高速收发器、LVDS 收发器和 PLL 模块,而且还带有嵌入式 ARM 核处理器,使得在进行项目设计时灵活性和可选择性大大提高[24]。赛灵思公司是 FPGA 芯片的研 发制造中的第一家企业,因此它在 FPGA 芯片的研发领域是世界首位。赛灵思公司根 据市场的不同需求分别推出了 4 款系列 FPGA 芯片。每一款 FPGA 都有它特定的应用 领域,Virtex 和 Kintex 系列芯片拥有逻辑资源丰富、运算速度很快,主要用于高端产 品,如航空航天方面,其余两款芯片则主要用在商业领域。 FPGA 在本文车载视频采集存储系统中主要负责驱动 GMSL 相机获取原始视频信 号、驱动视频接口、完成视频图像时标叠加、对视频数据进行接口转换、对串行器和 解串器寄存器进行配置。同时将时标叠加后的视频数据进行接口时序变换传输给 DM8168 嵌入式处理器处理。 为了满足采集板实现功能的要求,主要从以下几个方面对 FPGA 芯片进行选型, 首先是芯片的逻辑资源,FPGA 对视频数据处理需要的逻辑资源比较多,需要丰富的 逻辑单元资源。其次是逻辑时钟和 I/O 时钟速率,视频数据的处理传输属于高速信号 交互。最后片内资源的大小和 IP 核兼容也是需要考虑的。 最后决定本文车载视频采集与存储系统采集板电路采用赛灵思公司的 Sprtan6 系 列 XC6SLX75 芯片作为主控芯片,该芯片内部有大量的逻辑单元和高效集成模块,还 有四个 I/O bank 和丰富的 I/O 接口资源,并且具有 48 位加法器和高阶乘法器,可以 满足视频处理的运算速率要求,而且每个 I/O 口最高传输速率可以达到 1080M/s。综 上所述,XC6SLX75 芯片可以满足系统视频采集板的要求。 3.2.2 GMSL 串行器和解串器选型 GMSL 相机采集的视频信号由 GMSL 接口输出到串行器进行视频数据串行化。在 智能车无人驾驶平台中,需要的相机数目至少在 5 个以上,相机数目的增加使传输的 数据带宽增加,同时传输数据所需要的信号线也会成倍增加。为了解决相机数目增加 和智能化所带来的的总线带宽增加问题,以及将视频数据高精准高速率地传输到处理 器,本文系统设计采用美信公司 MAX9291 串行器和 MAX9288 解串器组合成的链路 作为 GMSL 视频传输链路。 MAX9291 串行器主要用在高分辨率汽车导航和百万级像素相机系统中,在 50 欧 姆同轴电缆或者 100 欧姆屏蔽双绞线上传输视频数据、音频和控制信号。本系统中采 用的是双绞线进行差分信号视频信号数据传输。当为 STP 输出编程时,输出幅度可编 程为 100mv 至 500mv 单端(同轴电缆)或者 100mv 至 400mv 差分(STP)。由于串 行器向后兼容任何 GMSL 解串器,因此,MAX9291 串行器可以与任何能够同轴输入 的 GMSL 解串器配对。MAX9291 串行器还具有 GMSL 输入和 HDMI1.4 输入,并且 带有集成输入均衡器、DDC 和输入端。在 104MHz 高带宽模式下支持 1920x720p/60Hz 24 位色显示,具有高达 192KHz 的采样率和 32 位采样深度,适用于高清视频数据传输。同时还具有多种数据速率以实现带宽高达 3.12Gbps 串行比特率。此外,像素时 钟在 25MHz 至 104MHz 之间可以根据系统功能需要自行设定。该芯片具有三种可编 程通道控制方式:UART、混合 UART/IIC 或具有时钟延长功能的 IIC。 MAX9288 解串器与 MAX9291 串行器配套使用,能够有效地对串行化视频数据 解码恢复成原始数据。在 UART-IIC 模式下,嵌入式控制信道的运行频率为 9.6kbps 至 1Mbps,在 IIC 至 IIC 模式下最高可达 1Mbps。µC 通过控制通道可以在任何时间编 程序列化、反序列化和外围设备寄存器,独立于视频定时,并管理 HDCP 操作。在 104MHz 高带宽模式支持 1920x720p/60Hz 显示与 24 位颜色输出。同时还具有降低电 磁干扰和屏蔽信号功能,满足严格的汽车工业要求。 综上所述,本系统选择 MAX9291 串行器和 MAX9288 解串器组合构建视频传输 链路,该视频链路符合本系统的 GMSL 视频数据传输设计要求。 3.2.3 GMSL 采集与转换模块电路设计 1)图像传感器驱动电路设计 在 IMX490 相机视频采集模块中,FPGA 内部锁相环产生的时钟通过外部 XVCLK 引脚提供给 GMSL 相机。PWDN 为低电平有效的使能引脚,当系统上电后此引脚变 为低电平,系统进入初始化状态。RESETB 为复位控制引脚,如果系统出现死机卡死 状态时,按下复位键可以使系统回到初始状态。XCLK 是相机的输入时钟,PCLK 是 像素时钟输出,由 XCLK 产生,PCLK 用于 FPGA 控制器采集视频图像数据。HREF 表示行参考信号输出,视频图像采集的像素和参考时钟进行比较,HSYNC 和 VSYNC 分别为行同步与场同步信号输出引脚,表示一帧数据的输出中断。SDA 和 SCL 为 IIC 总线的数据总线和时钟线,FPGA 通过 IIC 总线对 IMX490 内部寄存器进行初始值的 配置,使 IMX490 输出 GMSL 视频图像。IMX490 相机的驱动电路原理图如图 3.2 所 示。相机驱动电路需要的工作电压为 3.3V,该电压由电源芯片 U3 将 5V 转换得到, 以此向图像采集模块供电;摄像头的调焦模块和模拟电路的工作电压为 2.8V,该电压 由电源芯片 U2 将 3.3V 电压转换得到;摄像头图像采集核心模块的工作电压为 1.5V, 该电压由电源芯片 U1 将 2.8V 电压转换得到。

(3)GPS 时统单元 GPS 时统单元模块主要是将上位机传输来的标准时间模码信息通过串口发送到 FPGA 控制器,FPGA 控制器再将时间模码叠加到视频图像上,完成视频图像时标叠 加。 (4)电源模块 其中主要有三路电源芯片进行电源分流,分别对整个系统的各个模块电路进行供 电。 3.1.2 系统工作原理 GMSL 相机获取原始模拟视频图像经过图像处理模块转换成数字视频信号通过 GMSL 接口传输给 MAX9291 串行器。串行器对并行视频信号数据进行串行化,串行 数据通过双绞线传输。然后解串器对串行数据解串得到并行的原始数据,FPGA 对解 串后的视频数据进行时标叠加。叠加完时标的视频数据由 FPGA 接口时序转换模块对 视频信号数据进行接口时序转换。在视频采集单元中,解串器传输到 FPGA 的数据先 由 DDR3 缓存单元缓存,再传输给 FPGA 进行视频数据处理。这使 FPGA 处理数据更 加高效有序,不会出现数据混乱。DM8168 嵌入式处理器通过 GMPC 接口与 FPGA 模 块相连,由 FPGA 进行接口时序转换后的视频信号数据通过 GMPC 接口将视频数据 传输给 DM8168 嵌入式处理器。DM8168 处理平台对视频数据进行图像处理,然后存 储到 SATA 电子盘中,实现对视频数据的存储回放功能;另一路视频在 DM8168 处理 器中经过 H.264 压缩编码后通过网口发送到上位机。 3.2 GMSL 视频采集与转换模块设计 GMSL 车载视频采集与转换模块主要是对 GMSL 接口视频进行采集,通过 GMSL 链路传输到 FPGA 控制器进行数据处理,利用接口时序模块完成对视频数据接口的转 换。该模块主要器件有 GMSL 串行器、解串器和 FPGA 处理器。 3.2.1 FPGA 选型 FPGA 是 1980 年左右出现的一种设计非常灵活的新型可编程逻辑组合器件,用户 可以根据实现功能的需要进行编程来设计芯片内部的门阵列组合。与传统的单片机相 比,FPGA 的运算速度非常快,在视频图像处理方面它有着得独特的优势。FPGA 发 展到目前,它拥有的功能已经非常多并且很成熟,在 FPGA 的芯片里面不但集成了视 频信号高速收发器、LVDS 收发器和 PLL 模块,而且还带有嵌入式 ARM 核处理器,使得在进行项目设计时灵活性和可选择性大大提高[24]。赛灵思公司是 FPGA 芯片的研 发制造中的第一家企业,因此它在 FPGA 芯片的研发领域是世界首位。赛灵思公司根 据市场的不同需求分别推出了 4 款系列 FPGA 芯片。每一款 FPGA 都有它特定的应用 领域,Virtex 和 Kintex 系列芯片拥有逻辑资源丰富、运算速度很快,主要用于高端产 品,如航空航天方面,其余两款芯片则主要用在商业领域。 FPGA 在本文车载视频采集存储系统中主要负责驱动 GMSL 相机获取原始视频信 号、驱动视频接口、完成视频图像时标叠加、对视频数据进行接口转换、对串行器和 解串器寄存器进行配置。同时将时标叠加后的视频数据进行接口时序变换传输给 DM8168 嵌入式处理器处理。 为了满足采集板实现功能的要求,主要从以下几个方面对 FPGA 芯片进行选型, 首先是芯片的逻辑资源,FPGA 对视频数据处理需要的逻辑资源比较多,需要丰富的 逻辑单元资源。其次是逻辑时钟和 I/O 时钟速率,视频数据的处理传输属于高速信号 交互。最后片内资源的大小和 IP 核兼容也是需要考虑的。 最后决定本文车载视频采集与存储系统采集板电路采用赛灵思公司的 Sprtan6 系 列 XC6SLX75 芯片作为主控芯片,该芯片内部有大量的逻辑单元和高效集成模块,还 有四个 I/O bank 和丰富的 I/O 接口资源,并且具有 48 位加法器和高阶乘法器,可以 满足视频处理的运算速率要求,而且每个 I/O 口最高传输速率可以达到 1080M/s。综 上所述,XC6SLX75 芯片可以满足系统视频采集板的要求。 3.2.2 GMSL 串行器和解串器选型 GMSL 相机采集的视频信号由 GMSL 接口输出到串行器进行视频数据串行化。在 智能车无人驾驶平台中,需要的相机数目至少在 5 个以上,相机数目的增加使传输的 数据带宽增加,同时传输数据所需要的信号线也会成倍增加。为了解决相机数目增加 和智能化所带来的的总线带宽增加问题,以及将视频数据高精准高速率地传输到处理 器,本文系统设计采用美信公司 MAX9291 串行器和 MAX9288 解串器组合成的链路 作为 GMSL 视频传输链路。 MAX9291 串行器主要用在高分辨率汽车导航和百万级像素相机系统中,在 50 欧 姆同轴电缆或者 100 欧姆屏蔽双绞线上传输视频数据、音频和控制信号。本系统中采 用的是双绞线进行差分信号视频信号数据传输。当为 STP 输出编程时,输出幅度可编 程为 100mv 至 500mv 单端(同轴电缆)或者 100mv 至 400mv 差分(STP)。由于串 行器向后兼容任何 GMSL 解串器,因此,MAX9291 串行器可以与任何能够同轴输入 的 GMSL 解串器配对。MAX9291 串行器还具有 GMSL 输入和 HDMI1.4 输入,并且 带有集成输入均衡器、DDC 和输入端。在 104MHz 高带宽模式下支持 1920x720p/60Hz 24 位色显示,具有高达 192KHz 的采样率和 32 位采样深度,适用于高清视频数据传输。同时还具有多种数据速率以实现带宽高达 3.12Gbps 串行比特率。此外,像素时 钟在 25MHz 至 104MHz 之间可以根据系统功能需要自行设定。该芯片具有三种可编 程通道控制方式:UART、混合 UART/IIC 或具有时钟延长功能的 IIC。 MAX9288 解串器与 MAX9291 串行器配套使用,能够有效地对串行化视频数据 解码恢复成原始数据。在 UART-IIC 模式下,嵌入式控制信道的运行频率为 9.6kbps 至 1Mbps,在 IIC 至 IIC 模式下最高可达 1Mbps。µC 通过控制通道可以在任何时间编 程序列化、反序列化和外围设备寄存器,独立于视频定时,并管理 HDCP 操作。在 104MHz 高带宽模式支持 1920x720p/60Hz 显示与 24 位颜色输出。同时还具有降低电 磁干扰和屏蔽信号功能,满足严格的汽车工业要求。 综上所述,本系统选择 MAX9291 串行器和 MAX9288 解串器组合构建视频传输 链路,该视频链路符合本系统的 GMSL 视频数据传输设计要求。 3.2.3 GMSL 采集与转换模块电路设计 1)图像传感器驱动电路设计 在 IMX490 相机视频采集模块中,FPGA 内部锁相环产生的时钟通过外部 XVCLK 引脚提供给 GMSL 相机。PWDN 为低电平有效的使能引脚,当系统上电后此引脚变 为低电平,系统进入初始化状态。RESETB 为复位控制引脚,如果系统出现死机卡死 状态时,按下复位键可以使系统回到初始状态。XCLK 是相机的输入时钟,PCLK 是 像素时钟输出,由 XCLK 产生,PCLK 用于 FPGA 控制器采集视频图像数据。HREF 表示行参考信号输出,视频图像采集的像素和参考时钟进行比较,HSYNC 和 VSYNC 分别为行同步与场同步信号输出引脚,表示一帧数据的输出中断。SDA 和 SCL 为 IIC 总线的数据总线和时钟线,FPGA 通过 IIC 总线对 IMX490 内部寄存器进行初始值的 配置,使 IMX490 输出 GMSL 视频图像。IMX490 相机的驱动电路原理图如图 3.2 所 示。相机驱动电路需要的工作电压为 3.3V,该电压由电源芯片 U3 将 5V 转换得到, 以此向图像采集模块供电;摄像头的调焦模块和模拟电路的工作电压为 2.8V,该电压 由电源芯片 U2 将 3.3V 电压转换得到;摄像头图像采集核心模块的工作电压为 1.5V, 该电压由电源芯片 U1 将 2.8V 电压转换得到。

基于 JETSON+FPGA+GMSL+AI 车载视频采集与存储系统设计

最新推荐文章于 2026-01-10 06:10:37 发布

1006

1006

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?