1、简介

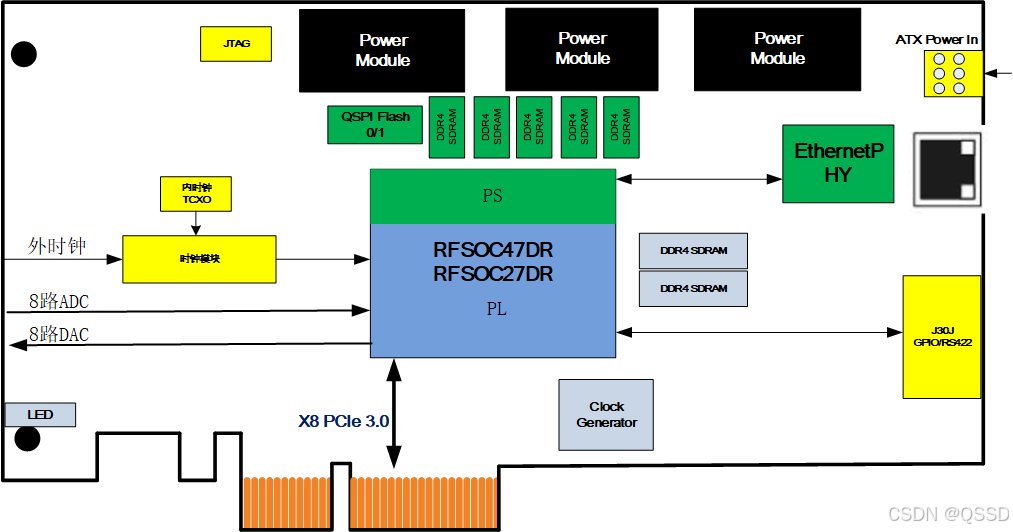

PCIE RFSOC数模混合信号处理卡,采用 Xilinx ZYNQ UltraScale+ RFSoC 27DR或47DR,实现了8路 ADC和8路DAC 端口,并支持外部同源参考时钟。对外J30J上支持24路双向GPIO、2组RS422、1组RS485、2组ps Uart,PS对外实现1个千兆网口。27DR ADC最高采样率 4.096GSPS 和DAC最高采样率 6.5536 GSPS; 47DR的ADC采样率最高可达5GSPS、DAC最高采样率 9.8 GSPS,分辨率14bit。可实现PC直接通过PCIE收发8收8发数据。

2、功能框图

3、技术指标

性能指标:

- FPGA封装支持47DR和27DR;

- 8x PCIe 3.0接口;

RF接口:

- 8路ADC (27DR:12-bit、4.096GSPS;47DR 14

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1174

1174

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?