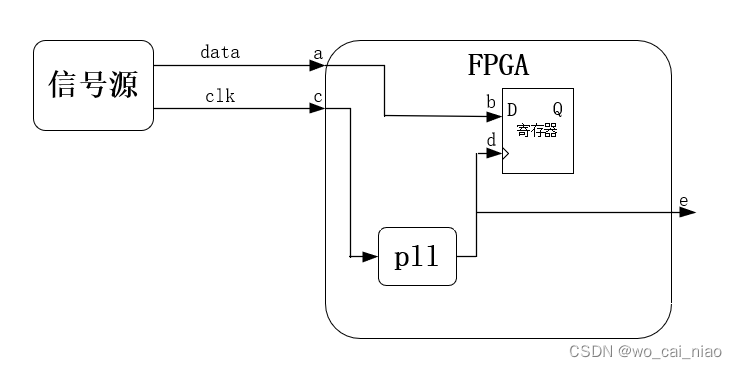

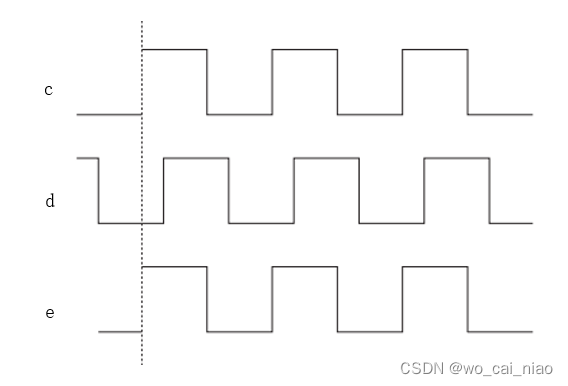

图1

以图1为例进行讲解

1、源同步补偿模式(source-synchronous compensation mode)

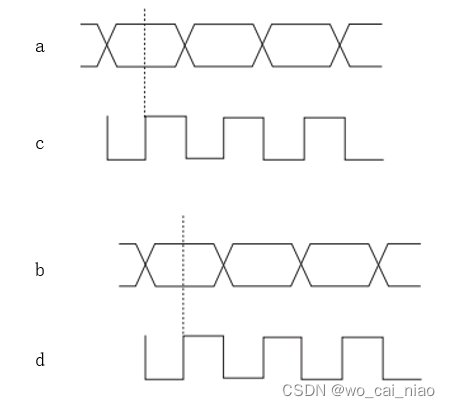

通常用于数据接口,特别是高速数据接口。源同步指数据和时钟来源于同一个数据源,数据和时钟之间有一个相位关系。源同步模式会调整c到d路径的布局布线(cd之间的路径会经过锁相环),使得ab路径和cd路延径的延时相等。数据与时钟在ac之间的相位关系与在bd之间的相位关系相同。

2、无补偿模式(no compensation mode)

在无补偿模式中,PLL不对任何时钟网络进行补偿。这样会有更佳的抖动性能。即指时钟经过图1中cd路径和ce路径该延迟多少就延迟多少,不会做任何补偿。时钟在d和e处的相位关系不确定,有可能超前也有可能滞后。

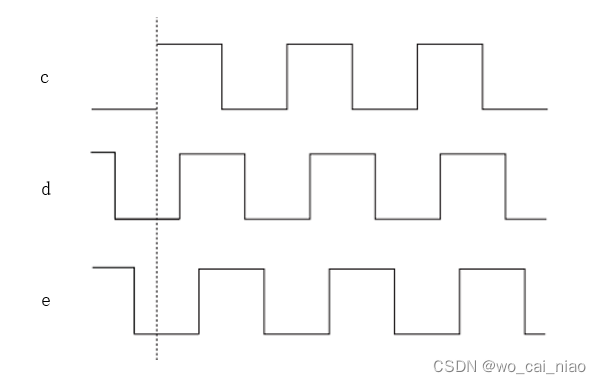

3、标准模式(normal mode)

在标准模式中时钟在cd路径上是有补偿滴,通过补偿使得时钟在c处的相位与时钟在d处的相位相同。但时钟在e处的相位没有得到补偿,因此e处的时钟有可能超前也有可能滞后。

由这个相位关系可知,标准模式下产生的时钟呢最好是用在内部寄存器上,不要用来输出,因为输出会产生相位的超前或者滞后,但在寄存器上它的相位关系是保持一致的。

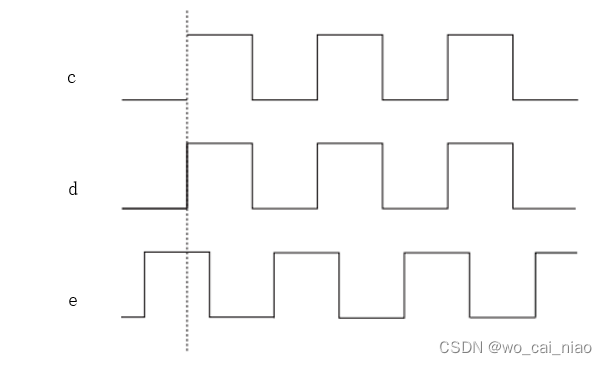

4、 零延迟缓冲模式(zero delay buffer mode)

零延迟缓冲模式与无补偿模式恰恰相反,它对ce路径进行了补偿,对cd路径没有补偿,因此建议在该模式下对时钟进行输出,不建议把时钟用在寄存器上,因为寄存器上的时钟相位会产生超前或者滞后。

1362

1362

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?