系列文章目录

二、FPGA学习笔记(二)Verilog语法初步学习(语法篇1)

四、FPGA学习笔记(四)通过数码管学习顶层模块和例化的编写

五、FPGA学习笔记(五)Testbench(测试平台)文件编写进行Modelsim仿真

六、FPGA学习笔记(六)Modelsim单独仿真和Quartus联合仿真

七、FPGA学习笔记(七)verilog的深入学习之任务与函数(语法篇3)

九、FPGA学习笔记(九)SPI学习总结及stm32的HAL库下SPI配置

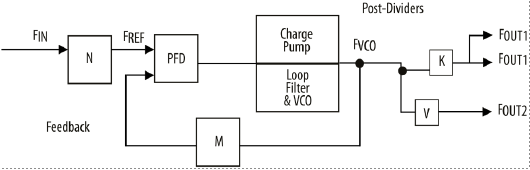

PLL锁相环

锁相环工作中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

Quartus II软件提供了锁相环PLL的IP核,具有时钟倍频(*2)、分频(/2)、相位偏移(0-360°)和可编程占空比的功能。

具体工作原理就不讨论了,看看怎么使用?

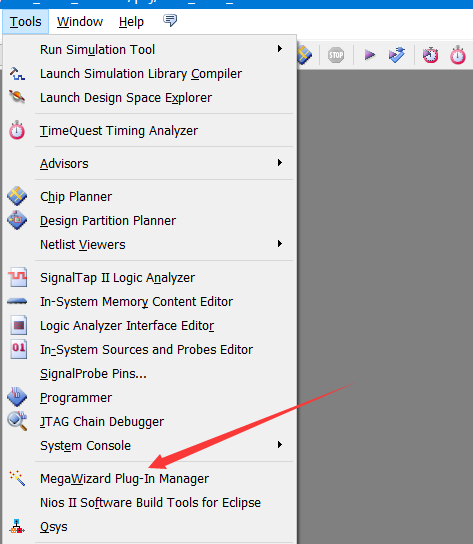

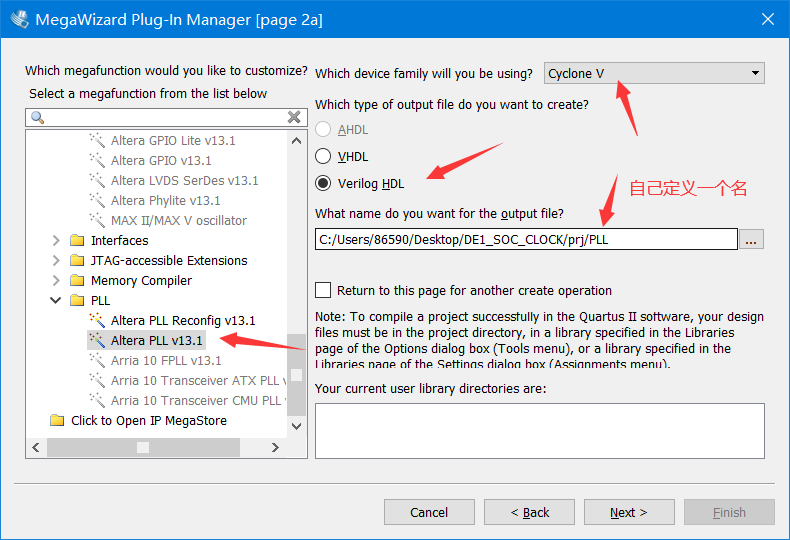

quartus13的使用方法

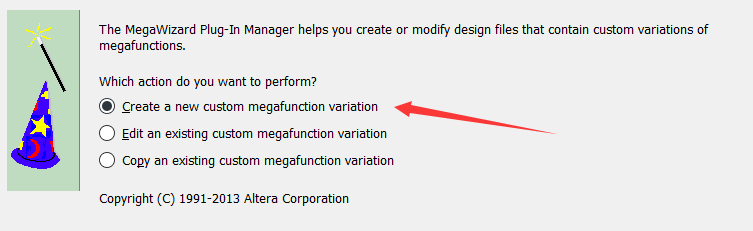

插件管理:帮助你创建或修改包含自定义变化的设计文件。

创建新的

订阅专栏 解锁全文

订阅专栏 解锁全文

3392

3392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?