目录

一、前言

在实际使用过程中,有时候需要得到不同频率的时钟,锁相环(PLL)可以对输入时钟进行倍频或者分频,以生成各种其他频率的时钟,在FPGA工程中,可以直接调用altera的IP核锁相环,FPGA型号为EP4CE6E22C8。

二、程序

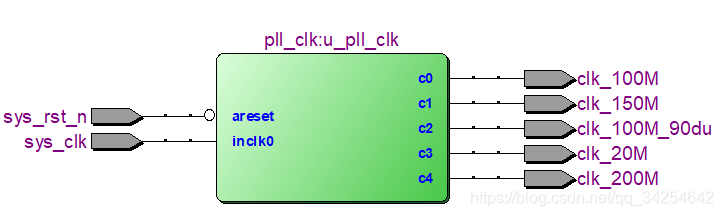

模块框图如下:

这里将50MHz的晶振时钟信号通过sys_clk引脚输入锁相环,然后经过倍频或者分频,产生5个时钟信号,分别是100MHz,150MHz,100MHz相位偏移90度,20MHz和200MHz。

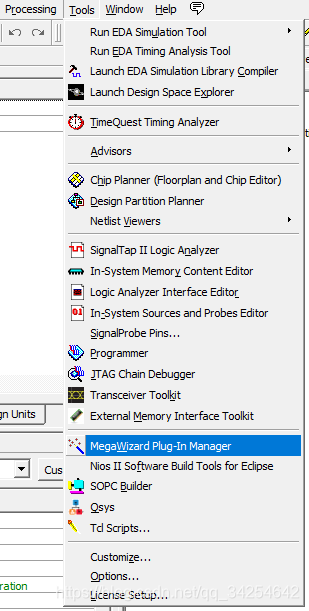

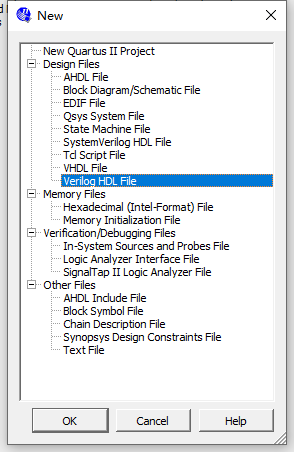

IP核锁相环调用如下,建立一个Quartus新工程altpll_test,然后选择Tools -> MegaWizard Plug_In Manager。

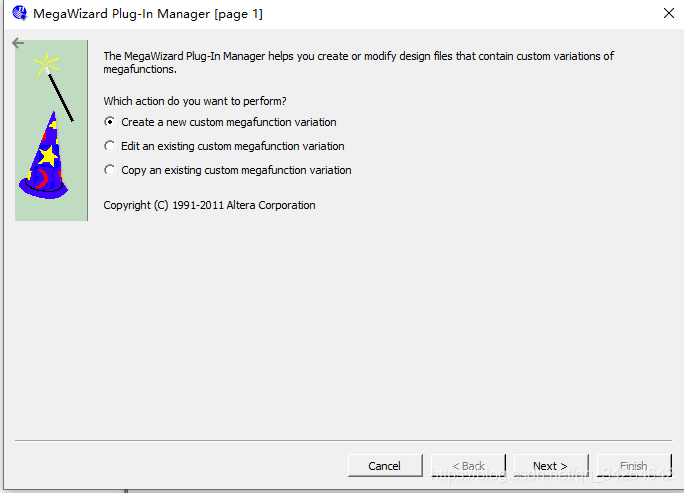

上图对话框选择第一个选项。

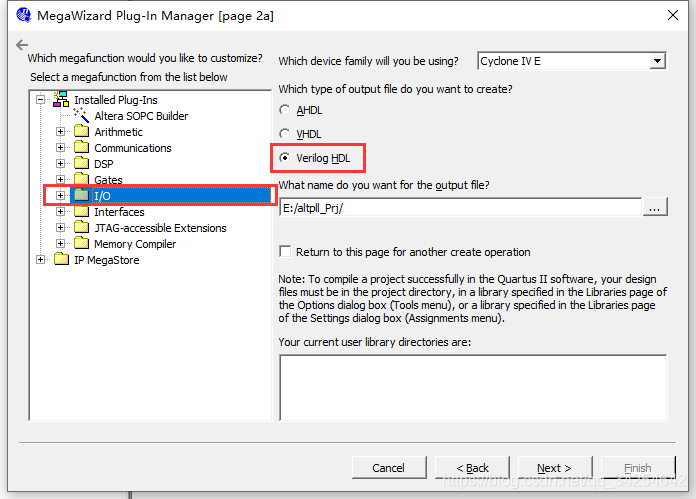

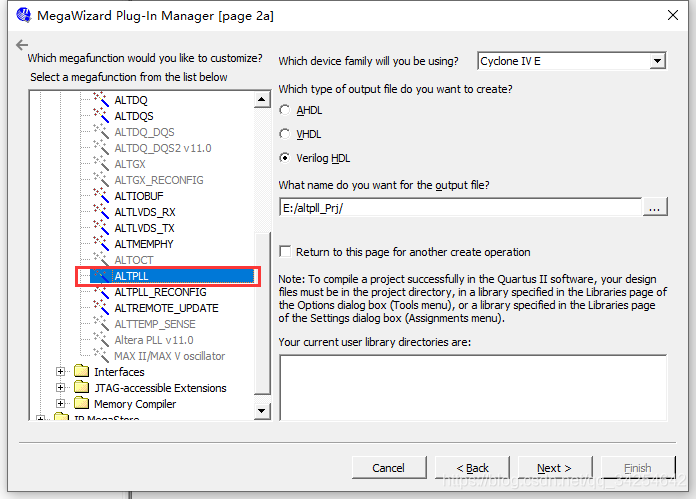

上图中选择Verilog HDL,左边选择IO类别里的ALTPLL,文件保存目录自己随便选。

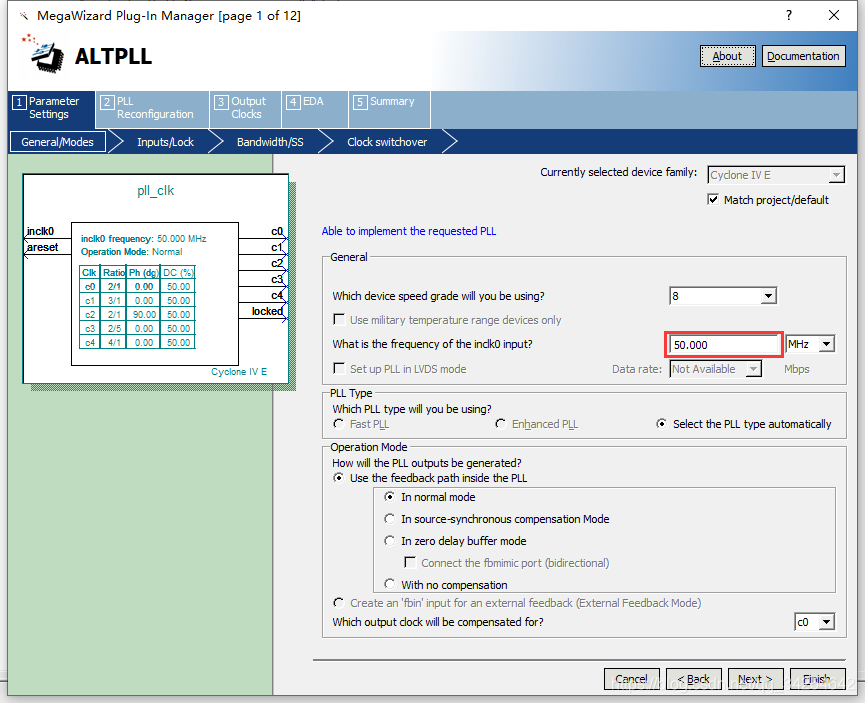

图中填写开发板的实际输入时钟频率50MHz,其他默认,然后Next,接下来几个页面一路默认Next,直到下面这里。

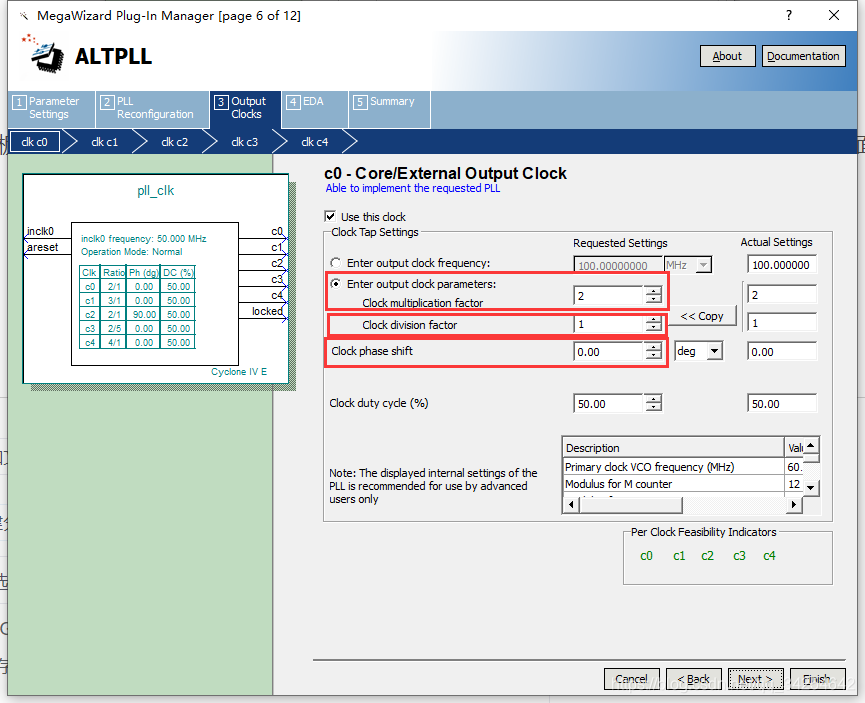

类似的页面有C0、C1、C2、C3、C4,是配置5个输出时钟引脚的配置的,可以设置倍频系数和分频系数,Actual Settings这一栏会显示实际调整到的配置,调整不到我们想要的时钟页面上会有错误提示的。C0、C1、C2、C3、C4这几个页面不一定要全部配置,需要用几个引脚就配置几个,配置完接下来几个页面后点Finsh就好了,ip核锁相环相关文件自动添加到工程里。其中锁相环配置接口如下:

module pll_clk (

areset,

inclk0,

c0,

c1,

c2,

c3,

c4,

locked);

input areset;

input inclk0;

output c0;

output c1;

output c2;

output c3;

output c4;

output locked;新建一个顶层文件altpll_test.v来调用锁相环。

module altpll_test(

input sys_clk,

input sys_rst_n,

output clk_100M,

output clk_150M,

output clk_100M_90du,

output clk_20M,

output clk_200M

);

wire locked;

wire rst_n;

assign rst_n = sys_rst_n & locked;

pll_clk u_pll_clk(

.areset (~sys_rst_n),

.inclk0 (sys_clk),

.c0 (clk_100M),

.c1 (clk_150M),

.c2 (clk_100M_90du),

.c3 (clk_20M),

.c4 (clk_200M),

.locked (locked)

);

endmodule

我们FPGA的复位信号是采用低电平复位,而锁相环是高电平复位所以在锁相环调用接口那sys_rst_n取了反,rst_n作为总的复位信号,当锁相环稳定后locked为高电平,此时才能让其他模块工作,要不然锁相环频率输出没稳定。

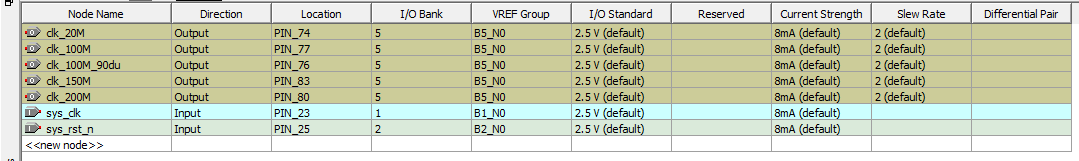

引脚配置如下:

三、实验分析

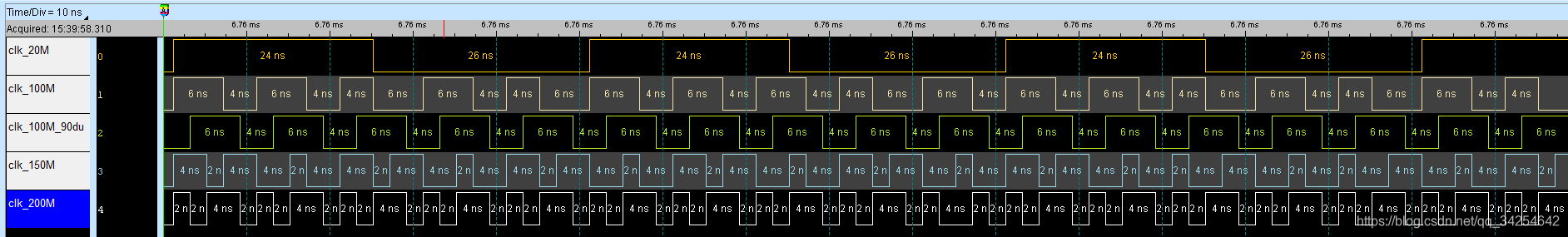

因为手头有逻辑分析仪,所以直接对着引脚抓输出时钟了,

可以看到当频率很高时(200M),输出的时钟虽然不是很完美的方波,但是总体上来说频率是很准的。

本文介绍在FPGA工程中使用Altera的IP核PLL,实现从50MHz输入时钟生成100MHz、150MHz、100MHz相位偏移90度、20MHz和200MHz时钟信号的方法。详细讲解了PLL配置流程及引脚配置,实验验证了输出时钟的准确性。

本文介绍在FPGA工程中使用Altera的IP核PLL,实现从50MHz输入时钟生成100MHz、150MHz、100MHz相位偏移90度、20MHz和200MHz时钟信号的方法。详细讲解了PLL配置流程及引脚配置,实验验证了输出时钟的准确性。

1265

1265

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?