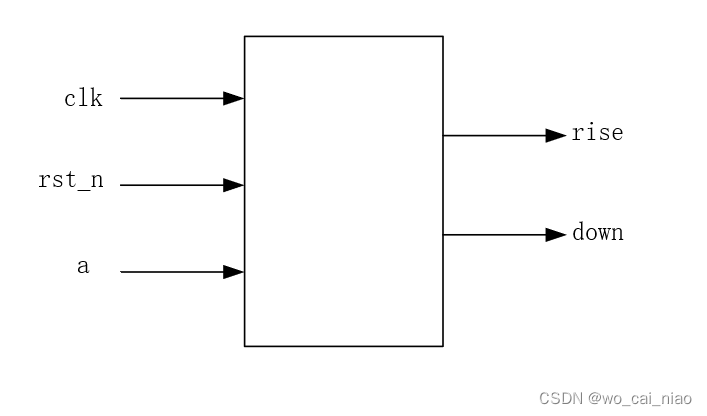

描述:有一个缓慢变化的1bit信号a,编写一个程序检测a信号的上升沿给出指示信号rise,当a信号出现下降沿时给出指示信号down。

一、检测双边沿、上升沿、下降沿

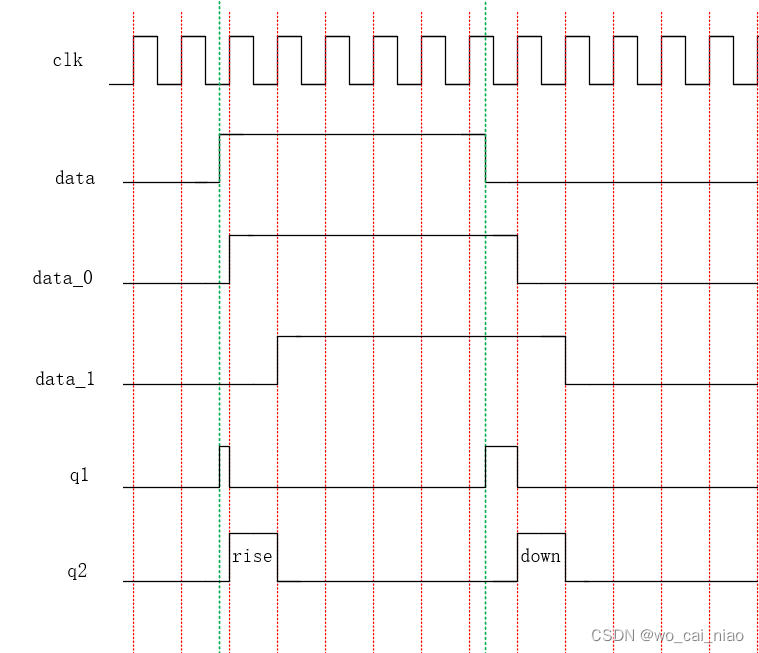

双边沿:如下图,来一个与时钟不同步的信号data,检测其边沿,data_0为打1拍,data_2为打2拍,q1为打一拍后的输出,q2为打2拍后的输出,显然q1可能产生毛刺,q2波形质量更好。

q1 = data ^ data_0;

q2=data_0 ^ data_1;(q2好,用q2)

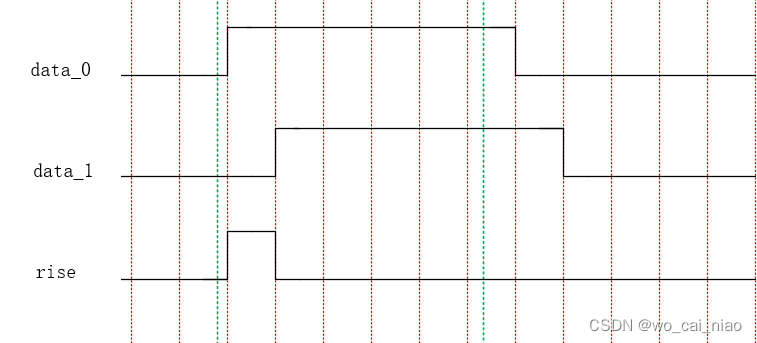

上升沿:rise = data_0 & (~data_1);

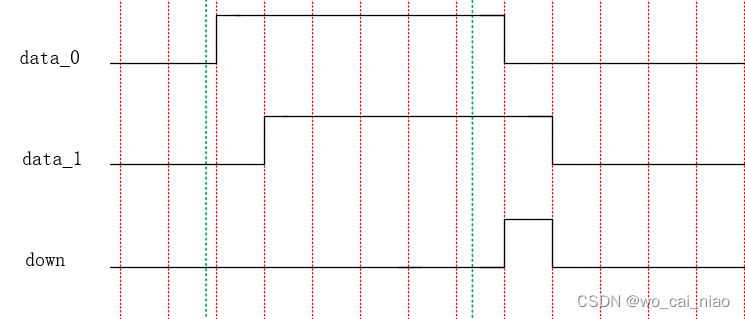

下降沿:down = data_1 & (~data_0);

该文描述了如何编程检测一个1bit信号的上升沿和下降沿。使用data的不同步信号,通过计算data与data的延迟版本的异或来检测双边沿,其中q2波形提供更好的结果。上升沿通过data_0与data_1的非运算表示,下降沿则由data_1与data_0的非运算得出。

该文描述了如何编程检测一个1bit信号的上升沿和下降沿。使用data的不同步信号,通过计算data与data的延迟版本的异或来检测双边沿,其中q2波形提供更好的结果。上升沿通过data_0与data_1的非运算表示,下降沿则由data_1与data_0的非运算得出。

885

885

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?