二、注意事项

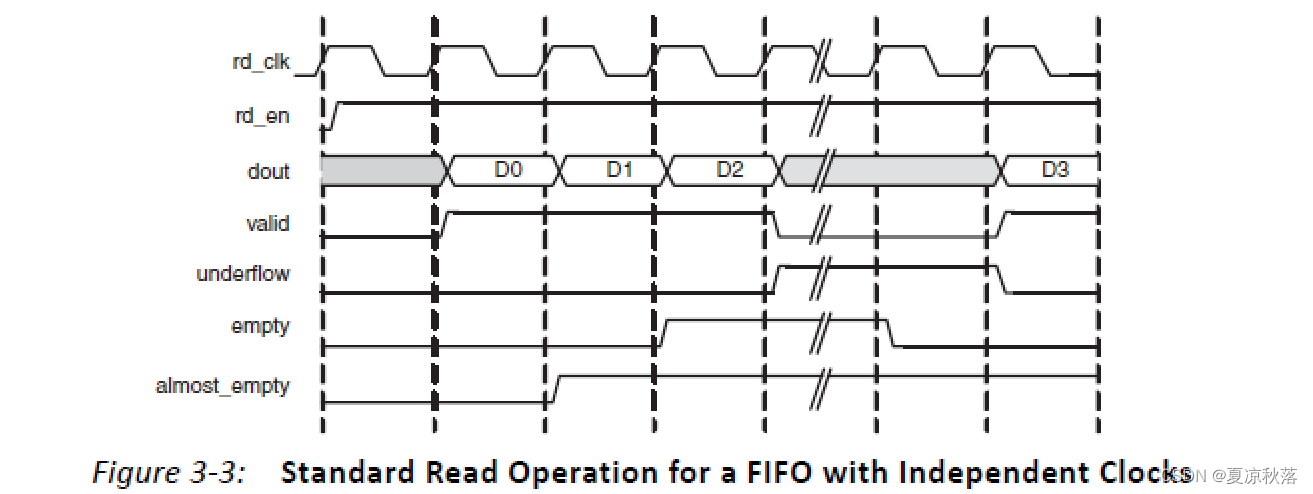

标准fifo模式(读出的数据会滞后读使能一个时钟周期,但与valid保持对齐):

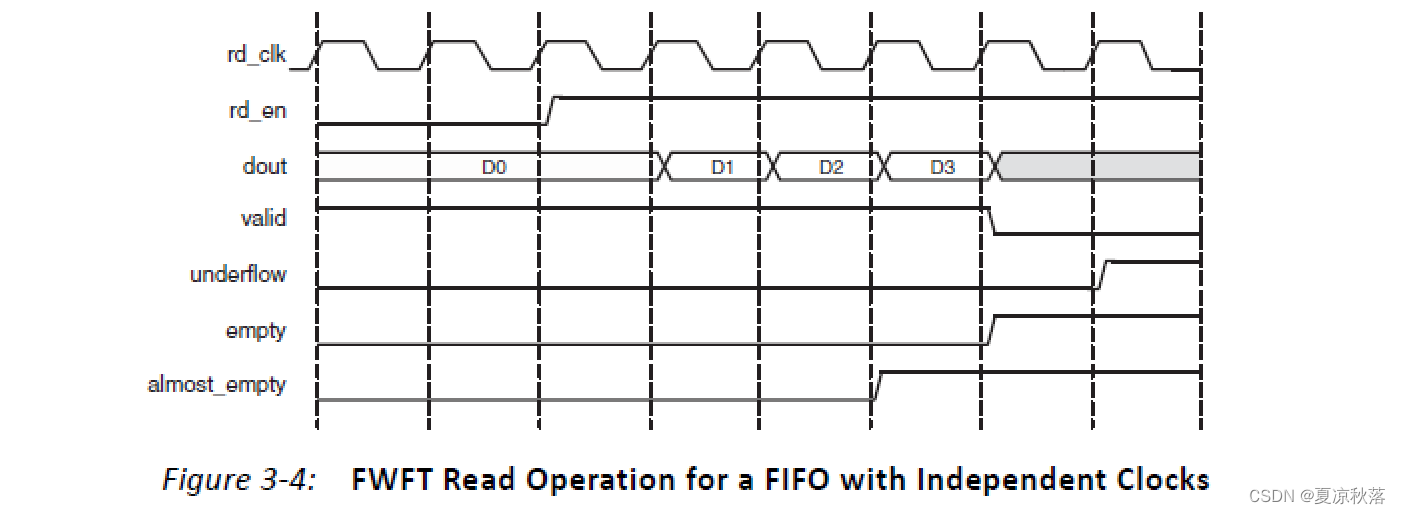

FWFT模式(数据和读使能在同一个时钟周期输出,valid表示不精确,会提前拉高):

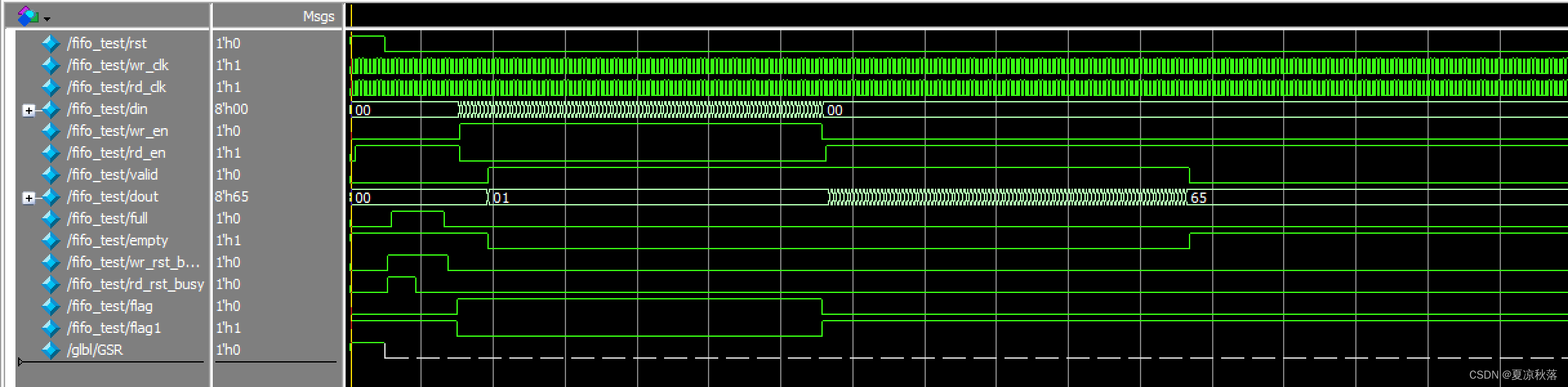

读使能一直有效,最后把fifo读空:

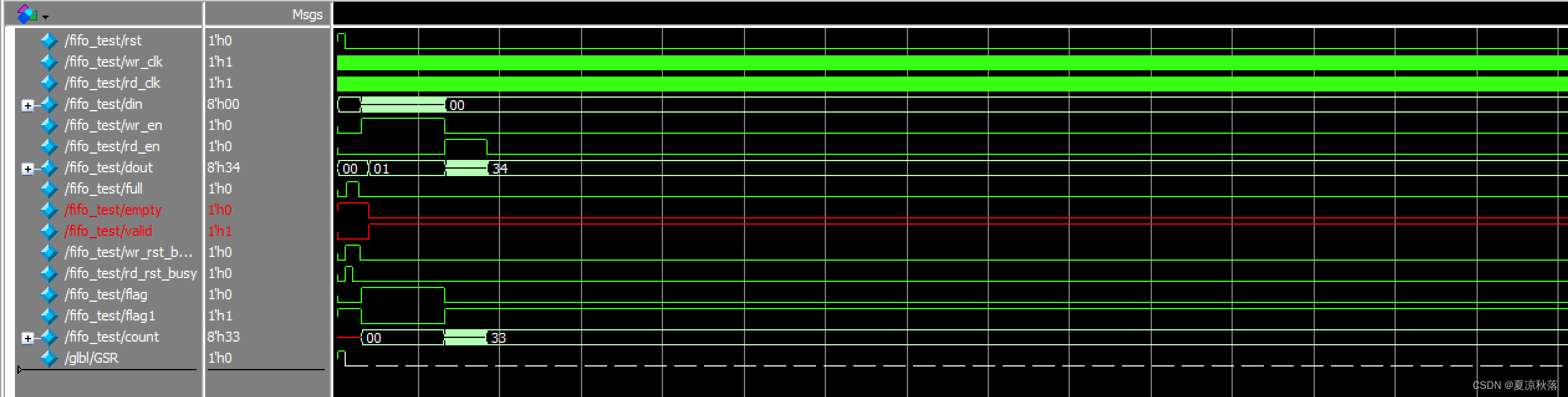

读使能读了一段数据后拉低,fifo中仍然有数据:

FWFT模式发现:

(1)valid信号会在读使能之前拉高(或者fifo中写入第一个数据后就拉高),fifo读空之后拉低,如果fifo中一直存在数据,即valid一直为高。

(2)fifo在复位后,full会拉高一段时间,此时不能进行写,否则会导致数据丢失,在写程序时候注意保护。

(3)fifo在读空后在读,仿真显示的是会保持原来的数据

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?