FIFO的数据已经读空了,再读会怎么样?

首先声明一下自己所用的IP核来源,源自ALTERA公司开发的IP核。

然后说结论,FIFO默认输出的数据为0,如果写入数据后再读FIFO,在rdreq归零后FIFO的读出数据线会一直保持最后一个读出数据的值(也有人会用clock来做读取的判断条件,clock跟rdreq本质上是一样的,但一般保持clock的周期不变比较容易让人理解)。

实际演示

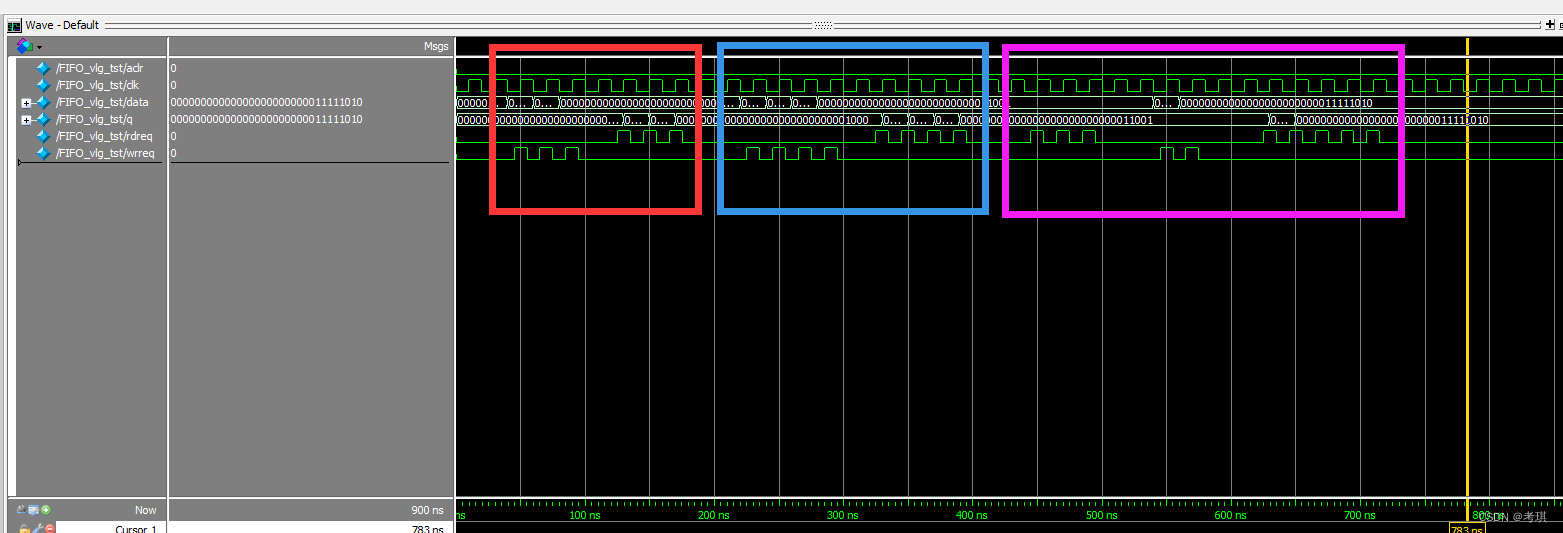

这是一个FIFO输入输出的仿真工程,从中可以看到:

这是一个FIFO输入输出的仿真工程,从中可以看到:

1.红框部分是正常的读入与读出。读入数据是你自己输入进FIFO的,所以其变化特征没意义,注意尽量在FIFO_clk的下降沿变化读入数据以保持上升沿时读入数据作为判定条件的稳定。

2.蓝框部分是进行过读入读出操作后,再读入读出的操作,可以看到没有任何问题,FIFO是可以正常复用的。

3.紫框部分表示连续多次读取FIFO直至将FIFO读空。FIFO读空后,会保持输出最后一个留在FIFO内的之前写入的数值,并不会随着FIFO的读取信号而发生改变。重新写入数据后,也可以正常使用,正常读新的数值。

当FIFO的数据被读空后,其默认输出数据为0,并在后续读操作中保持最后一个读出的数据值。在FIFO再次接收到数据后,可以正常读取新的数值。此特性在使用ALTERA公司的IP核时表现明显,且连续读取直至FIFO为空时,FIFO会持续输出最后留存的数值,直到有新数据写入。

当FIFO的数据被读空后,其默认输出数据为0,并在后续读操作中保持最后一个读出的数据值。在FIFO再次接收到数据后,可以正常读取新的数值。此特性在使用ALTERA公司的IP核时表现明显,且连续读取直至FIFO为空时,FIFO会持续输出最后留存的数值,直到有新数据写入。

1178

1178

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?