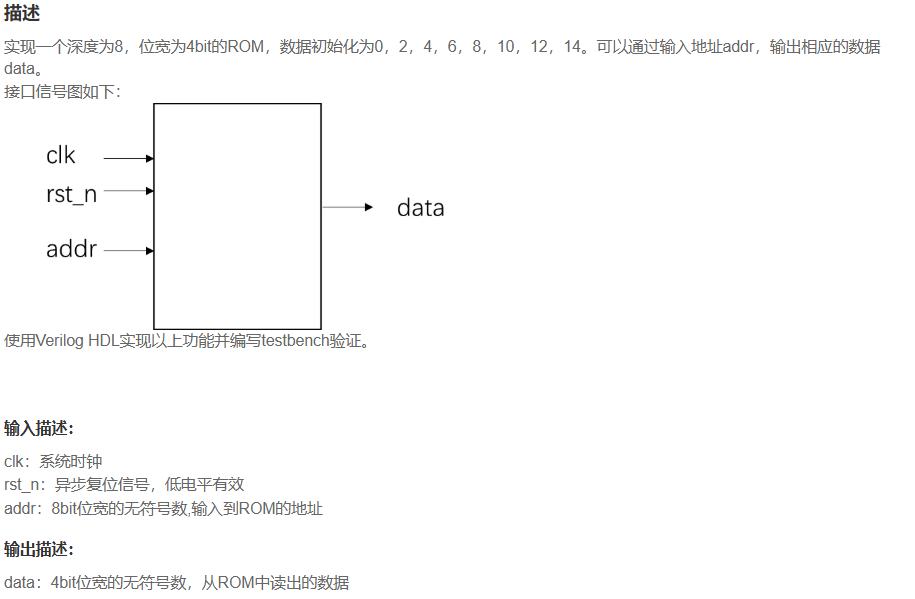

VL23 ROM的简单实现

ROM的深度是什么

深度表示 ROM 有多少个独立的存储位置(地址)。

例子:

举例说明:

一个 ROM 的规格为 1K × 8:

“1K” 表示深度 = 1024(即有 1024 个地址);

“×8” 表示宽度 = 8 位(每个地址输出 8 位数据);

总容量 = 深度 × 宽度 = 1024 × 8 = 8192 位 = 1 KB。

思路一:使用case

`timescale 1ns/1ns

module rom(

input clk,

input rst_n,

input [7:0]addr,

output [3:0]data

);

reg [3:0] out;

always @(posedge clk , negedge clk ,negedge rst_n) begin

if(!rst_n)

out <= 4'd0;

else

case(addr)

8'd7: out <= 4'd14;

8'd6: out <= 4'd12;

8'd5: out <= 4'd10;

8'd4: out <= 4'd8;

8'd3: out <= 4'd6;

8'd2: out <= 4'd4;

8'd1: out <= 4'd2;

8'd0: out <= 4'd0;

default: out <= 4'd0;

endcase

end

assign data = out;

endmodule

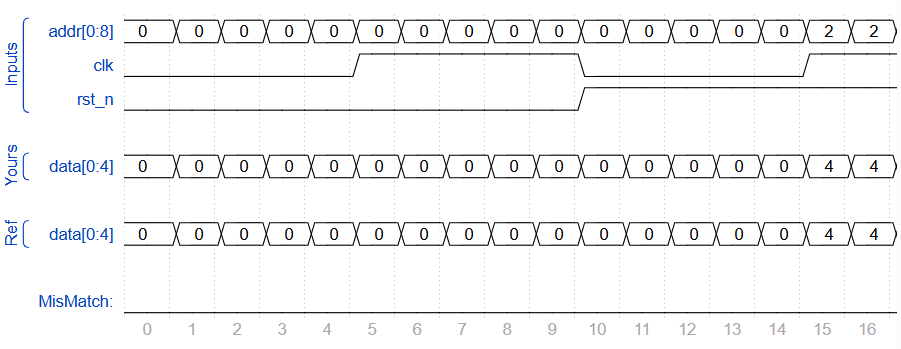

输出波形:

思路二:

`timescale 1ns/1ns

module rom(

input clk,

input rst_n,

input [7:0]addr,

output [3:0]data

);

reg [3:0] out ;

reg [3:0] rom [7:0];

always @(posedge clk , negedge rst_n) begin

if(!rst_n) begin

rom[0] <= 4'd0;

rom[1] <= 4'd2;

rom[2] <= 4'd4;

rom[3] <= 4'd6;

rom[4] <= 4'd8;

rom[5] <= 4'd10;

rom[6] <= 4'd12;

rom[7] <= 4'd14;

end

else begin

rom[0] <= 4'd0;

rom[1] <= 4'd2;

rom[2] <= 4'd4;

rom[3] <= 4'd6;

rom[4] <= 4'd8;

rom[5] <= 4'd10;

rom[6] <= 4'd12;

rom[7] <= 4'd14;

end

end

always @(posedge clk , negedge clk , negedge rst_n)

if(!rst_n)

out <= 4'd0;

else

out <= rom[addr];

assign data = out ;

endmodule

这种写法有问题:

1.rom的赋值冗余,分析其目的就是想把rom的值保持为{0,2,4,6,8,10,12,14},可以考虑使用initial

2.设置reg变量out,当初是为了解决data为wire型无法在always块里被赋值,但是现在是:现将rom[addr]赋值给out,out再赋值给data,为何不去掉中间商呢?

最终改为:

`timescale 1ns/1ns

module rom(

input clk,

input rst_n,

input [7:0]addr,

output [3:0]data

);

reg [3:0] rom [7:0];

initial begin

rom[0] <= 4'd0;

rom[1] <= 4'd2;

rom[2] <= 4'd4;

rom[3] <= 4'd6;

rom[4] <= 4'd8;

rom[5] <= 4'd10;

rom[6] <= 4'd12;

rom[7] <= 4'd14;

end

assign data = rom[addr] ;

endmodule

137

137

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?