VL3 奇偶校验

什么是奇偶校验?

计算数据中 “1” 的个数是奇数还是偶数,并据此生成一个校验位(parity bit)。

一、 偶校验(Even Parity)

1.添加一个校验位,使得 33 位(32 数据 + 1 校验)。

2.例如:若 32 位中有 5 个 1(奇数),则校验位 = 1 → 总共 6 个 1(偶数)。

二、奇校验(Odd Parity)

1.添加一个校验位,使得 33 位中 “1” 的总数为奇数。

2.例如:若 32 位中有 6 个 1(偶数),则校验位 = 1 → 总共 7 个 1(奇数)。

三、代码实现

校验的数据为data

那么在data前面加一个^就代表计算data里边是否有奇数个1

^data =1 说明data有奇数个1;

^data =0 说明data有偶数个1;

三、题目

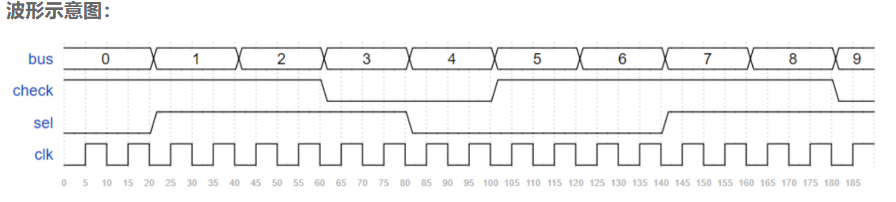

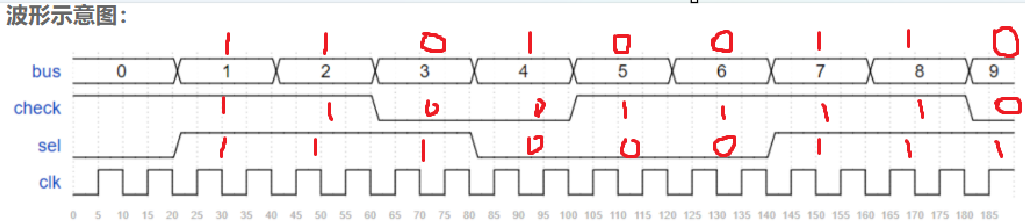

可以看出,

sel = 1 时,check和^bus相同,说明sel = 1 时是偶校验;

sel = 0 时,check和^bus相异,说明sel = 0 时是奇校验;

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

//*************code***********//

assign check = sel ? ^bus : ~^bus;

//*************code***********//

endmodule

奇偶校验原理与FPGA实现

奇偶校验原理与FPGA实现

409

409

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?