CHAPTER 15 三维集成电路中的同步

15.1 平面时钟分配网络的综合技术

时钟信号构成了同步集成系统的基石,因为该信号提供了时序参考,以维持正确的时序操作。

在传递时钟信号的过程中,一个重要的步骤是设计时钟分配网络,对于大多数现代集成电路系统而言,该网络包含具有多个分配层级的层次化时钟网络拓扑 [574]。更高的集成密度、更大的硅面积、不断增加的功耗以及工艺和环境变化是一些导致现代集成系统内出现多时钟域的主要原因 [264]。因此,在这些复杂系统中分配时钟信号的问题可以描述为:在偏斜、压摆率、功耗和布线约束下,将一个稳定且可靠的时钟信号传递到整个电路模块(例如处理核心)或整个时钟域内的所有时钟汇点(如触发器)的任务。根据系统的性能规格,这些约束的重要性可能有所不同,这意味着设计空间会随着系统规格的变化而变化。

在分层时钟网络中,时钟网络层次结构的最上层覆盖大面积区域,通常通过需要等距路径的对称拓扑实现。这些路径从源到时钟网络层次结构下一级的根节点具有相同的特性(例如延迟和压摆率)。全局网络由多种不同的拓扑结构组成,例如H树、X树、环形以及网状/网格拓扑 [575,576]。这些全局拓扑通常终止于分布在系统各处的预设且保留的位置。而层次结构的较低层级则连接到电路单元的时钟引脚,每个层次级可能包含数千个时钟汇点。具有特定时序特性的综合时钟树通常为所有这些汇点提供时钟信号。在过去几十年中,已发表了大量由设计自动化工具支持的用于二维电路的时钟树综合(CTS)算法。

随着三维集成电路的发展,许多研究工作聚焦于三个物理维度中的时钟网络。这些三维时钟综合技术的需求源于垂直互连(即硅通孔(TSV))。TSV的阻抗特性与水平导线以及三维堆叠中每一层存在的局部时钟网络的阻抗特性有很大差异,这使得键合前测试成为一项具有挑战性的任务。

本章讨论三维时钟网络拓扑的设计,回顾了全局拓扑以及三维CTS算法。某些用于二维(2‐D)时钟树综合的算法已被应用于三维CTS方法的开发中,这些算法在第15.1节中进行了讨论。三维全局时钟分配网络的设计与性能在第15.2节中介绍。三维时钟树的综合技术比较见于第15.3节。强调与三维时钟树综合相关的实际问题的增强技术在第15.4节中进行了回顾。

本章的主要概念总结于第15.5节。请注意,本章所述的大部分结果基于仿真和模型,而来自一个表征全局三维时钟分配网络性能的测试电路的硅片测量结果将在第16章案例研究:三维集成电路的时钟分配网络中介绍。

15.1.1 均值与中位数法

MMM算法通过在x和y方向上使用切割(即二分划分)来迭代地划分布线路网(或布线平面)内的时钟汇点,每次切割生成两个新的时钟汇点集合。假设有一组m个时钟汇点,每个时钟汇点记为si,其在布线平面上的坐标为(xi, yi)。这些时钟汇点可由有限集合S = {s1; s2; s3; … sm} ⊂ R²表示。该集合的质心位置为

$$

x_c = \frac{\sum_{i=1}^{m} x_i}{m}; \quad (15.1)

$$

$$

y_c = \frac{\sum_{i=1}^{m} y_i}{m}; \quad (15.2)

$$

其中这些坐标构成时钟树的根节点。为了沿物理方向进行切割,需要利用时钟汇点的排序。

通过分别将时钟汇点的x坐标和y坐标按升序排列,形成两种不同的时钟汇点排序,即对于集合Sx(S)的每个子集,若xi ≤ xj,则si在Sx(S)中位于sj之前。对于子集Sy(S),关于y坐标也适用类似的规则。根据这些排序,在每种排序的中位数周围定义了四个不同的子集。

$$

S_L(S) = { s_i \in S_x \mid i \leq \lfloor m/2 \rfloor }; \quad (15.3)

$$

$$

S_R(S) = { s_i \in S_x \mid \lfloor m/2 \rfloor < i \leq m }; \quad (15.4)

$$

$$

S_B(S) = { s_i \in S_y \mid i \leq \lfloor m/2 \rfloor }; \quad (15.5)

$$

$$

S_T(S) = { s_i \in S_y \mid \lfloor m/2 \rfloor < i \leq m }; \quad (15.6)

$$

图15.1 一条数据路径,描绘了一对顺序相邻寄存器 [577,583]。

这四个子集是通过对每个方向上的排序在中位数处进行切割而产生的。所有这些子集包含的时钟汇点数量大致与 $|SL|$, $|SR|$ # 1 相同。该不等式同样适用于子集 SB 和 ST。为每个新子集确定其质心。该算法将这些新确定的点与初始集合S的质心(即树的根节点)连接起来。

此过程重复进行,对每次x方向切割生成左(L)和右(R)两个集合,对每次y方向切割生成下(B)和上(T)两个集合。当每个新集合仅包含一个时钟汇点时,该过程终止。

该算法的一个简单示例如图15.2所示,其中标注了不同集合的质心之间的布线。尽管在一次迭代中由切割确定的质心与后续质心之间的布线长度相等,但随着算法的推进,可能会出现不同的布线长度,如图15.2A所示。为解决此情况,应用了两对切割。这一对切割导致更低的偏斜。该前瞻过程产生了更优的布线方案。如图15.2B所示,由y-和x‐切割生成的树相比图15.2A中的树具有更低的偏斜。该算法的复杂度,包括前瞻功能,为O(m log m)。

MMM方法确保在每次执行切割操作的迭代之后,到新形成子集的质心的布线路径长度相等,从而实现较低(或零)的偏斜。然而,这种布线通常比具有相同时钟汇点集合[403]的最小正交斯坦纳树(RMST)的长度更长。如[578]所述,生成的时钟树的线长随 $3/2 \sqrt{mp}$ 成比例增长,而对于RMST,当m个点(即时钟汇点)在布线路网上均匀分布时,树的长度增长为 $(\sqrt{mp} + 1)$。两种布线算法之间的比率以约1.53的恒定因子增加,表明MMM方法的线长开销并不显著。

为了限制这种额外开销,MMM方法分为两个阶段使用。在第一阶段,生成的切割子集包含大量时钟汇点时,采用MMM方法进行布线。在第二阶段,当后续迭代产生的每个子集内的时钟汇点数量较小时,采用标准布线算法更为合适,以保证最小线长,同时使时钟偏斜仅有较低且可接受的增加。应用非MMM布线技术的时机(即树的深度或迭代次数)取决于可容忍的偏斜程度。

图15.2 MMM时钟合成方法的简单示例,其中生成了一个时钟树。(A) 无前瞻,(B) 有前瞻。在(A)中,xy切割导致的偏斜大于在(B)中的yx切割。

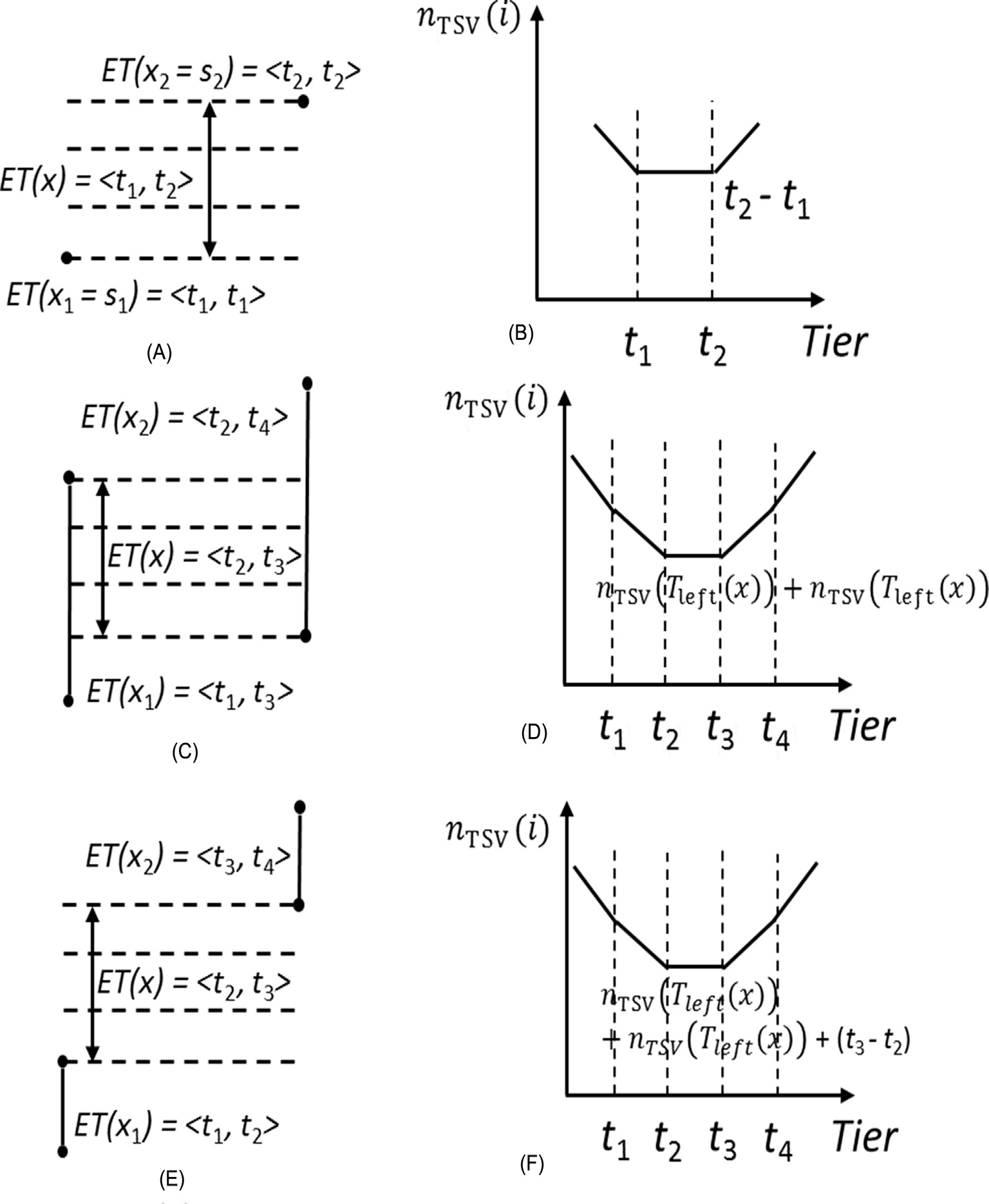

15.1.2 延迟合并嵌入法

另一种已扩展用于支持三维时钟网络综合的流行技术是DME方法,这是一种两阶段CTS技术 [581,582]。该方法的输入是在某种拓扑结构(通常为树)中汇点的连接性,其中汇点的位置已知,内部节点被放置以确保在最小线长下实现零偏斜(假设采用线性延迟模型)[581]。因此,在假设线性延迟模型的情况下,DME技术可生成最优的零偏斜时钟网络;而当使用其他更复杂的延迟模型(如埃尔莫尔延迟模型)时,则会产生次优的时钟树。尽管如此,在这种情况下结果虽为次优,但总体质量仍然很高,能够产生低线长且零偏斜的时钟树。DME方法的优势在于,与MMM相比,它在构建零偏斜时钟网络的同时还最小化了线长。

DME技术不受时钟网络拓扑结构的限制,因此可以在时钟树的内部节点通过MMM方法生成后,将其作为后处理步骤应用。然而需要注意的是,拓扑结构的选择或生成时钟网络所采用技术的选择会影响DME方法产生的结果质量(即总线长,因为零偏斜是保证的)。

DME方法包含一个自下而上阶段和一个自顶向下阶段。在自下而上阶段,确定每个内部节点的可行放置位置。每个内部节点是(两个)合并的子树根节点的父节点。在自顶向下阶段,将内部节点嵌入到这些可行位置中的一个,从而在保证时钟网络内所有汇点零偏斜的同时,实现最小线长(针对线性延迟模型)。

为解释该方法,首先介绍一些相关术语。在MMM方法中,将包含m个时钟汇点的有限集合S及这些汇点的相应位置作为输入。通过DME方法在曼哈顿平面上嵌入一棵时钟树,记为T(S),其中树的每个内部节点的位置被确定,以确保偏斜为零且时钟树的线长最小。每个节点的位置表示为pl(u)。假设u是另一节点w的父节点,ew表示从父节点到子节点的有向边。该边的代价记为 $|e_w|$。由于曼哈顿平面嵌入了时钟网络,此代价等于(或大于)这两个节点之间的曼哈顿距离。因此,整棵树T(S)的代价是所有这些边的线长之和。

类似地,从源节点u到节点w的任意路径的延迟表示为 $t_d(s_u, s_w)$。同一源节点出发的两条路径之间的时钟偏斜由 $|t_d(s_u, s_w) - t_d(s_u, s_v)|$ 描述。假设时钟网络的根节点为sr,则T(S)的时钟偏斜是S中所有汇点对si、sj之间 $|t_d(s_r, s_i) - t_d(s_r, s_j)|$ 的最大差值。如果采用线性延迟模型来估计每条源‐汇路径的延迟,则该延迟是从源节点u到汇节点w的路径上各边延迟的求和。

$$

t_{ld}(u, w) = \sum_{e_v \in \text{path}(u,w)} |e_v|; \quad (15.7)

$$

除了这一符号表示外,还需要一些其他定义来描述DME方法。在自底向上步骤中确定的每个内部节点的位点称为合并段。合并段是具有斜率±1或与x-y布线方向成±45°角的线段。

类似地,曼哈顿平面上距离曼哈顿弧固定距离内的点集形成一个倾斜矩形区域(TRR),该区域内接于曼哈顿弧。TRR的一个示例如图15.3所示,其中也显示了TRR的核心弧和半径。该核心弧由距离TRR边界最远的所有点组成(始终假设为曼哈顿距离)。

图15.3 TRR,其中的核心该区域是一个曼哈顿弧,边界点与核心之间的距离为半径距离。

对于节点u,该节点的合并段ms(u)确定如下。如果u属于S,则合并段为时钟汇的位置;否则,u是一个内部节点,其合并段的长度和位置取决于u的子节点的合并段。假设节点a和b是u的子节点,并且由于此步骤以自底向上的方式进行,因此节点a和b的合并段(分别记为ms(a)和ms(b))已知,且均为曼哈顿弧[581]。这种情况如图15.4所示。节点u的合并段也是一个曼哈顿弧,通过两个TRR的交集获得,这两个TRR的核心分别为线段ms(a)和ms(b)。因此,ms(u)形式化描述为 $ms(u) = TRR_a \cap TRR_b$。TRRa和TRRb的半径分别为 $|e_a|$ 和 $|e_b|$,如图中所示。以节点a和b为根的子树的合并代价为 $|e_a| + |e_b|$。目标是确定这些半径(即 $|e_a|$ 和 $|e_b|$),使得合并代价最小化,并满足零偏斜约束。

假设采用线性延迟模型,合并代价的下界等于ms(a)与ms(b)之间的最小曼哈顿距离,记为 $MD_{min} = d(ms(a), ms(b))$。如果节点a和b的延迟严重不平衡,为了满足零偏斜要求,合并代价将偏离该最小值,并可能需要额外的布线。节点u处的零偏斜要求可以从

$$

t_{ld}(a) + |e_a| = t_{ld}(b) + |e_b|; \quad (15.8)

$$

其中 $t_{ld}(a)$ 和 $t_{ld}(b)$ 分别表示到达以节点a和b为根的子树汇点的(线性模型)延迟。注意,由于在每一级都满足零偏斜要求,树,这些延迟在来自这些节点的子树的每个汇点处都相同。TRRa和TRRb的半径通过让 $|e_a| + |e_b| = MD_{min}$ 获得,且如果 $|t_{ld}(a) - t_{ld}(b)| \leq MD_{min}$,

$$

|e_a| = \frac{MD_{min} + t_{ld}(b) - t_{ld}(a)}{2}; \quad (15.9)

$$

and

$$

|e_b| = MD_{min} - |e_a|; \quad (15.10)

$$

如果条件 $|t_{ld}(a) - t_{ld}(b)| \leq MD_{min}$ 不满足,则需要额外的线长来平衡从节点u到节点a和b的偏斜,从而增加合并代价。

自下而上阶段递归地合并T(S)的节点,直到到达根节点sr。时钟驱动器通常放置在特定位置,该位置不会被根节点的合并段所经过。一条额外的线段连接到sr,且不会降低最终树的性能。当获得根节点的合并段时,自下而上阶段(即延迟合并)终止。

自顶向下阶段(即嵌入)如下。从根节点开始,依次确定每个节点的精确定位pl(u)。对于sr,通常可以选择ms(sr)上的任意一点作为pl(sr)。对于任何其他内部节点u,可以选择ms(u)上的任意一点作为pl(u),该点距离u的父节点的位置放置pl(p)不超过 $|e_u|$。根据合并段的构造,此位置必然存在[582]。图15.5展示了这种情况的一个示例。

图15.4 合并段根据TRRa和TRRb,为作为节点a和b的父节点的节点u计算ms(u)值。

图15.5 具有核心点的TRR。父节点p的放置位置pl(p)(从上一次迭代中已知)以及等于边eu的线长的半径。ms(u)在TRR内的线段为粗线,表示节点u的有效放置位置集合。

DME技术的操作可以通过一个实际例子更好地理解。图15.6展示了一个具有八个汇点(例如,s1到s8)的简单时钟拓扑结构。假设每个汇点的延迟相同(或为零),则可以确定每个汇点的TRR。由于每个汇点的位置已知且假设延迟为零,$t_{ld}(s_i) = 0$,(15.9)和(15.10)等于一半的各汇点对之间的曼哈顿距离si和sj(见图15.6A)。每对汇点的TRRs半径相同,每个父节点的合并段msi,j用粗线表示。在图15.6B中,获得了树的上一级节点的合并段。注意,在此特定示例中,ms1,4是一个单点,因为节点s1,2和s3,4的TRRs仅在一个点相交。在图15.6C中,根节点s1,8的合并段msr位于节点s1,4和s5,8的TRRs的交点处。

由于所有节点的合并段均已确定,自顶向下阶段将决定树中内部节点的位置放置。如前所述,对于树的根节点,可以选择ms1,8上的任意一点,该点在图15.6D中用三角形表示。

为了确定pl(s1,4)和pl(s5,8),分别从根节点的放置位置pl(sr)出发,绘制半径为 $|e_{ms1,4}|$ 和 $|e_{ms5,8}|$ 的TRRs(时序相关区域)。由于ms1,4仅对应一个单点,因此在图15.6D中仅绘制了节点s1,4的TRR。最粗线段表示节点s5,8,的有效放置点,该线段上的任意点均可被选为pl(s5,8)。类似地,在图15.6E中绘制TRRs以确定节点s1,2,、s3,4,、s5,6,和s7,8的有效放置位置。注意,对于节点s1,2和s3,4,,有效放置位置仅可能位于一个单点。最终生成的时钟树如图15.6F所示,其中实线表示合并段,其余所有线条表示树的分支。圆点表示树中内部节点的放置位置。

图15.6 具有八个汇点的树的DME方法示例。(A)到(C)为自下而上阶段,完成合并段的递归推导;(D)到(F)为自顶向下阶段,确定每个内部节点的精确定位。

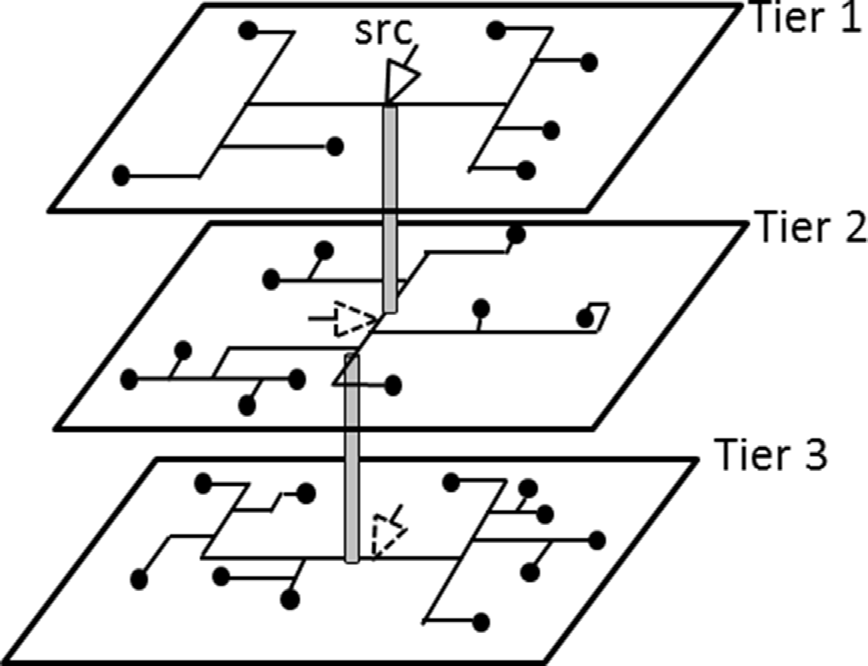

15.2 全局三维时钟分配网络

已为二维电路开发了多种时钟网络拓扑。这些拓扑可以是对称的,例如H型和X型树;也可以是高度非对称的,例如缓冲树和蛇形结构[575,583],以及网格状结构,例如环形结构和网状结构[587]。时钟分配网络通常由一个全局网络和多个较小的局部网络构成。在全局时钟网络中,时钟信号被分发到电路中的特定位置。这些位置是局部网络的源,将时钟信号传递给寄存器或其他电路元件。

对称结构(例如H树)通常用于全局时钟网络[583],,如图15.7所示。对称结构最吸引人的特点是,时钟信号理想情况下会同时到达时钟树的每个叶节点。

然而,为了保持对称性,所经过的距离与最小长度树相比显著更长。由于在千兆赫兹频率下运行的全局时钟网络中的互连非常长,时钟网络通常被建模为传输线,因为可能会出现电感行为[588]。电感行为可能导致分支点处产生多次反射,直接影响时钟网络的性能和功耗。为了减少H树分支点处的反射,在每个分支点处将线段的互连宽度减半(线宽变化23),以确保该分支点处看到的总阻抗保持恒定(阻抗匹配)。

然而,由于负载不平衡、工艺变化和串扰等多种原因,对称树中不同时钟信号在各个位置的到达时间可能不同,从而产生时钟偏斜。为了缓解这种情况,通常采用H树和网格的组合,如图15.8[587]所示。这些网络在三维电路中有多种实现方式。双层电路的一种直接扩展如图15.9所示。两者均

图15.7 二维四级H树

图15.8 驱动网格的缓冲且对称的时钟树,其中每个单元网格构成一个局部时钟网络,被建模为集总电容Cl_seg。

这些拓扑结构包含两个H树,但这些拓扑结构的行为却大不相同。如图15.9A所示的网络仅使用一个H树网络为两层提供时钟信号。时钟信号通过连接至上层H树叶节点的硅通孔传递到下层。下层的局部时钟网络以这些硅通孔为根节点,将时钟信号分发到该层的时钟引脚。用虚线表示的H树仅用于键合前测试,在两层键合后即被断开。因此,这种拓扑结构存在一定的冗余,但在正常的键合后操作中所需的布线远少于

图15.9 基于平面对称H树的全局三维时钟分配网络,在正常操作期间,(A) 一个H树和多个硅通孔分发时钟信号,以及(B) 两个H树和一个根硅通孔分发时钟信号。

如图15.8所示的拓扑结构。实际上,图15.9B中所示的拓扑结构在正常(键合后)操作期间需要在两层中均布置两个完整的H树,导致功耗更高。一组硅通孔(类似于垂直主干)连接了两个H树的根节点,通常可简化整个堆叠中的时钟分配。

两种拓扑结构之间的另一个区别在于驱动时钟负载的时钟缓冲器的数量和尺寸。如图15.9A所示,由于时钟负载由单层内的网络驱动,因此使用的时钟缓冲器数量更多且尺寸更大,相比之下,图15.9B所示拓扑结构中每一层的时钟缓冲器数量和尺寸则较小。请注意,图15.9B所示网络的缓冲器总数可能更大。将这些拓扑结构扩展到更多层时,这种权衡会更加明显。需要更多的缓冲器来通过仅在其中一层连接到H树叶节点的堆叠硅通孔驱动所有层中的时钟负载。或者,如图15.9B所示,在所有层中复制H树是一种合理的方法,因为它使用的硅通孔更少。然而,这种拓扑结构所需的大量布线可能会成为限制因素。另一个重要问题是这两种拓扑结构对工艺变化的鲁棒性,以及更广泛地说,三维时钟网络对工艺变化的鲁棒性。

此问题将在第17章《三维集成电路中的变异问题》中讨论。

一种对工艺变化和负载不平衡更具鲁棒性的替代拓扑结构是树形与网格的结合,如图15.8所示。在一个案例研究中,已探讨了将整个层专门用于时钟电路和全局网络的方案[589]。

将时钟传输任务从逻辑电路中分离出来,为独立优化时钟网络以及生成时钟信号的相关电路提供了机会。

关键思想是在每一层内放置一个网格,并通过硅通孔将全局对称树(例如H树)连接到这些网格以驱动它们。该专用时钟层位于三维堆叠的中间位置,以实现对称性,如图15.10所示,适用于跨越四个逻辑层的网络。在此配置中,时钟层从两面与其他层相连,这意味着需要同时使用面对面到背面对接和面对面互连。这两种键合方式之间的层间互连不同(例如微凸点与硅通孔),这一问题在设计过程中需要予以考虑。

为了评估该方法的性能,已在三维系统[590]中部署了Alpha 21264处理器。该处理器的二维布局被划分为多个象限,每个象限放置在一个物理层上,形成包含专用时钟层的五层堆叠。缓存位于

图15.10 包含一个专用时钟层和四个逻辑层的五层三维堆叠的横截面[589]。

分为两层,整数单元和浮点单元分别放置在两个独立的层上。指令取指单元在其中一个缓存层和包含浮点单元的层之间共享。尽管该布局规划较为粗略,但它为评估时钟层的性能提供了一个合理的测试案例。每一层的电容被估算并分配到每个网格单元,其中时钟网格的粒度为Lseg = 100 µm。时钟缓冲器以Lbuf = 300 µm的间隔插入(参见图15.8)。

基于该划分方案,微处理器的平面布局规划采用树状与网格相结合的网络结构驱动,电路所占面积显著减小。具体而言,二维处理器中时钟网格的面积为2.5 mm × 2.5 mm,而在三维处理器中由于使用了四层结构,该面积减少至1.25 mm × 1.25 mm。面积的减小导致末级缓冲器数量减少,其数量从81个降至25个。这些缓冲器驱动所有四层中的网格,总网格面积与二维情况相近,因为初始的平面布局被“折叠”形成三维结构。因此,二维系统中这些缓冲器的尺寸是三维系统的两倍。然而,由于缓冲器总数以及时钟树在逻辑层内驱动网格的面积均有所减少,时钟网络的功耗也随之降低。对于32 nm工艺节点[252],,平面系统和三维系统的最大偏斜及时钟网络功耗如表15.1所示。

时钟网络的更小尺寸和更少的缓冲器使偏斜和功率降低了15%到20%。

这种全局时钟分配网络的缺点是需要为时钟电路和网络提供一个专用层。该方法会遇到与图15.9A所示拓扑结构相同的键合前测试相关困难。因此,一种更实用的方法是将每一层中的时钟树与网格相结合,并共享一个公共时钟源[591]。在图15.11中,展示了一个双层三维电路同步系统的基本元件。在键合之前提供外部参考时钟给时钟生成电路。键合之后,二级中的三态多路复用器断开层内锁相环(PLL),并选择一级中PLL的输出。在这种配置下,两个网络均由单个PLL驱动,并在全局树的根节点处连接。二级中的相位检测器和延迟锁定环确保两层内的时钟信号时间对齐。两层之间的时钟偏斜主要取决于工艺变化和延迟锁定环的带宽[591]。

一种可抑制因工艺变化引起的额外偏斜的替代方法是增加两层时钟网络之间的连接数量。

采用这种拓扑结构,可以移除时钟相位对齐电路,从而简化时钟电路。此外,由于时钟网络之间有更多的节点被短接,工艺变化得以补偿,从而降低整体层间偏斜。有趣的是,功耗并未下降,这在原理上是违反直觉的。这种矛盾行为的原因在于,每个TSV都使用了静电放电(ESD)二极管以在制造过程中保护驱动电路,这显著增加了提供时钟信号的整体功耗。该方法的另一个缺点是,网络的物理设计受到限制,必须在短接点提供适当的硅通孔连接。

这些拓扑已在eDRAM上进行了评估。测试电路采用IBM 45纳米绝缘体上硅(SOI)技术,尺寸为5.6 mm × 10.9 mm[592],工作频率为2.5吉赫兹。硅通孔短接仅增加1%的功耗开销,但由于ESD二极管的电容负载带来的开销使功耗增加了10%至30%[591]。角点分析还表明,当两层均处于典型工艺角且采用短接网格的方法时,其时钟偏斜比两层处于不同工艺角(例如快‐慢)的情况下的时钟偏斜低一倍[591]。

这些结果不仅表明了选择适当数量的硅通孔以管理偏斜的重要作用,还显示了工艺变化在三维集成电路中的重要性,其中两者均

| 表15.1 二维与四层三维时钟偏斜和功耗比较 | ||||

|---|---|---|---|---|

| 带专用时钟层的微处理器 [589] | ||||

| 布局规划 | 偏斜(皮秒) | 功率(瓦特) | 切片1 | 2-D |

| 9.86 | 3.15 | 3-D | 7.9 | |

| 2.67 | 切片2 | 2-D | ||

| 3.04 | 3.04 | 3-D | 2.51 | |

| 2.51 |

在确定三维时钟网络的性能时,必须考虑层间和层内变化。由于此问题的重要性,工艺和环境变化对全局时钟分配网络设计的影响在第17章“三维集成电路中的变化性问题”中进行了讨论。

作为本节的最后说明,请注意,后续章节讨论的现有时钟综合技术尚未充分研究此问题。因此,在三维CTS方面,仍需大量努力以进一步改进现有技术。

图15.11 两个时钟传输网络,(A) 网络仅在时钟分配的初始阶段被短接,(B) 硅通孔在时钟网络层次结构的较低层级连接时钟网络 [591]。

CHAPTER 15 三维集成电路中的同步

15.3 三维时钟分配网络综合

与之前讨论的技术类似,针对三维电路的其他物理设计问题(如布局规划、平面CTS方法)也已进行了调整,以应对此类系统的多层特性和垂直连接。大多数三维CTS算法包含两个主要阶段。在第一阶段,采用经过适当修改的MMM算法(如第15.1节中所述),为位于多个层上的时钟汇点生成连接拓扑结构。根据综合技术的目标不同,已开发出该拓扑生成算法的多种变体。在第二阶段,经过适当调整后,采用另一种常用技术DME(也在第15.1节中讨论过),将三维连接拓扑嵌入到多层堆栈中。

三维CTS方法的多样性可归因于不同的性能目标以及过去几年中这些方法的演变[593–598]。

如表15.2所列,三维CTS技术生成的时钟网络除了满足零(或接近零)偏斜和(近)最小线长外,还需满足多个目标。一个重要目标是降低三维时钟树消耗的功率,正如多项研究报道的那样 [593–597],这需要在硅通孔数量、三维树的线长以及硅通孔电容之间进行若干权衡。

考虑到全局拓扑结构以及图15.9中所示的结构,观察到类似的权衡:多硅通孔时钟树通常比单硅通孔时钟树消耗更少的功率。如果硅通孔电容较高,则限制三维时钟树中的硅通孔数量不会增加功耗,因为水平互连的较低电容所带来的节省可以抵消硅通孔电容负载的影响。

此外,键合前测试已被证明是提高三维系统良率的有效手段[599],但其对时钟综合过程提出了不同的要求,这种情况在三维系统中是独有的。为了更好地理解键合前测试为时钟综合过程带来的额外复杂度,考虑图15.12所示的具有多个汇点和多硅通孔拓扑结构的双层时钟树示例。

| 表15.2 三维电路的CTS方法及每种方法满足的相关目标 | |||||||||

|---|---|---|---|---|---|---|---|---|---|

| 技术 | CTS | 技术 | 目标/约束 | Zero Skew | 时钟 | Slew | 功率 | 数量 | 硅通孔数量 |

| ü | ü | ü | ü | û | ü | ||||

| ü | ü | ü | ü | û | û | ||||

| ü | ü | ü | ü | ü | ü | ||||

| ü | ü | ü | ü | ü | ü | ||||

| ü | ü | ü | ü | û | ü | ||||

| ü | û | û | û | û | ü | û | ü | ||

| [593] | ü | ü | ü | ü | û | ü | û | û | |

| [594] | ü | ü | ü | ü | û | û | û | û | |

| [595] | ü | ü | ü | ü | ü | ü | û | û | |

| [596] | ü | ü | ü | ü | ü | ü | û | û | |

| [597] | ü | ü | ü | ü | û | ü | ü | û | |

| [598] | ü | û | û | û | û | ü | û | ü |

为提高可读性,本文所采用的技术命名约定与原始源出版物中的命名约定不同。

二级中的汇点形成三个互不相连的子树,并与一级中的子树连接,构成一个连接全部13个汇点的三维树。为了支持双层的键合前测试,任一层都应存在时钟树,并且相较于键合双层系统中的全连接时钟树,需满足所有目标。除非在二级中使用冗余网络,否则所示拓扑无法满足此要求。该冗余网络应确保保持与键合后三维树相同的时钟偏斜和压摆率。此外,对一级的键合前测试不需要冗余树;但由于时钟负载不同于完整时钟树,时钟网络的特性也有所不同。已开发出考虑此情况的时钟综合技术,这些技术考虑了布线和位置放置障碍[600]以及在可用空白区域内的硅通孔位置放置。

在时钟树综合过程中考虑的另一个问题是容错性。由于硅通孔可能受到制造或装配缺陷的影响,[601],容错性是一个重要问题。

几种时钟综合方法的特点总结于表15.2中,其中列出了每种技术所针对的不同目标。在接下来的小节中,由于方法和资源的不同,将分别描述包含和不包含键合前测试的技术。

15.3.1 标准综合技术

经典综合技术在二维时钟树中的应用讨论见于第15.1节。这些方法可用于生成三维电路的时钟树,前提是每一层包含一棵连接该层内所有时钟汇点的树。所有这些树的根节点通过单个垂直连接(例如,多个并联的硅通孔)相连,从而构成覆盖整个三维电路的完整树结构。然而,这种单硅通孔拓扑是一种相当幼稚的方法,因为第三维度的优势未能得到充分挖掘。因此,多硅通孔拓扑是一种更优方法,可显著减少线长,通常意味着更低功耗。[593]

三维时钟综合问题已有多种建模方式,其主要目标是为一组跨越多个物理层的时钟汇点 $S = {s_1; s_2; s_3; … s_m} \subset \mathbb{R}^3$ 构建一棵具有最小(或接近最小)线长和/或功率、且使用最少[594]或有限数量的硅通孔[593]的零偏移多硅通孔树。这些时钟汇点的位置由坐标三元组 $(x_i, y_i, z_i)$ 描述,其中 $z_i$ 表示 $s_i$ 所在的层。此外,压摆率应满足一个目标约束,通常小于时钟周期的5%。

多硅通孔时钟树综合技术分为两个阶段进行。首先生成连接三维系统中所有层的时钟汇点的拓扑结构,然后进行扩展

图15.12 跨越两层的多TSV时钟树,包含13个汇点和三个硅通孔

DME方法用于在整个三维系统的层中嵌入拓扑结构。拓扑生成扩展了传统的MMM算法。如第15.1节所述,MMM算法通过使用x‐或y‐切割对一组时钟汇点进行递归二分划分,直到每个集合仅包含一个汇点。在三维电路中,由一次切割产生的子集中的时钟汇点位于不同的层中,这些汇点通过硅通孔相连。此外,z‐切割以多种方式对S进行划分,从而导致对硅通孔的不同需求。

因此,经典的MMM算法对硅通孔不敏感,这可能导致不良情况:要么因硅通孔使用不足而无法有效减少总线长,要么因过度使用硅通孔而导致功耗节省降低(甚至增加)。为解决这些问题,已对MMM算法进行了扩展,以控制综合树状拓扑[593,594]所需的硅通孔数量。

MMM‐TSV‐Bound算法(称为MMM‐TB)根据满足用户指定的硅通孔数量上限来生成拓扑结构。硅通孔分布在各层的面积上[593]。不同硅通孔数量限制对所生成拓扑结构的影响示例如图15.13所示。从该图中可以观察到,对于较大的硅通孔数量限制,会使用更多的硅通孔,这些硅通孔更靠近连接较少内部节点和/或汇点的那些汇点。这种行为减少了总线长,因为水平互连更短。MMM‐TB算法从一组汇点S以及三维系统中每一层的硅通孔限制开始。如果stack(S)表示跨越S中汇点的层数,则在每次划分迭代中,基于两个条件生成两组S1和S2。

如果硅通孔限制为1,则需对现有集合S进行划分,以确保具有相同zi(即来自同一层)的汇点被分配到同一子集。只要stack(S)=2,这种划分就很简单。然而,如果汇点跨越超过两层,并且由于切割会对集合S进行二分划分,因此需要进行(stack(S) − 1)次迭代,将汇点沿z方向进行划分,以确保汇点

图15.13 MMM‐TB算法针对不同硅通孔数量边界为八个汇点生成的若干抽象树,(A) 为这些树的二维视图,虚线表示硅通孔,(B) 为相同树的三维视图,(C) 为得到的连接拓扑,其中灰色矩形表示硅通孔 [593]。

相同的 $z_i$ 位于同一层。该过程如图15.14所示,展示了在MMM‐TB算法的特定迭代中,汇点集合z-方向上的划分发生过程。在此图中,$z_{min}$ ($z_{max}$)是包含集合S汇点的层的最低(最高)索引。此外,假设时钟树的根节点位于 $z_r$。层的索引从底层到最上层按升序进行。

如图15.14所示,如果 $z_r \leq z_{min}$,这意味着根节点位于集合S中任意汇点的下层,则所有满足 $z_i = z_{min}$ 的汇点构成(底部)子集SB,其余汇点(例如,$z_i \in [z_{min}+1, z_{max}]$)构成(顶部)子集ST。或者,如果 $z_r \geq z_{max}$,这意味着根节点位于集合S中任意汇点的上层,则所有满足 $z_i = z_{max}$ 的汇点构成(顶部)子集ST,其余汇点(例如,$z_i \in [z_{min}, z_{max}-1]$)构成(底部)子集SB。

在其他任何情况下,(顶部)子集ST包含与树的根节点处于同一层的那些汇点,而(底部)子集SB包含位于其他层的剩余汇点。图15.15展示了对一个小集合 $S={a, b, c}$ 执行此过程的一个示例,其中不同z切割产生的硅通孔数量由粗线段表示。

在第二种情况下,当硅通孔限制大于一时,如同MMM中那样,对汇点的x或y坐标的中位数沿水平方向进行切割,并且不考虑z维度。如果这些子集中包含具有不同z坐标的汇点,则所得到的子集需要多个硅通孔。在每次划分步骤结束时,会为每个子集分配一个新的硅通孔限制,以确保维持硅通孔限制。该新的硅通孔限制是通过估计新形成子集所需的硅通孔数量并将原限制除以估计的硅通孔数量来确定的。硅通孔数量的估计值由水平切割后每层中最小的汇点数量决定。MMM‐TB算法的复杂度与MMM相同,均为 $O(m \log m)$。

MMM‐TB算法可确保硅通孔数量不超过硅通孔限制。只要满足该限制,即可使用任意数量的硅通孔。硅通孔数量会显著影响总线长,从而影响时钟网络消耗的功率。采用穷举扫描来确定最优的硅通孔数量。然而,这种方法

Z切割(集合 S,子集 ST,子集 SB)

设置 S={s1, s2,...,sk},根层索引 zr

子集 ST和 SB

1: zmin= min(z1,..., zi,...,zk), si=(xi, yi,zi) ∈ S

2: zmax= max(z1,..., zi,...,zk), si=(xi, yi,zi) ∈ S

3:如果 (zr ≤ zmin) 那么

4: ST={s1,..., si,...,sk1), zi ∈ [zmin+1, zmax]}

5: SB={sk1+1,..., sj,...,sk), zj= zmin

6:否则如果 (zr ≥ zmax)那么

7: ST={s1,..., si,...,sk1), zi= zmax

8: SB={sk1+1,..., sj,...,sk), zj ∈ [zmin, zmax-1]}

9: else

10: ST={s1,..., si,...,sk1), zi= zr

11: SB={sk1+1,..., sj,...,sk), zj ≠ zr

图15.14 MMM‐TB算法的z‐cut过程伪代码 [593]

计算成本较高,特别是对于较大的硅通孔数量限制。MMM‐TB 可进一步增强,以根据功率确定最优的硅通孔数量。需要注意的是,如果硅通孔的电容较高,那么即使水平线长减少带来了功耗节约,使用尽可能多的硅通孔也可能不会带来最低的功耗,因为这一特性可能对功耗节约产生不利影响。为了确定硅通孔数量,采用类似于 [578] 中使用的前瞻操作 [593]。

这些操作包括:(a) 先进行 Z切割,然后进行 xy切割;(b) 先进行 xy切割,然后进行 Z切割。

比较 (a) 和 (b) 两种情况下新形成的质心之间的距离。在两种情况下均应用一个成本函数,该函数将生成的硅通孔数量和线长与功耗估计相关联。在下一次迭代中选择能够产生较低功耗估计值的操作序列。

综合过程的第二阶段是DME方法的一种变体,经过调整以考虑硅通孔和压摆率约束。为了满足压摆率约束,通常的做法是不允许树中任何节点所看到的电容超过特定限制 $C_{max}$[602]。

通过添加时钟缓冲器来确保这些缓冲器所承受的负载低于 $C_{max}$,从而满足该约束。在DME方法的自底向上遍历中(参见第15.1节),基于埃尔莫尔延迟计算出的合并段,也会在内部节点的下游电容超过 $C_{max}$ 时为缓冲器确定。在自顶向下阶段,DME被扩展以评估合并类型(例如,内部节点与子树根节点处的缓冲器合并,或内部节点与子节点的标准合并),并确定内部节点和缓冲器的位置放置。当缓冲器插入与DME方法结合时,图15.16展示了遇到的两种不同合并类型的示例。图15.16。

将MMM‐TB算法与集成缓冲器插入和DME技术应用于多个基准测试[603]表明,对于双层电路,与TSV电容分别为15、50和100飞法的单个TSV时钟网络相比,多硅通孔时钟树可显著降低功耗,降幅分别为16.1%至18.8%、10.3%至13.7%以及6.6%至8.3%。相应的总线长减少分别为24.0%至26.5%、23.9%至26.6%以及16.6%至18.9%。多硅通孔时钟树的另一个优势是由于线长减少,平均压摆率和斜率分布得到了更好的控制。尽管

图15.15 一组汇点S={a, b, c},用于示例MMM‐TB算法中递归z切割的效果。(A) 连续应用两次z切割,(B) 源位于 Tier 3层,并依次进行z‐cut1和z‐cut2,,(C) 源位于二级层,且该层中的汇点首先被提取,(D) 源位于一级层,并依次进行z‐cut2和z‐cut1。

MMM‐TB算法与DME方法的结合可生成高效的多硅通孔时钟树,而其他MMM和DME方法的变体在无缓冲时钟树上表现出更大的线长缩减,下文将介绍这些变体以提供更深入的见解。

15.3.1.1 综合时钟树中硅通孔的进一步减少

在三个物理维度中,对MMM的一种简单扩展被称为MMM半周长线长(HPWL),该方法在[594],中提出,其中用户定义的参数 ρ(0 ≤ ρ ≤ 1)决定切割的方向。如果 ρ = 0,则采用标准MMM算法,并忽略z维度。或者,如果 ρ = 1,则将汇点在组成三维电路的各层之间进行划分,并对每层生成的子集使用xy切割方式执行二分划分,如同MMM中一样。对于任何其他 ρ值,则在二维曼哈顿平面内沿几何中位数执行水平切割。然后计算这些汇点子集的HPWL。

如果某个汇点子集的HPWL小于所有汇点总HPWL的 ρ×,则将汇点在各层之间进行划分(即进行Z切割),而不是在xy方向上切割。这一条件与MMM‐TB算法中的某些概念相似,在MMM‐TB算法中,使用硅通孔限制来确定汇点划分的方向。此外,在MMM‐TB算法中,限制硅通孔数量并不能保证总垂直线长最小化。

MMM‐TB算法提供了在递归自上而下划分过程中连接汇点所需的硅通孔数量。然而,硅通孔的使用还取决于连接拓扑结构中T(S)内部节点所处的层。但该信息并非由MMM‐TB算法确定。此外,标准DME技术应用于一个二维平面,其中汇点被投影到该平面上,且并未最小化硅通孔数量。

为了说明树拓扑中内部节点的不同位置放置可能导致硅通孔数量的差异,考虑图15.17所示的示例。根据节点 x1, x2, 和根节点 sr 的位置放置,双层树的硅通孔数量可能会显著不同,如图15.17所示。本示例表明,在情况 (A) 和 (H) 中嵌入各层节点可得到最少的硅通孔数量。

一种通过嵌入各层以确保最小垂直长度的算法在 [594] 中给出。三维时钟树的垂直长度为

$$

L_v^{\text{total}} = \sum_{(i,j) \in G(S)} L_{\text{TSV}} |z_i - z_j|; \quad (15.11)

$$

其中 $L_{\text{TSV}}$ 是连接相邻层的一个硅通孔的长度,且求和适用于树T(S)连接拓扑内每一对节点。任何位于同一层内的节点对不贡献垂直线长,因为 $z_i = z_j$。为了确定T(S)中节点i的硅通孔数量,进而计算垂直线长,使用以下表达式

$$

n_{\text{TSV}}(i) =

\begin{cases}

0, & \text{if } i \text{ is a sink node;} \

n_{\text{TSV}}(T_{\text{left}}(i)) + n_{\text{TSV}}(T_{\text{right}}(i)) + n_{\text{TSV}}(i, T_{\text{left}}(i)) + n_{\text{TSV}}(i, T_{\text{right}}(i)), & \text{if } i \text{ is an internal node;}

\end{cases} \quad (15.12a-b)

$$

其中,$n_{\text{TSV}}(T_{\text{left}}(i))$ 和 $n_{\text{TSV}}(T_{\text{right}}(i))$ 分别表示以节点i的子节点为根的子树中包含的硅通孔数量,而 $n_{\text{TSV}}(i, T_{\text{left}}(i))$ 和 $n_{\text{TSV}}(i, T_{\text{right}}(i))$ 分别表示连接节点i与子树 $T_{\text{left}}(i)$ 和 $T_{\text{right}}(i)$ 的硅通孔数量。

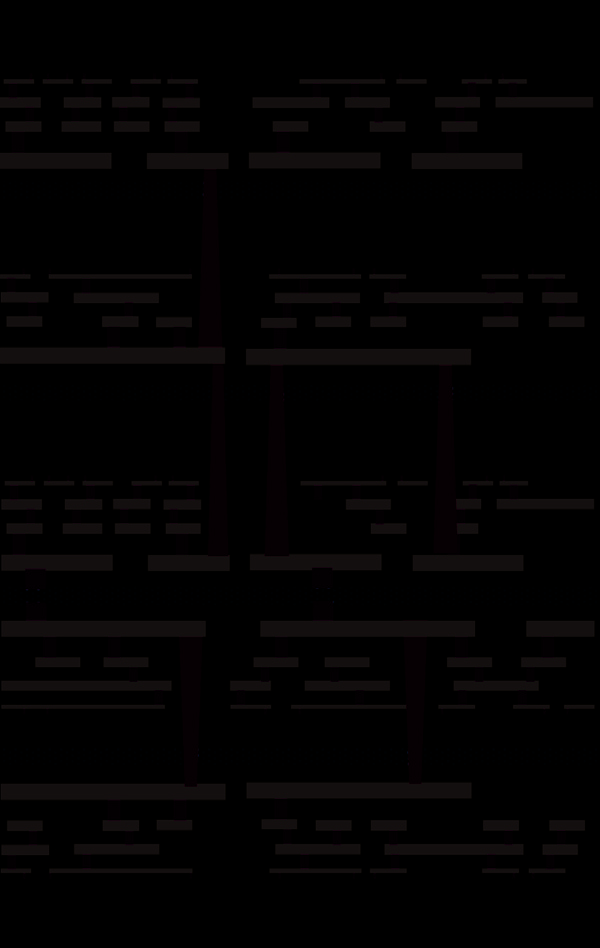

如果节点i的子节点是汇点,且汇点的位置已知,则用于确保由子节点所在层决定TSV最小数量的节点i可嵌入的层记为ET(i)。然而,如果子节点是内部节点,则这些节点的嵌入层为若干嵌入层的集合。在这种情况下,可以从这些嵌入层集合中确定出使该节点i的硅通孔数量 $n_{\text{TSV}}(i)$ 最少的一组层ET(i)。图15.18展示了基于子节点x1和x2的嵌入层来嵌入内部节点x的一个示例。如果子节点是汇点,即 $x_1=s_1$ 和 $x_2=s_2$,则在节点x处合并这些节点所需的垂直连接长度为 $|t_2 - t_1|$,其中 $t_2=z_2$ 和 $t_1=z_1$ 为汇点的层,如图15.18A所示。

如果子节点也是内部节点,则可以区分两种情况。如果嵌入层 $ET(x_1)$ 和 $ET(x_2)$ 具有一些公共层,那么将这些节点与节点x合并所需的最小垂直长度为 $n_{\text{TSV}}(T_{\text{left}}(x)) + n_{\text{TSV}}(T_{\text{right}}(x))$,且该节点的嵌入层位于层 $t_2$ 和 $t_3$ 之间,如图15.18C所示。选择其他任意层来嵌入x都会导致 $n_{\text{TSV}}(x)$ 增加,如图15.18D所示。在第二种情况下,当子节点 $x_1$ 和 $x_2$ 的嵌入层集合没有共享任何公共嵌入层时,如图15.18E所示,节点x被嵌入在层 $t_2$ 和 $t_3$ 之间。这两种情况之间的差异,如

图15.16 两个层间节点 u,v 与节点 p 合并的合并段示例。(A) 一个无缓冲的树,(B) 一个有缓冲的树。

图15.17 具有四个汇点嵌入两层的树,针对内部节点x1和x2以及根节点sr的不同嵌入情况,以及每种情况下所需的硅通孔数量。符号xi,j(si,j)表示将节点xi(si)放置在第j层。(A) 硅通孔数量为2,(B) 硅通孔数量为3,(C) 硅通孔数量为3,(D) 硅通孔数量为4,(E) 硅通孔数量为4,(F) 硅通孔数量为3,(G) 硅通孔数量为3,(H) 硅通孔数量为2。

图15.18 确定节点x的嵌入层数量的不同情况,其中子节点x1和x2为(A)时钟汇点,而(C)和(E)为内部节点。(B)、(D)和(F)中分别显示了(A)、(C)和(E)的TSV的最小数量[594]。

如图15.18C和15.18E所示,子节点存在一个共同的嵌入层,在图15.18C中,因此与节点x合并不需要硅通孔。然而,如图15.18E所示,$|t_3 - t_2| > 1$,且至少需要一个硅通孔来嵌入节点x。

内部节点的嵌入层集合(由(15.12a)要求)通过自底向上过程迭代确定[594],

$$

ET(x) = [\min(t_1, t_2), \max(t_1, t_2)]; \quad (15.13)

$$

其中

$$

t_1 = \max(\min(ET(T_{\text{left}}(x))), \min(ET(T_{\text{right}}(x)))); \quad (15.14)

$$

and

$$

t_2 = \min(\max(ET(T_{\text{left}}(x))), \max(ET(T_{\text{right}}(x)))); \quad (15.15)

$$

这些表达式的最优性已通过一系列引理[594]得到证明。将树的节点进行嵌入以确保采用最小垂直长度的过程具有 $O(m)$ 的复杂度,其中m是树T(S)的节点数量。

一旦确定了树中节点的嵌入层,树节点的位置放置将基于DME技术进行,其中采用埃尔莫尔或线性延迟模型。在线性延迟模型中,由于硅通孔与水平导线的电容不同,因此对硅通孔采用不同的建模方式。与将DME技术应用于具有线性延迟模型的二维时钟树类似,该方法同样可为三维时钟树实现零偏斜和最小线长。然而情况更为复杂,因为在ea和eb处对于合并节点a和b(参见第15.1节)使用的是埃尔莫尔延迟。这种方法可能因在合并段上缺乏特定位置来平衡从合并节点x到子树Ta和Tb根节点的延迟而导致次优线长。这种行为需要走线蛇形化,从而导致偏离最小线长的绕行。

15.3.2 可预键合测试的三维时钟树综合技术

先前讨论的综合技术可为任意数量的层生成三维时钟树,但存在限制其可用性的缺点。由于键合前测试能够保证三维系统的高良率,因此在堆叠组装之前,必须验证每一层的正确功能和预期性能。这一要求对三维系统的设计施加了相当大的约束。有关三维电路的预键合测试方法,参见[605]。对于时钟树的设计,必须进行特定修改以提供键合前测试。与CTS技术相关的键合前测试的根本区别在于附加电路。本节将介绍这些技术的显著特征。

一种提供可在键合前进行测试的三维时钟分配网络的方法是采用单个TSV拓扑,例如如图15.19所示,这些拓扑在三维系统的每一层中包含完全连接树。每一层的一个时钟输入为该层内的所有时钟引脚提供时钟信号。然而,这种方法相较于二维电路仅带来较小改进,降低了三维集成的优势。相反,采用支持预键合测试的多硅通孔时钟网络更为有利。主要挑战在于多硅通孔拓扑。

图15.19 使用单个TSV实现层间连接的三层时钟树。该拓扑结构是可预键合测试的,因为每一层都包含一个连接所有汇点的网络。

通常只有一层包含一个完全连接的树(通常是主时钟驱动器所在的层),而其他层则由多个子树组成,这些子树通过硅通孔与完整的树相连。然而,在键合前测试操作期间,这些子树彼此之间是断开连接的。在键合之前,需要相当数量的时钟输入来驱动这些断开的子树,这使得测试过程更加复杂并增加了代价。

此外,即使对于包含全连接时钟网络的层,测试也不是一个简单的过程,因为该网络驱动整个时钟负载。在键合前测试期间,只有部分负载存在,这意味着时钟偏斜和压摆率可能与正常操作期间的目标偏斜和压摆率显著偏离。因此,该网络可能导致多种时序违规,这些违规可能会被错误地解释为故障。为了缓解这种情况,采取了两种措施:(1)在每个连接到硅通孔的完整网络节点处插入缓冲器;(2)添加适当数量的冗余网络,在键合前测试期间将一层的局部树相互连接。在正常操作期间,即键合后,这些冗余树会从其余时钟网络断开 [606]。措施(1)中的缓冲器插入使全连接树与网络其余部分解耦。因此,该时钟树每个节点的电容在键合前后操作期间保持不变。

一个可键合前测试的时钟树在两层中的示例如图15.20所示。该图中用虚线标出了硅通孔之前的缓冲器、冗余树以及在正常操作期间断开该树的传输门(TGs)。另请注意,该结构需要一个额外的控制信号来切换二级中的传输门。

在描述了可预键合测试时钟网络的特性之后,综合问题被表述如下:对于分布在 n 层上的汇点集合 $S = {s_1; s_2; s_3; … s_m} \subset \mathbb{R}^3$、一个根节点 $s_r$ 以及硅通孔限制,需综合出一个三维时钟网络,使其在键合后(整个堆栈)和键合前(每一层)均具有最小或零时钟偏斜。同时,在满足时钟转换速率约束的前提下,最小化该三维时钟网络的线长和功率。

采用上一节所述的MMM‐TB方法,为S的汇点生成连接拓扑结构,记为T(S)。

MMM‐TB方法生成的拓扑结构中,汇点与源位于同一层,称为源层。这些汇点通过一棵树进行连接。到其他层的连接通过硅通孔实现。为了将这些层中的子树与源层中的网络解耦,遵循以下步骤[596]:(1)如果一个硅通孔连接源层与其他层,则在源层插入一个TSV缓冲器;(2)如果三维时钟树中的两个节点通过穿越源层的硅通孔相连,则在源层添加一个TSV缓冲器;(3)如果一个硅通孔连接两个节点但不穿越源层,则不插入TSV缓冲器。在这种情况下,键合前测试期间该硅通孔的缺失对源层的电容没有影响,因此不需要TSV缓冲器。

综合过程的下一阶段包括一种改进的DME,这是一种两阶段技术。在这种键合前感知时钟树综合(PBA‐CTS)技术中,生成了一棵零偏斜树,该树考虑了来自MMM‐TB算法的连接拓扑中TSV缓冲器和节点的合并段。然而,TSV缓冲器通常需要额外的线长来维持零(或低)偏斜要求[596]。这种情况可能导致最小线长目标无法满足。插入公共时钟缓冲器可以避免这种情况。考虑图15.21中所示的例子,其中两个子树ST1和ST2,分别位于第一层和第二层。

由于这些树位于不同的层上,因此使用一个TSV缓冲器来合并这些子树。该TSV缓冲器增加了从节点E到ST2的延迟。如果此延迟远大于在插入TSV缓冲器之前从E到ST1,的延迟,则该延迟会增加。为了保持零偏斜目标而添加走线“蛇形化”,但这背离了最小线长目标。可以通过插入时钟缓冲器来避免走线蛇形化。案例研究表明,此类不平衡情况很少发生;因此,为此目的使用时钟缓冲器并不是一个重大问题。

在自底向上过程中合并子树时,存在另一个需要添加时钟缓冲器的原因。时钟缓冲器被广泛用于满足压摆率约束。插入这些时钟缓冲器可确保每个时钟缓冲器所驱动的负载不超过下游电容阈值 $C_{max}$[602]。这种做法已被证明能够控制压摆率。对于可预键合测试的三维时钟树,插入时钟和硅通孔缓冲器的示例如图15.22所示。图15.22A展示了简单的情况,当合并分支的延迟严重不平衡时(例如 $t_{dA}$, $t_{dB}$),这种情况在二维和三维(无论是否可预键合测试)综合时钟树中都很常见。图15.22B中,由于导线过长和/或下游电容超过 $C_{max}$,因此使用了多个时钟缓冲器。

图15.20 具有多个硅通孔的键合前可测试时钟树。缓冲器插入在硅通孔之前,从而不改变一级中树的电容。二级中的传输门在键合前测试期间将冗余树(以虚线表示)与子树连接。键合后,传输门被关闭,使冗余树断开。

另一种情况如图15.22C所示,需要添加一个时钟缓冲器以抵消插入TSV缓冲器引起的延迟不平衡。插入TSV缓冲器还会使子树解耦,从而便于键合前测试。

PBA‐CTS方法的输出是一个用于键合后操作的三维时钟树,以及一棵覆盖位于源层上所有时钟汇点的树。对于剩余层,通过冗余树连接这些层中未连接的树来生成类似的树。该过程类似于平面电路的传统CTS技术[596],包括:(1)以自上而下的方式构建二进制连接拓扑T(S),(2)在每个汇节点插入传输门,以及(3)在满足偏斜和最小线长约束条件下将 T(S)嵌入并缓冲到某一层中。需要注意的是,这些层中由冗余树连接的子树的根节点即为汇点。传输门的插入用于连接(键合前操作)或断开

图15.21 由多个子树STi组成的三维时钟树的一部分。(A)中的硅通孔在(B)中被替换为TSV缓冲器,以将一级中的时钟树与第 2[596]层中的时钟树解耦。

图15.22 插入TSV和/或时钟缓冲器的不同情况。(A) 插入一个时钟缓冲器以平衡两个分支之间的延迟,其中 $t_{dA}$, $t_{dB}$,(B) 由于导线较长或下游电容较高而插入多个时钟缓冲器,以及(C) 插入一个TSV缓冲器以解耦下游时钟树,并添加一个时钟缓冲器以补偿由TSV缓冲器引起的延迟不平衡[596]。

(键合后操作)冗余树需要一个跨越该层大部分区域的控制信号。为了限制

3894

3894

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?