FPGA组成结构

博主刚开始接触FPGA时是在大三上EDA实验课,当时就对这种这种芯片的强大好奇,当时实验课用的VHDL语言,当时觉得这种并行的语言很有趣。后续又自学了verilg,从此就迈上了这条不归路,经过几年学习总感觉没啥进步,当初以为自己会用verilog就代表懂了FPGA,对于FPGA结构了解很少。本博文主要介绍FPGA内部组成以及资源。

FPGA内部主要有CLB(可配置逻辑块),IOB(输入输出单元),Block ram,丰富的布局布线资源以及底层嵌入的逻辑支援例如dsp,FIFO等逻辑资源供用。

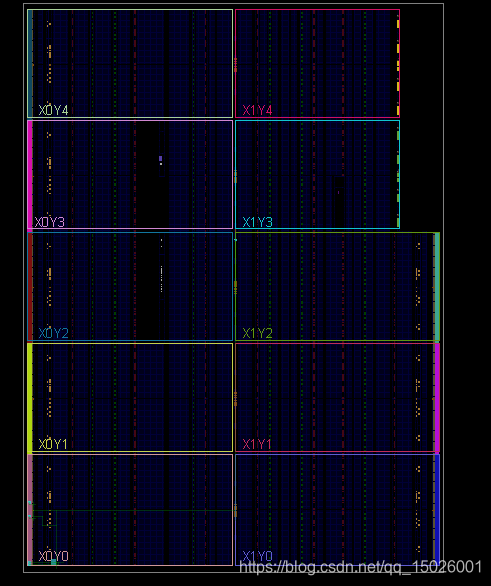

FPGA资源分布图

博主以xilinx的K7系列的一款FPGA为例介绍:

FPGA管脚

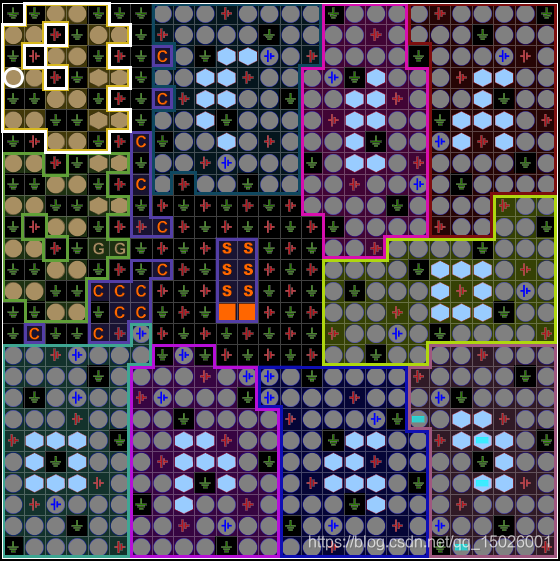

CLB

CLB结构如图

其中CLB又由SLICEL与SLICEM两部分组成,其中这两部分有些许差异,SLICEL通常用来产生时序与组合逻辑,而SLICEM和还可以作为mem,移位寄存

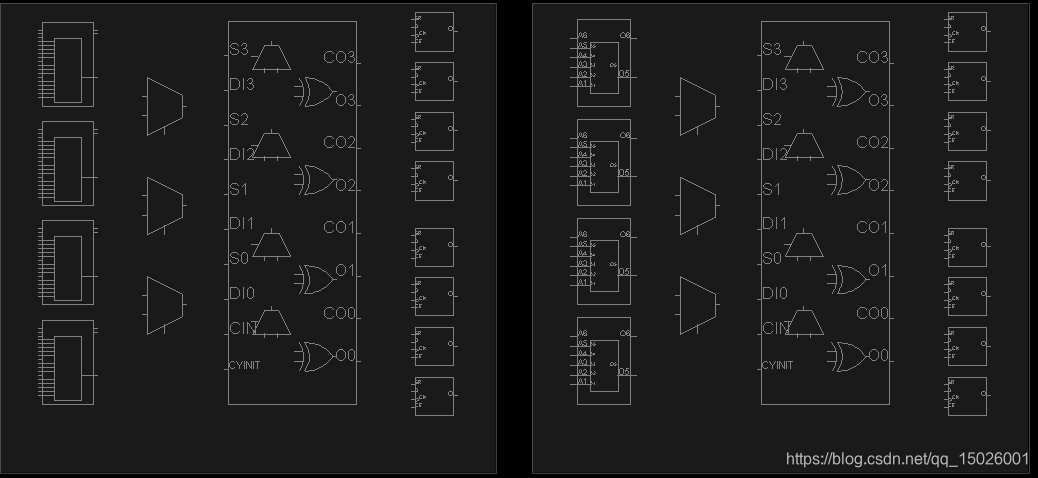

本文深入探讨FPGA的内部组成,包括CLB、触发器、IOB和BRAM等关键资源。CLB由可配置逻辑块构成,触发器分为D触发器和锁存器,IOB是与外部电路交互的接口,BRAM则提供片上存储功能。理解这些底层结构对于优化FPGA设计至关重要。

本文深入探讨FPGA的内部组成,包括CLB、触发器、IOB和BRAM等关键资源。CLB由可配置逻辑块构成,触发器分为D触发器和锁存器,IOB是与外部电路交互的接口,BRAM则提供片上存储功能。理解这些底层结构对于优化FPGA设计至关重要。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?