脉冲同步器

脉冲同步器作用

在实际的电路设计中,设计人员很少遇到单一时钟的同步电路设计,更多的是多时钟域的设计,因此异步电路的设计在实际应用中的重要意义不言而喻。由于信号在不同时钟域之间传输,容易发生亚稳态的问题导致,不同时钟域之间得到的信号不同。处理亚稳态常用打两拍的处理方法。多时钟域的处理方法很多,最有效的方法异步fifo,具体可以参考博主的verilog异步fifo设计,仿真(代码供参考)异步fifo适合处理不同时钟域之间传输的数据组,但有时不同时钟域之间仅仅传递脉冲,异步fifo就显的有点大材小用的,因此单信号的跨时钟域处理通常有,

- 两级寄存器串联。

- 脉冲同步器。

- 结绳法。

- 采用握手。

本博文仅仅对脉冲同步器进行设计

脉冲同步器

由于脉冲在快时钟域传递到慢时钟域时,慢时钟有时无法采样的信号奈奎是特采样定理

因此需要对信号进行处理,可以让慢信号采样到。

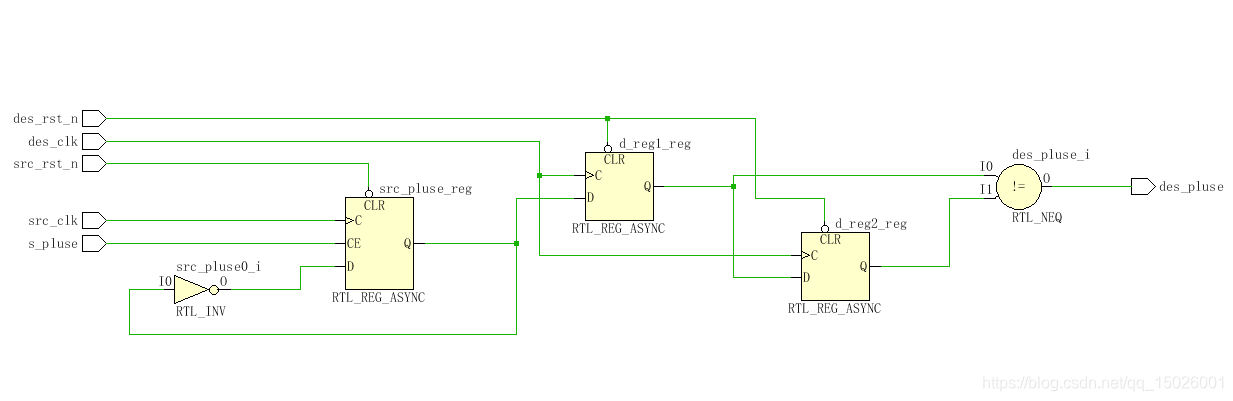

脉冲同步器的结果如图

verilog code

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: zhangsy

//

// Create Date: 2019

本文探讨了在多时钟域设计中脉冲同步器的重要性,以解决信号跨时钟域传输时的亚稳态问题。除了介绍常用的处理方法,如异步FIFO,还重点讲解了脉冲同步器的设计,它能有效确保慢时钟域正确采样脉冲。文章提供Verilog代码及仿真结果展示。

本文探讨了在多时钟域设计中脉冲同步器的重要性,以解决信号跨时钟域传输时的亚稳态问题。除了介绍常用的处理方法,如异步FIFO,还重点讲解了脉冲同步器的设计,它能有效确保慢时钟域正确采样脉冲。文章提供Verilog代码及仿真结果展示。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

653

653

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?