了解以太网 PHY 的各种 MII 接口。

目录

一. 数据接口 MII

1.1 MII

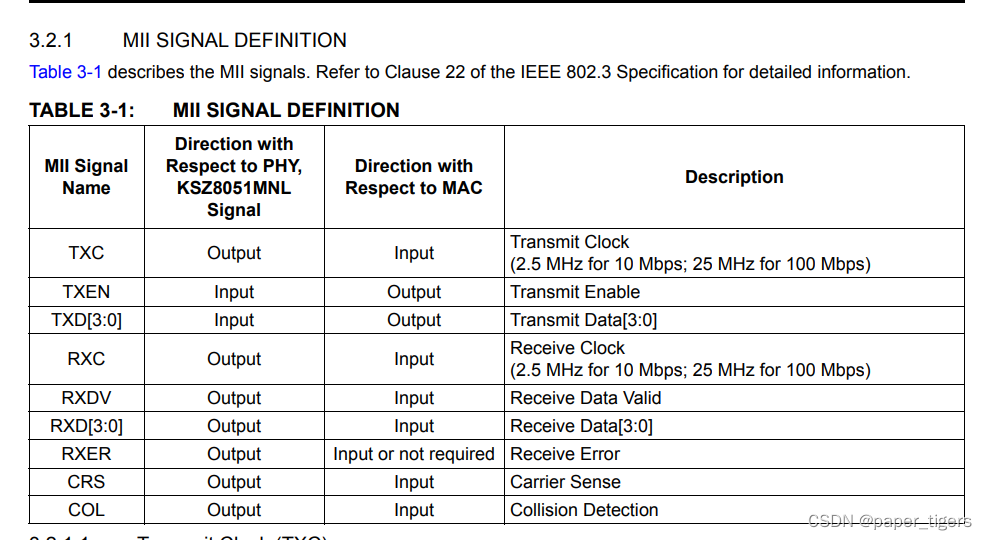

MII 介质独立接口提供 PHY 和 MAC 之间数据的一个访问接口,支持10BASE-Te 和 100BASE-TX 协议。下图以 microchip 的 KSZ8051 为例展示了 MII相关信号。

发送侧TX:

TXC:由 PHY 提供给 MAC 的参考时钟,10Mbps 下是 2.5MHz,100Mbps 下是 25MHz,作为 TXEN 和 4bit TXD 的采样参考时钟。TXEN 为高时标志着 MAC 侧准备发送数据。为低时 PHY 侧忽略TXD 上的数据。

接收侧RX:

RXC:由 PHY 提供给 MAC,作为 RXDV 和 4bit RXD 的采样参考时钟。在 10Mbps 下,当 CRS有效时,RXC 由 RXD 恢复出来,当线路处于 Idle 或者 Link down 时,RXC 由 PHY 的参考时钟提供。是 2.5MHz,100Mbps 下是 25MHz,作为 TXEN 和 4bit TXD 的采样参考时钟。RXDV 为高时标志着 PHY 侧准备发送数据。为低时 PHY 侧忽略TXD 上的数据。

状态信号:

CRS:在 10Mbps 下,当检测到数据帧的前导码 preamble 有效时 PHY侧输出 CRS 为高,检测到数据帧的结束标志 EOL 时,CRS 为低。在 100M

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2586

2586

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?