一、代码实现

`timescale 1ns / 1ns

module decoder_3_8(

input S0 ,

input S1 ,

input S2 ,

output [7:0] out //output reg[7:0] out

);

reg[7:0] r_out ; //利用了always模块,需对输出定义reg类型

assign out = r_out ;//或者直接在输入端定义reg类型

always @(*) begin

case({S2,S1,S0})

3'b000: r_out = 8'b0000_0001; //out = ........

3'b001: r_out = 8'b0000_0010;

3'b010: r_out = 8'b0000_0100;

3'b011: r_out = 8'b0000_1000;

3'b100: r_out = 8'b0001_0000;

3'b101: r_out = 8'b0010_0000;

3'b110: r_out = 8'b0100_0000;

3'b111: r_out = 8'b1000_0000;

default:r_out = 8'b0000_0000;

endcase

end

endmodule

二、仿真

`timescale 1ns / 1ns

module decoder_3_8_tb();

reg S0 ;

reg S1 ;

reg S2 ;

wire[7:0] out ;

decoder_3_8 inst0(

.S0 (S0 ) ,

.S1 (S1 ) ,

.S2 (S2 ) ,

.out(out)

);

initial begin

S0 = 0 ; S1 = 0 ; S2 = 0;

#200

S0 = 1 ; S1 = 0 ; S2 = 0;

#200

S0 = 0 ; S1 = 1 ; S2 = 0;

#200

S0 = 1 ; S1 = 1 ; S2 = 0;

#200

S0 = 0 ; S1 = 0 ; S2 = 1;

#200

S0 = 1 ; S1 = 0 ; S2 = 1;

#200

S0 = 0 ; S1 = 1 ; S2 = 1;

#200

S0 = 1 ; S1 = 1 ; S2 = 1;

#200

$stop;

end

endmodule

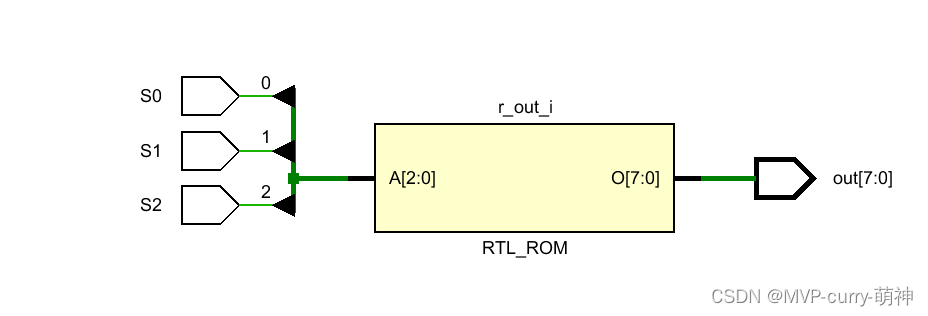

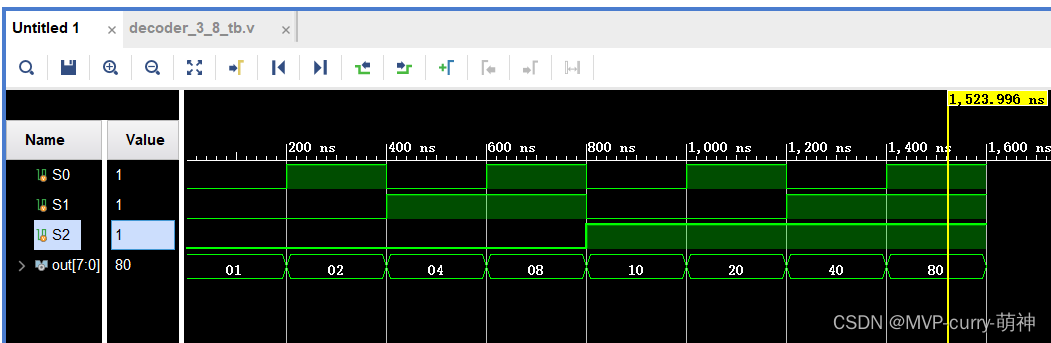

给予如上图的激励,仿真图如下:

Verilog代码实现3-8解码器及其仿真,

Verilog代码实现3-8解码器及其仿真,

文章详细描述了一个使用Verilog编写的3-8解码器模块,通过case语句实现输入信号S0,S1,S2控制输出。随后进行了时序仿真,展示了不同输入组合下的输出结果。

文章详细描述了一个使用Verilog编写的3-8解码器模块,通过case语句实现输入信号S0,S1,S2控制输出。随后进行了时序仿真,展示了不同输入组合下的输出结果。

1493

1493