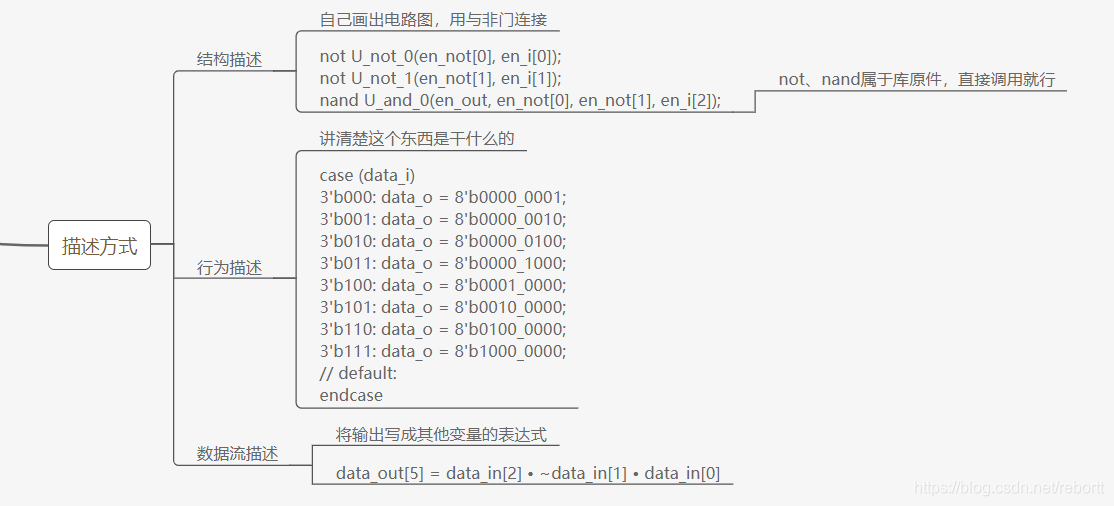

描述方式

之前说过,verilog属于高级语言,需要软件设计硬件结构来实现,也说过描述方式是有很多种的,下面介绍一下。

结构描述十分底层,相当于自己搭电路;

行为描述最简单,只需要写出输入对应的输出就行,例子中需要case语句。

数据流描述比较玄学,还需要找关系,感觉也不太好。

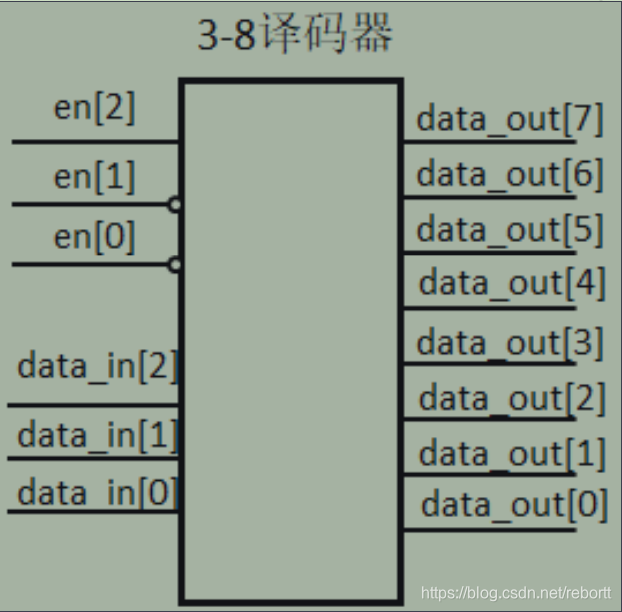

对于题目38译码器这样一个简单的器件,我们选择行为描述的方式最简单(要是有个十几个输入,case语句直接爆炸,所以这种方式也是有限制的)

代码:

`timescale 1ns / 1ps //时钟信号的精度和周期

module decoder_38(

input [2:0] data_i, //输入数据

input [2:0] en_i, //使能端,高低有效看要求,这里是0、1位低有效,2位高有效

output reg [7:0] data_o //输出的八位数据

);

always @(*) begin

if(en_i

本文围绕Verilog展开,介绍了其描述方式,包括结构、行为、数据流描述,以38译码器为例说明行为描述较简单;阐述了仿真文件,涉及变量创建、模块调用、赋值原则等;还提及约束文件,给出模板及相关操作,下板后续操作未详述。

本文围绕Verilog展开,介绍了其描述方式,包括结构、行为、数据流描述,以38译码器为例说明行为描述较简单;阐述了仿真文件,涉及变量创建、模块调用、赋值原则等;还提及约束文件,给出模板及相关操作,下板后续操作未详述。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2951

2951