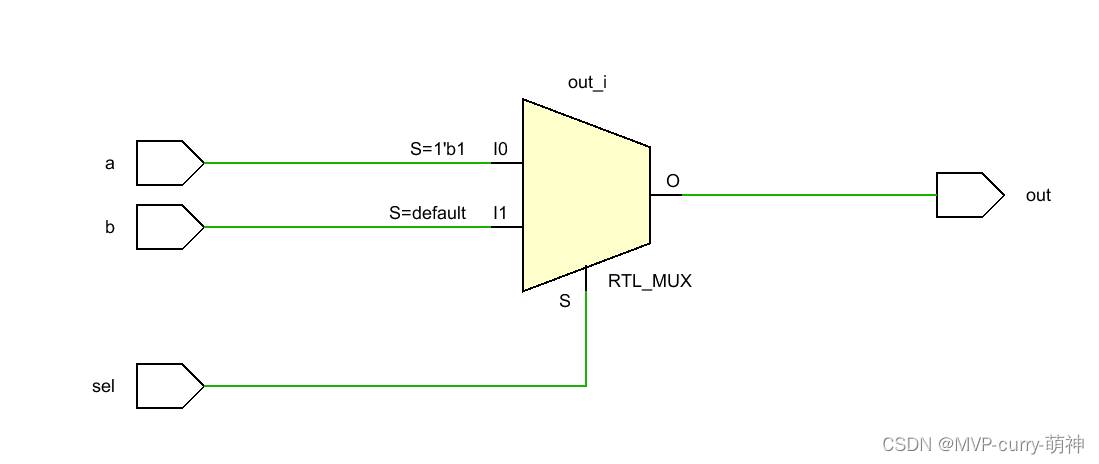

一、Verilog代码实现

module muxtwo(

input a ,

input b ,

input sel ,

output out

)

assign out = (sel == 1) ? a : b ;

endmodule

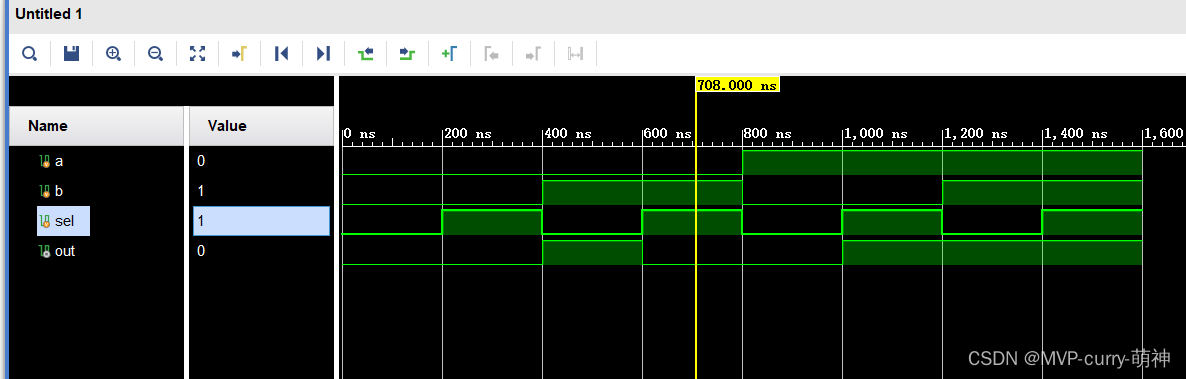

二、仿真

`timescale 1ns / 1ns

module muxtwo_tb();

reg a ;

reg b ;

reg sel ;

wire out ;

muxtwo muxtwo_inst0(

.a (a ) ,

.b (b ) ,

.sel(sel) ,

.out(out)

);

initial begin

a = 0 ;b = 0 ;sel = 0;

#200;

a = 0 ;b = 0 ;sel = 1;

#200;

a = 0 ;b = 1 ;sel = 0;

#200;

a = 0 ;b = 1 ;sel = 1;

#200;

a = 1 ;b = 0 ;sel = 0;

#200;

a = 1 ;b = 0 ;sel = 1;

#200;

a = 1 ;b = 1 ;sel = 0;

#200;

a = 1 ;b = 1 ;sel = 1;

#200;

$stop;

end

endmodule

通过加上激励,出现如下图的波形图:

本文详细介绍了使用Verilog语言实现的多路复用器(muxtwo)模块的代码和功能,以及对其进行了简单的仿真,展示了输入信号变化时输出的波形图。

本文详细介绍了使用Verilog语言实现的多路复用器(muxtwo)模块的代码和功能,以及对其进行了简单的仿真,展示了输入信号变化时输出的波形图。

9021

9021

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?