一、组合逻辑电路与时序逻辑电路

组合逻辑电路:任意时刻的输出仅仅由该时刻的输入决定,与电路当前的状态无关。

时序逻辑电路:任意时刻的输出不仅由该时刻的输入决定,还与电路当前的状态有关。

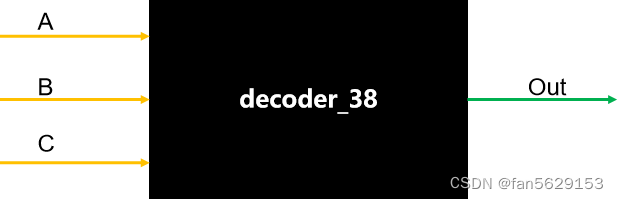

二、38译码器的工作原理

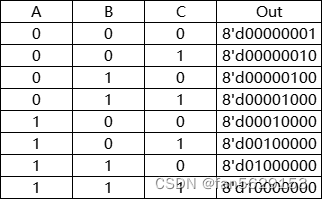

表①、38译码器真值表

3种输入状态翻译成8种输出状态。

三、Verilog代码实现

源码:

module decoder_38 (

a,b,c,data

);

input wire a;

input wire b;

input wire c;

output reg [7:0]data;

always @( a,b,c) begin

case ({

a,b

本文介绍了38译码器的工作原理,并通过Verilog代码展示了其实现过程,包括组合逻辑电路与时序逻辑电路的概念,以及38译码器的真值表和仿真模拟。

本文介绍了38译码器的工作原理,并通过Verilog代码展示了其实现过程,包括组合逻辑电路与时序逻辑电路的概念,以及38译码器的真值表和仿真模拟。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

929

929

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?