FPGA实现

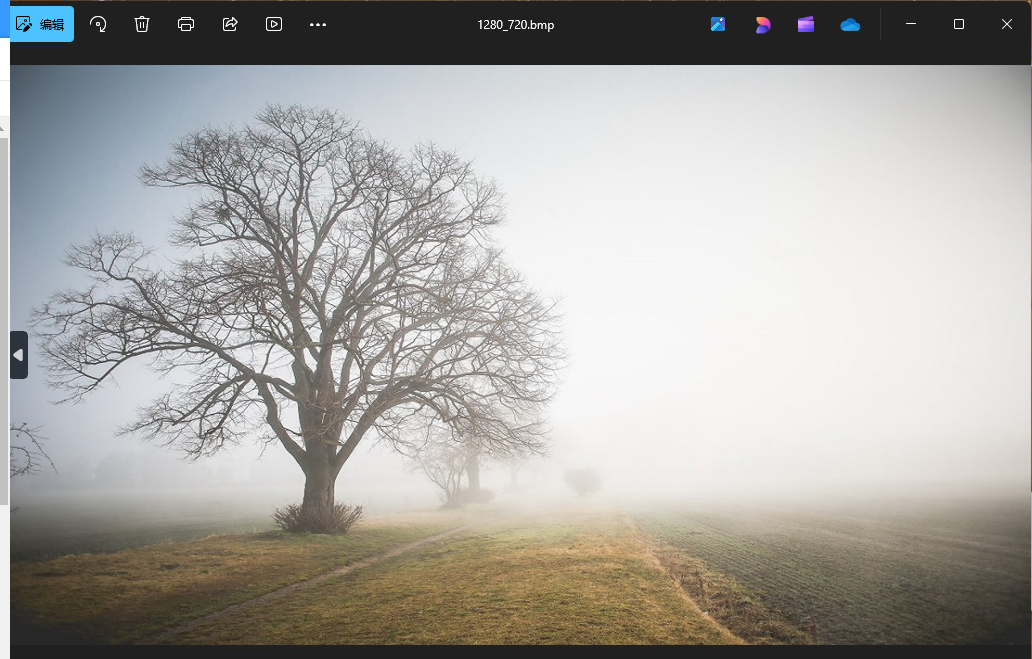

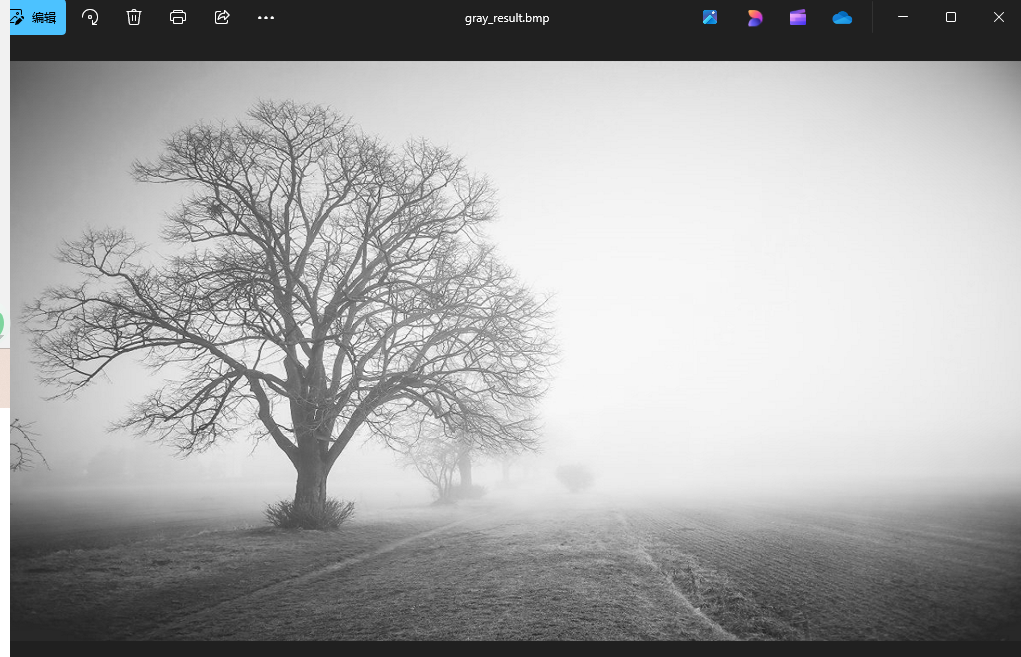

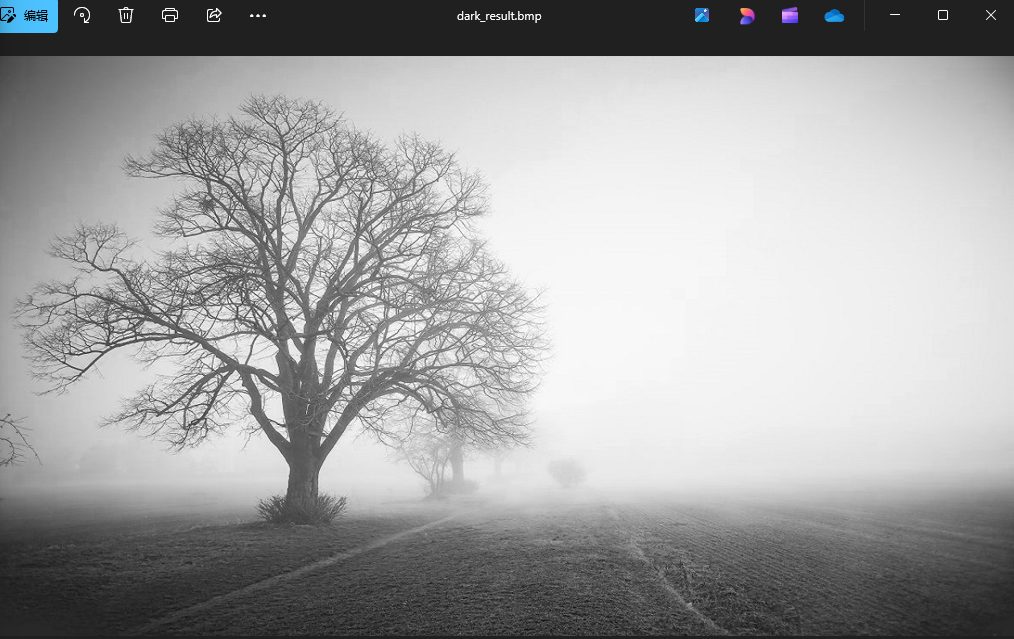

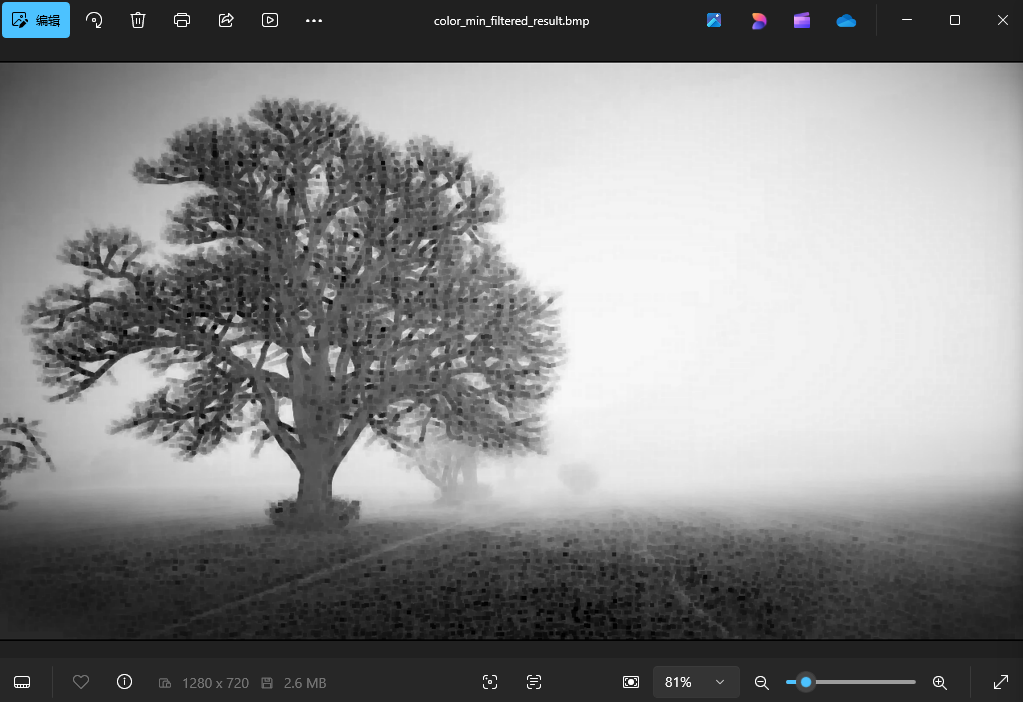

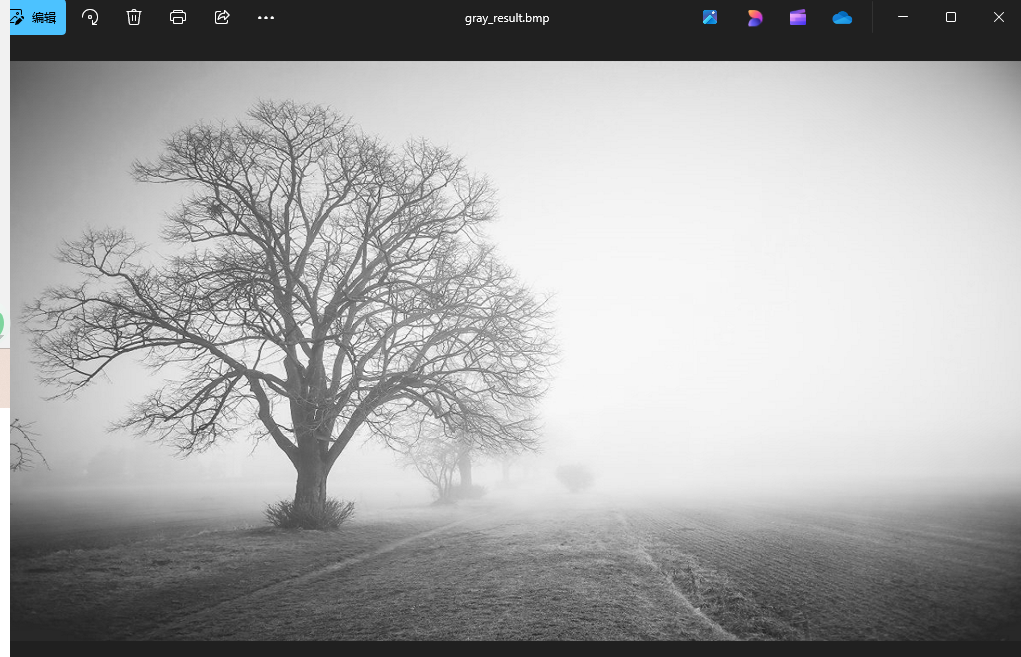

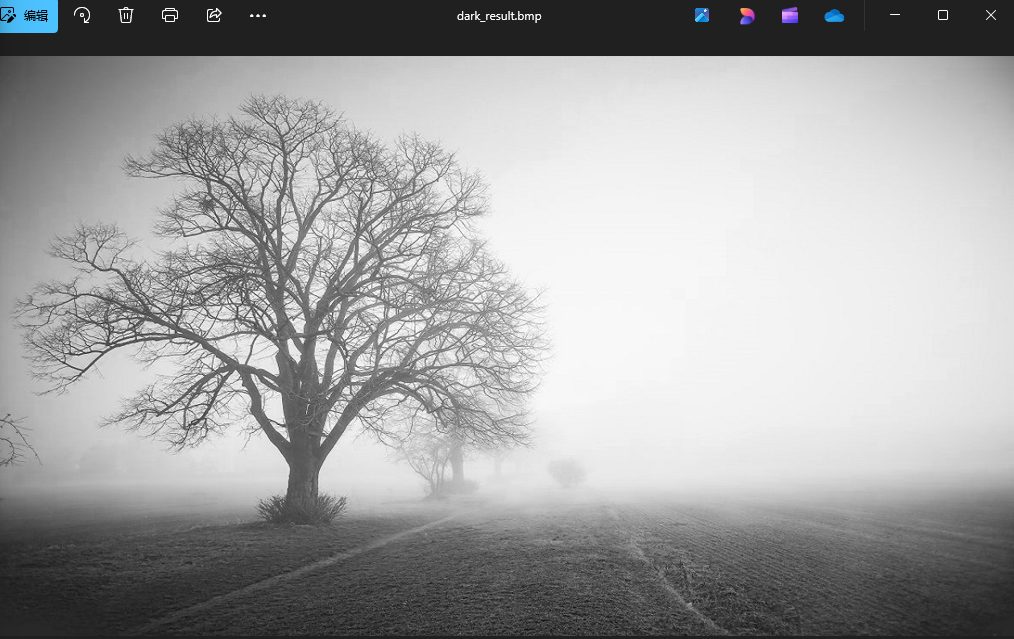

经过暗通道处理单像素最小值后

因为图像灰度化/暗通道处理都是对像素点的RGB三通道取一样的值,图像灰度化是取均值,暗通道处理取的是最小值,在处理这个图像的时候,应为均偏灰色,所以为了了区分;

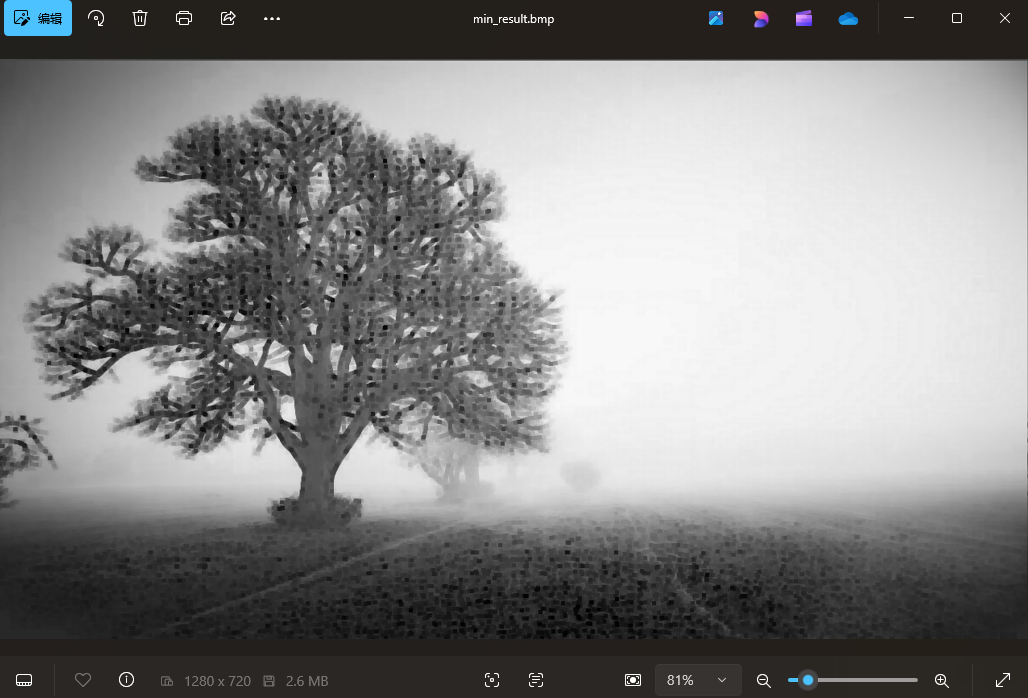

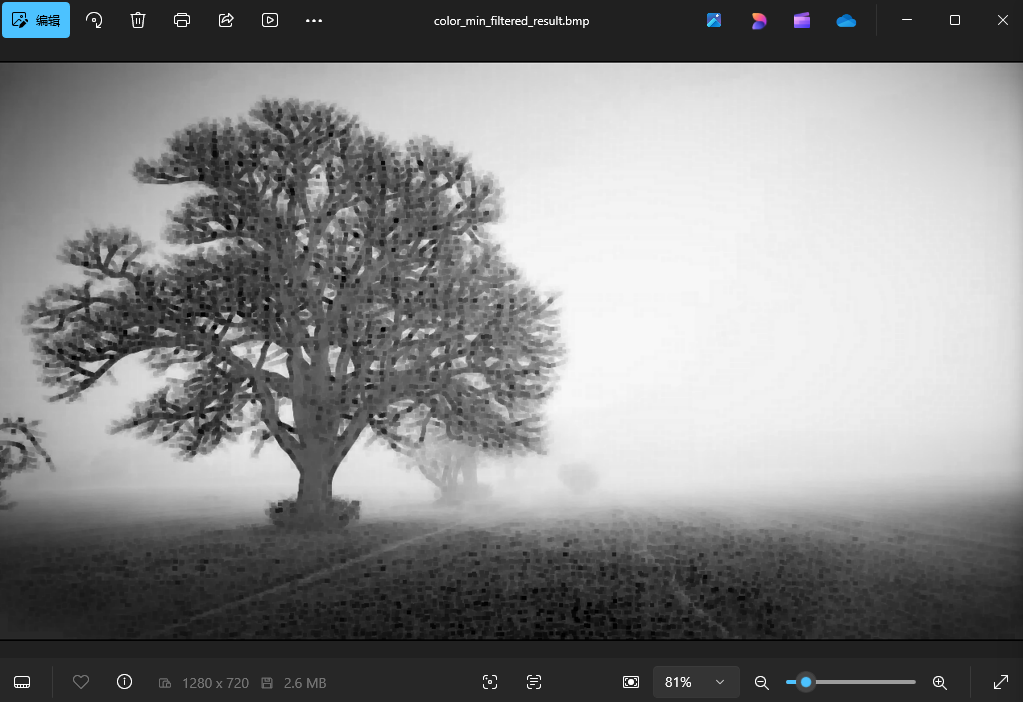

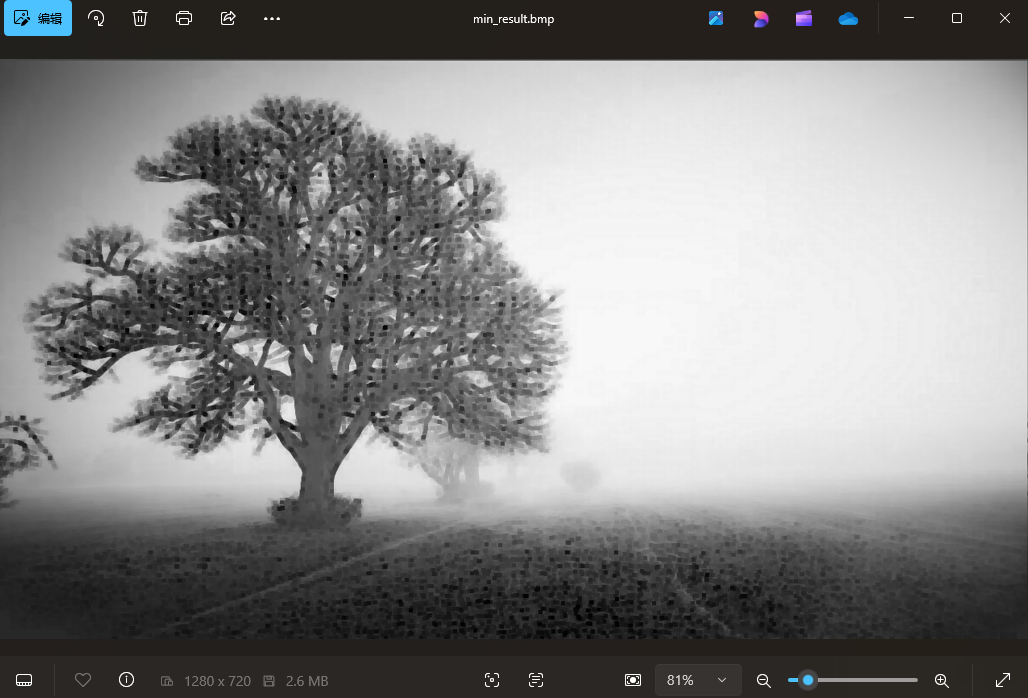

经过5*5滤波核最小值滤波后

matlab自带ordfilt2

fpga硬件实现

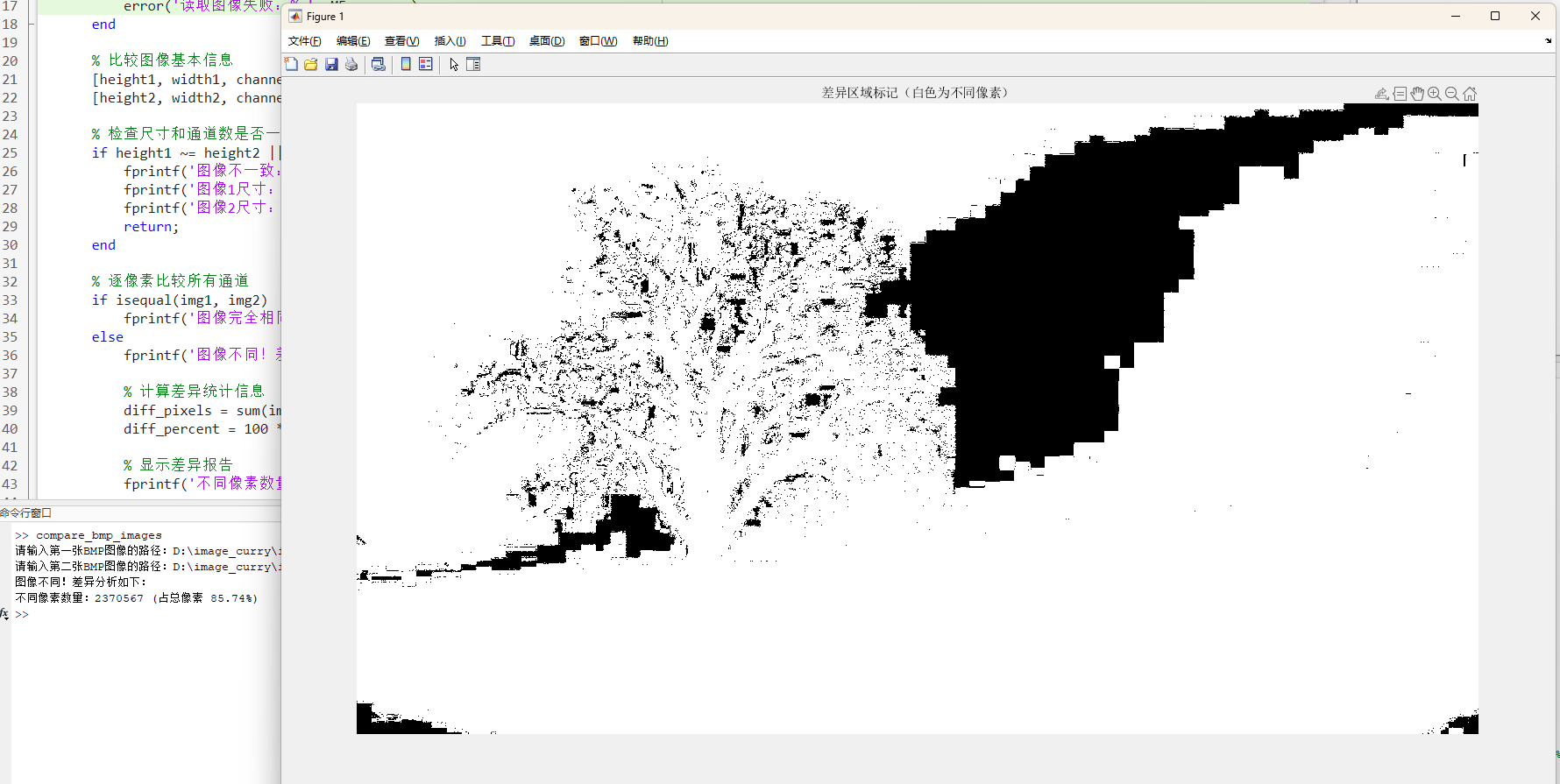

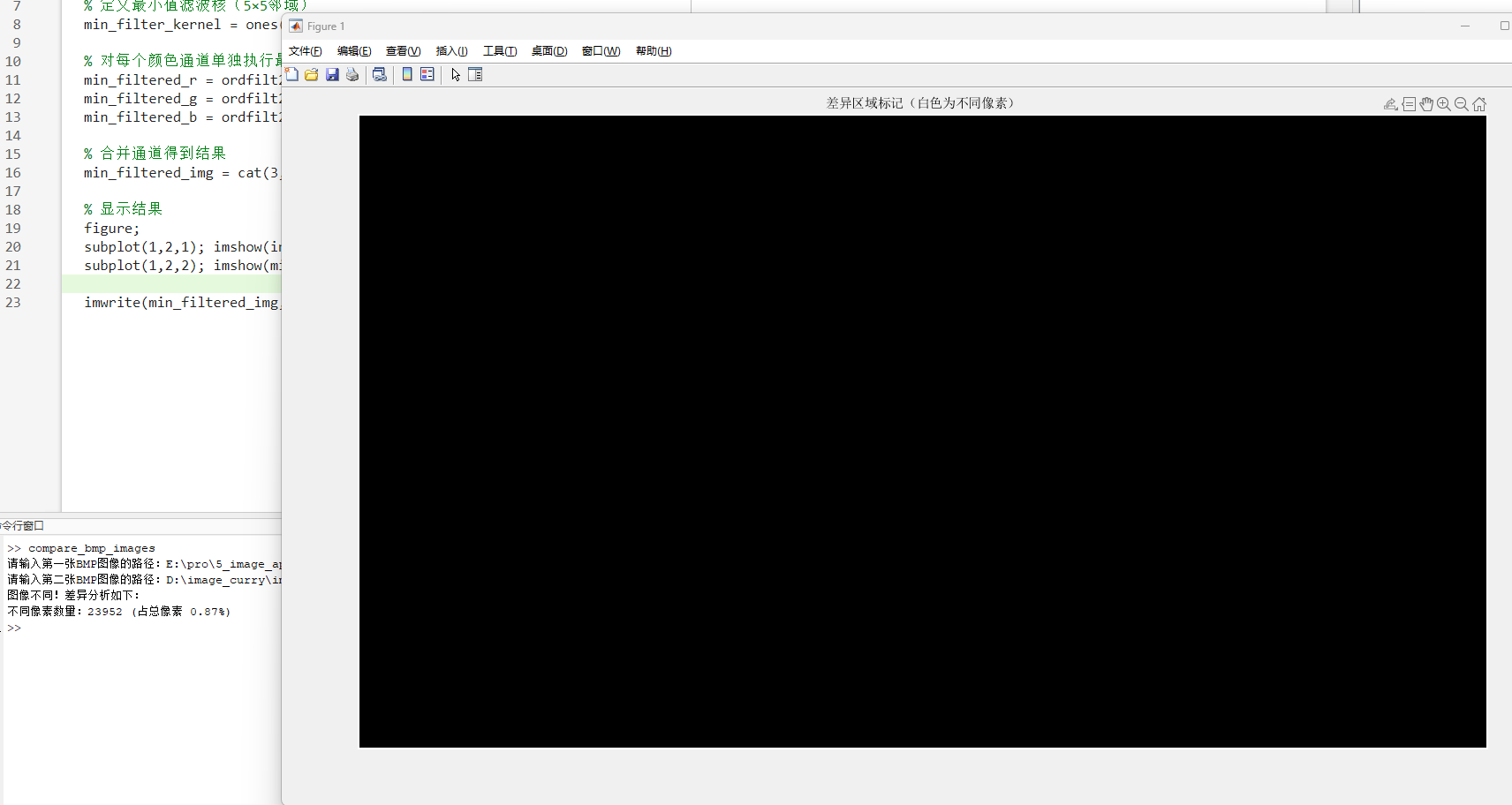

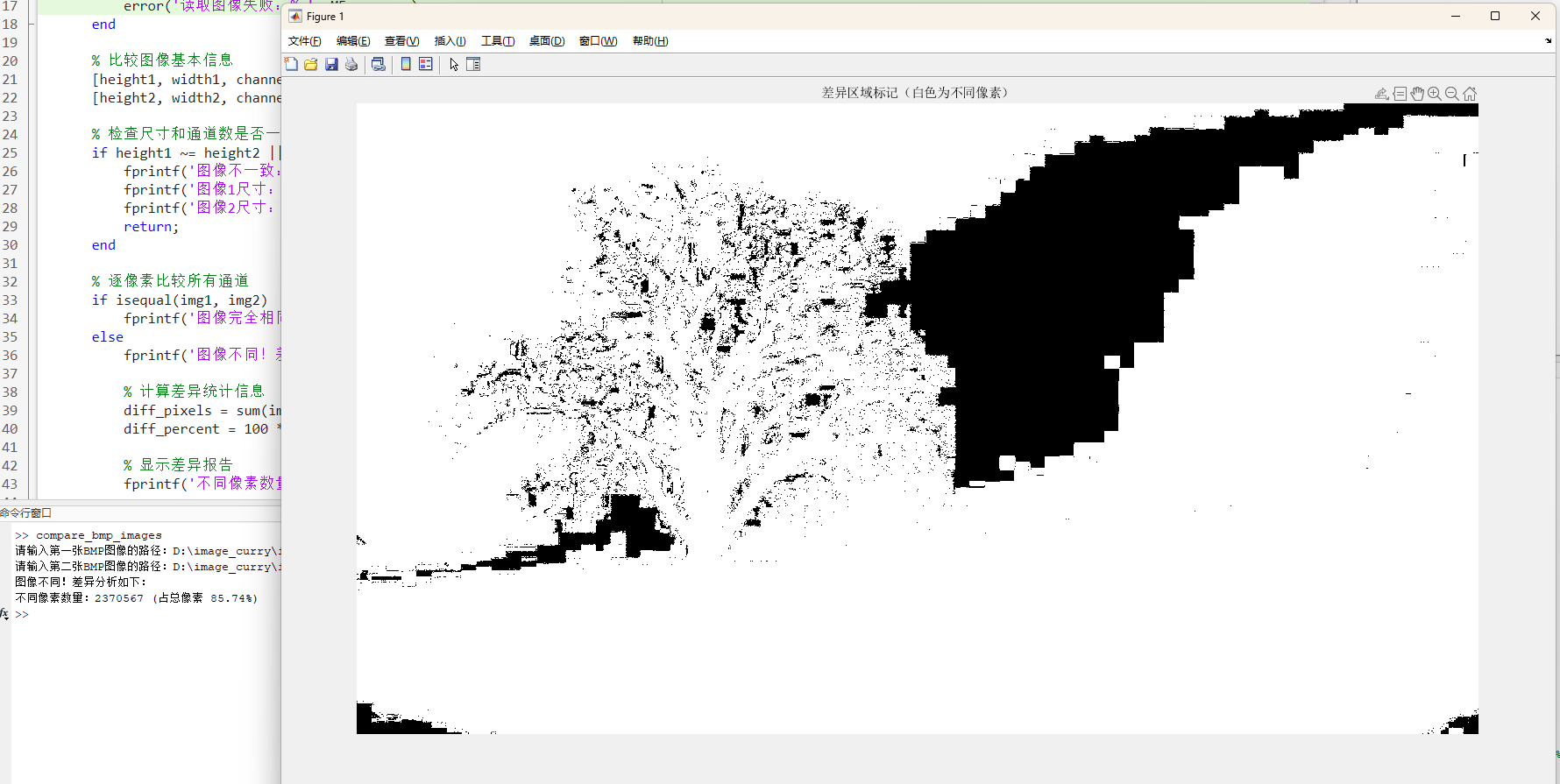

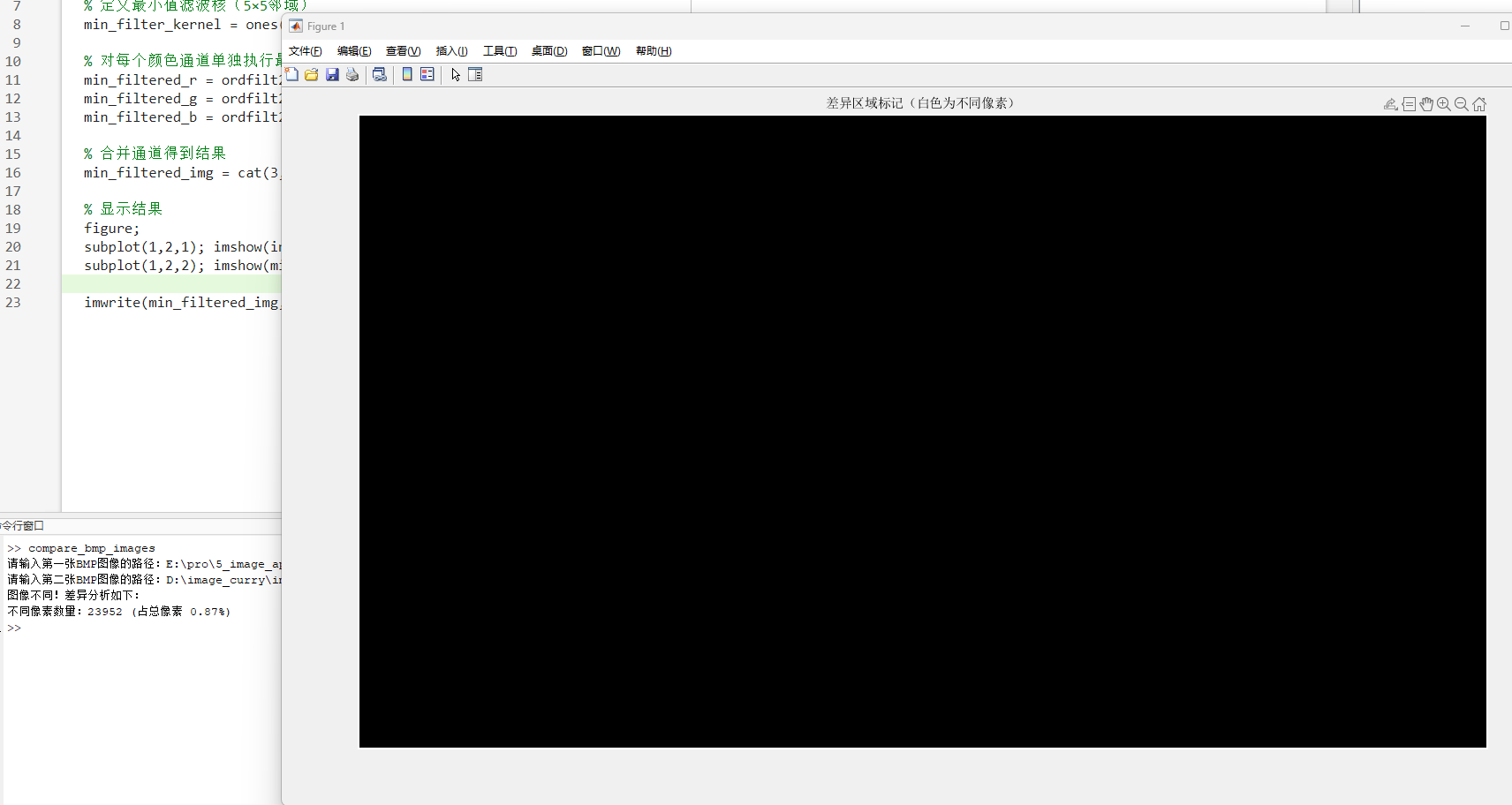

仅有0.87%的不同

仅有0.87%的不同

因为图像灰度化/暗通道处理都是对像素点的RGB三通道取一样的值,图像灰度化是取均值,暗通道处理取的是最小值,在处理这个图像的时候,应为均偏灰色,所以为了了区分;

仅有0.87%的不同

仅有0.87%的不同

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?