基于轴向电容器的10千伏、100安4H‐碳化硅 MOSFET短路测试仪低阻抗母线排设计

摘要

本文讨论了用于10千伏10安4H‐碳化硅MOSFET短路(SC)测试装置的设计。该装置可实现高达10千伏的电压和超过100安的电流。设计的主要目标是在整个装置中实现低寄生电感,同时通过避免直流链路电容器的串联连接以及采用额定电压高于10千伏的电容器来降低装置的复杂性和尺寸。考虑到所需的电气间隙距离、市场上缺乏额定电压为10千伏的径向电容器、CREE 10千伏 10安 4H‐碳化硅MOSFET的封装设计以及器件加热器所需空间,在如此高的电压水平下实现低电感具有挑战性。

使用Ansys Q3D提取设计中的寄生元件。采用定制设计的铝制外壳用于15千伏轴向电容器,以最大限度地降低电感,并采用对称布置以实现最佳的电流均流分布。母线排测量验证了直流链路的低电感设计。所测得的电感值还通过有限元方法分析和实验验证进行了确认。

关键词

直流链;碳化硅,10千伏MOSFET;短路;Ansys Q3D

I. 引言

功率器件的短路(SC)特性表征通常是在将其应用于变流器应用之前评估其鲁棒性的必要步骤,因为在变流器应用中,瞬态可能会损坏或破坏这些器件。这些瞬态是意外的、不可预测的异常运行情况,在变流器的整个生命周期中可能发生,会使器件工作在超出其安全工作区(SOA)的应力条件下。器件可能承受超过其设计值的能量,这些能量由非常大的浪涌电流产生,而浪涌电流仅受限于寄生元件和器件的增益。

器件必须根据其最小短路耐受时间保证(即在特定测试条件下,器件能够安全承受此类过载的参考时间)以及在经历重复性非破坏性短路事件时的行为进行表征。

测试期间,器件将承受高达其额定值10倍的过电流。由于高速开关4H‐SiC器件特有的频率,结合增大的电流上升率,如果电路杂散电感未被最小化,则可能产生过压/欠压瞬态 [1, 2]。此外,为了观察结温对器件短路能力的影响,在表征前需对器件的基板进行精确加热。

为了最小化电路的电感,采用具有低寄生电感的器件并联连接,并使用叠层母线排。这样可以使母线排中的电流反向流动,从而减少磁通产生 [3, 4]。串联电容器在此应用中不切实际,尤其是因为串联连接会增加寄生电感。

本文提出了一种用于短路特性表征的9纳亨母线排设计,可为器件测试提供高达6000毫焦的能量,同时避免超过1%的电压跌落 [1]。

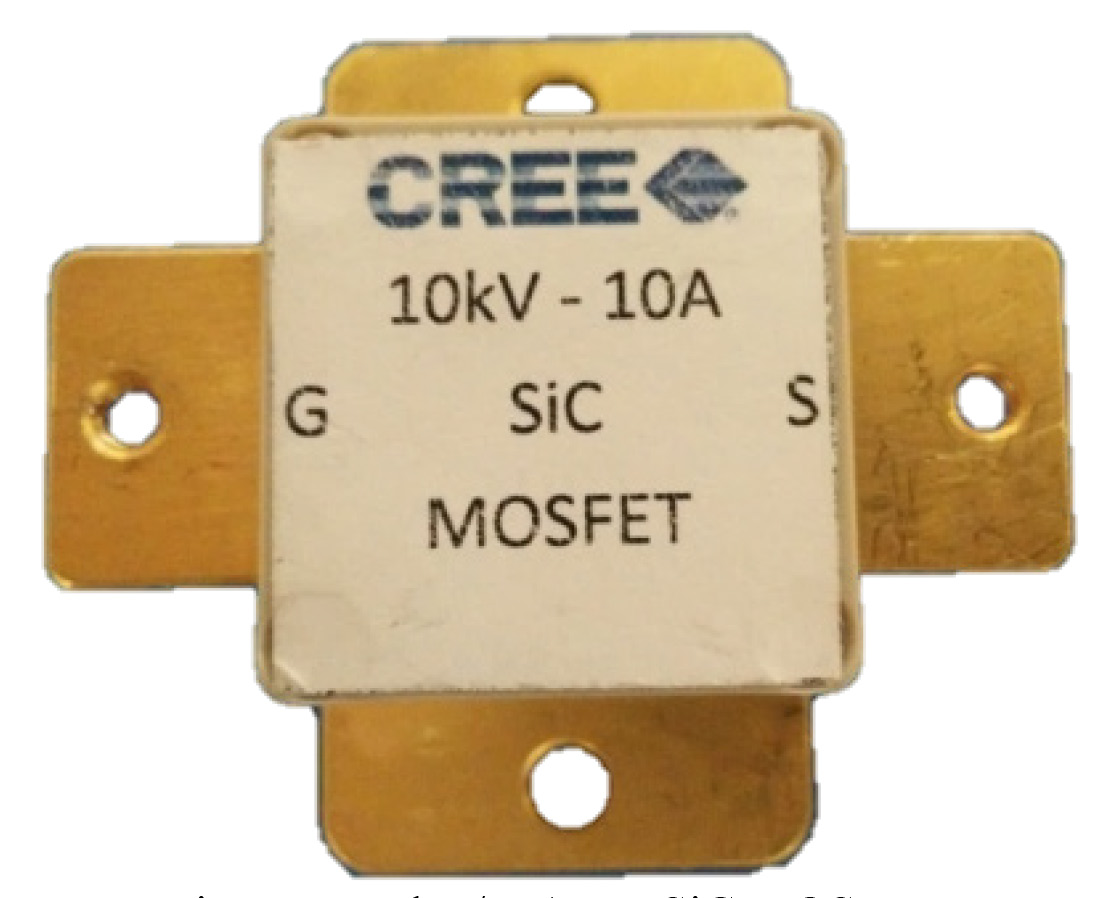

II. 被测器件

图1展示了被测器件(DUT)。该器件是科锐公司生产的10千伏10安4H‐碳化硅MOSFET。其在室温下测得的主要特性总结于表1中。该半导体采用独特的定制封装。在双脉冲测试仪(DPT)中进行开关特性表征时,使用了相同封装的10千伏10安4H‐碳化硅结势垒肖特基二极管。

表I。 MOSFET室温下的特性 [5]

| 击穿电压 (BrV) | 12千伏 |

|---|---|

| 漏极电流(DI) | 10 A |

| 导通电阻 (ONR) | 0.44 |

| 栅极电荷 (GQ) | 350 nC |

| 上升时间 (rt) | 180 ns |

| 下降时间 (ft) | 94 ns |

| 开通能量(onW) | 4.5 毫焦 |

| 开通能量(off W) | 0.8 毫焦 |

III. 测试设置设计与尺寸确定

测试电路设计为一种多功能解决方案,既可实现器件开关特性表征(DPT),也可在钳位和非钳位情况下进行短路能力测量。同时,该电路可通过外部加热板实现结温控制。此外,它还可用于重复短路测试,以评估被测器件的可靠性。图2所示为简化电路图,其基于经典DPT。

电感器和二极管可根据测试程序要求轻松拆卸。测试电路的最大电压为10千伏,受限于2千瓦/10千伏Magna Power XR直流电源,且设计用于在短路测试中提供超过100安培的电流。通过控制被测器件栅极电压的宽度W(GS V),可调节短路测试时间及电流。该装置设计使得电感器和二极管能够方便地插入电路中,从而允许在相同电路中对器件进行表征。针对不同应用的各种平面母线排设计及其设计模型已在文献[3, 6]中提出。

在设计可能承受感性负载的电力电子变换器时,通常将工作直流母线电压设定为器件额定电压的60%左右,以避免在关断时由于负载电感导致电压过冲超过击穿电压的情况。为了研究正常运行期间的短路行为,短路测试仪的设计也采用了类似的假设。直流母线电压选定为6千伏,从而避免了关断时过电压带来的应力。为了获得准确结果,在设计此类电路时必须特别考虑一些因素。在短路瞬态期间,MOSFET通常表现得类似于一个电阻器,因此输入电容中存储的能量应足够大,以避免输入电压发生显著波动。

通常4H‐SiC MOSFETs被设计为可承受的最大短路能量小于3000毫焦[1, 7], ,因此,为了提供良好的安全裕度,输入电容的最小能量被设定为至少6000毫焦,并且最大允许电压跌落ǻ9 在1% of 6 kV (60 V)。基于上述要求下,计算出的最小所需电容为:

$$

C = \frac{2 \times E_{SC,max}}{V_{DC}^2 - (V_{DC} - \Delta V)^2} = \frac{2 \times 6000 \times 10^{-3}}{6000^2 - 5940^2} = 16.75\,\mu F

$$

(1)

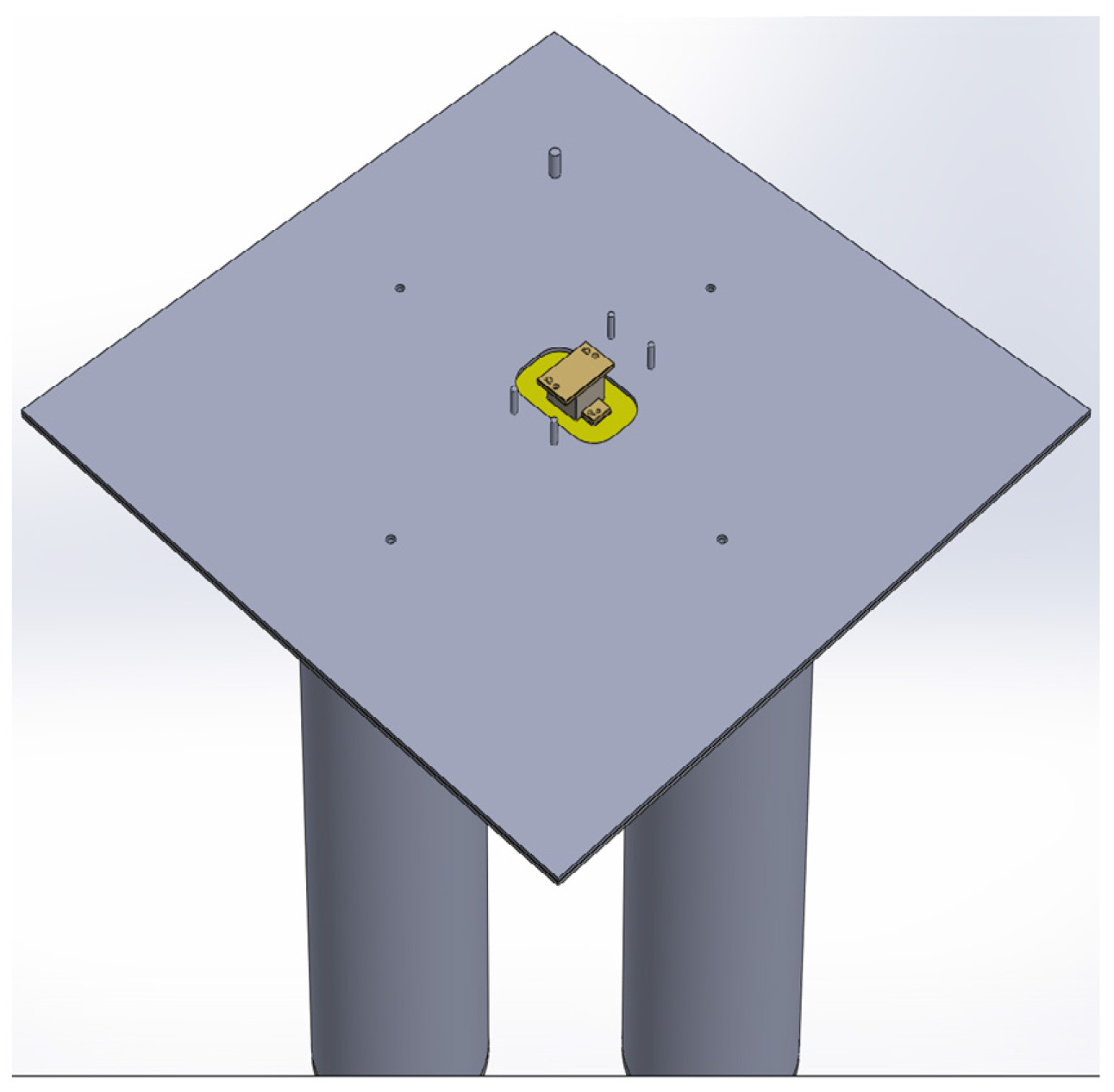

为了最小化电路的寄生电感并实现围绕被测器件的对称性,将4个相同的 6μF、额定电压为15千伏的薄膜电容器并联连接,并将被测器件置于中间位置,如图3所示。

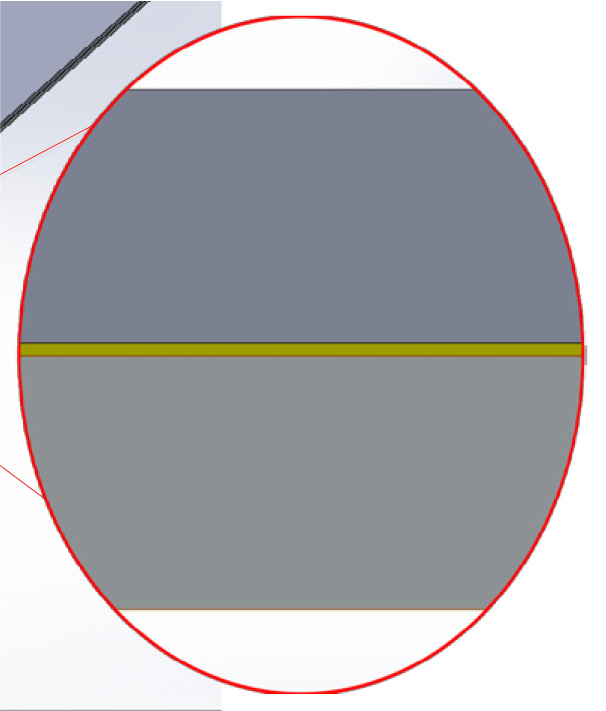

由于制造限制,额定电压高于5千伏的电容器采用轴向端子设计。为了限制寄生电感并避免大量串联和并联连接的电容器,将15千伏电容器放置在铝制外壳中,从而使正负端子均可引至同一平面。所使用的电容器具有15纳亨的内部寄生电感。

假设薄膜电容器为一个整体导体,外部外壳为已知半径的空心圆柱体,则可计算每个电容器的近似电感:

$$

L = \frac{\mu_0 l}{2\pi} \ln\left(\frac{R}{r}\right) = \frac{1.26 \times 10^{-6} \times 0.3}{2 \times 3.14} \ln\left(\frac{0.057}{0.055}\right) = 31.86\,nH

$$

(2)

其中 $\mu_0$ 是自由空气磁导率,$l$是电容器和外罐的长度(单位:米),$R$是外罐的半径(单位:米),$r$是电容器的半径。这些

图2:简化电路图

2mm

2mm

0.25mm

21354

正母线排侧 2) 绝缘聚酯薄膜 3) 负母线排侧 4) 被测MOSFET 5) 直流链路电容器)

正母线排侧 2) 绝缘聚酯薄膜 3) 负母线排侧 4) 被测MOSFET 5) 直流链路电容器)

图3:母线排CAD设计 1) 正母线排侧 2) 绝缘聚酯薄膜 3) 负母线排侧 4) 被测MOSFET 5) 直流链路电容器

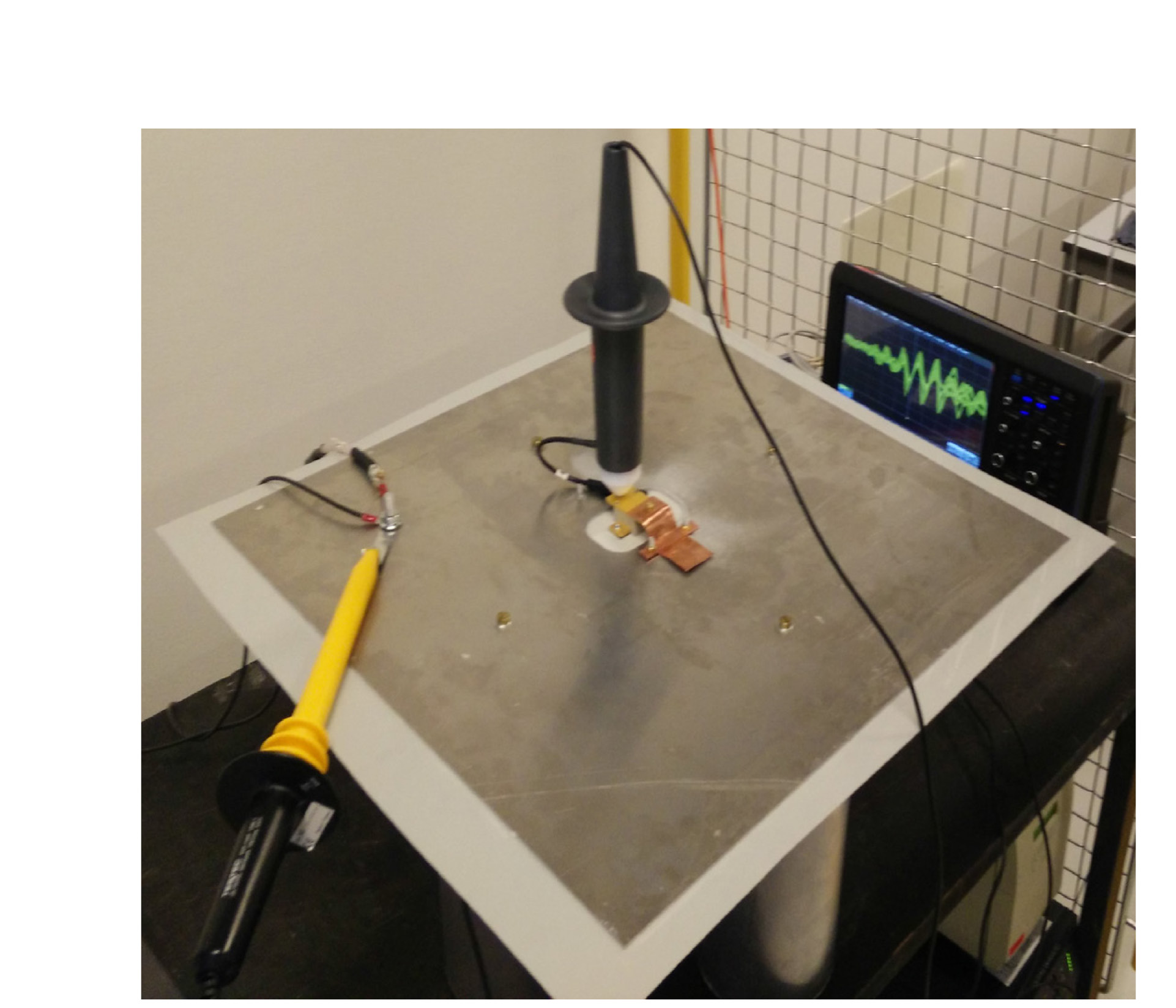

假设电流在罐体和电容器中均匀分布。因此,对于4个并联电容器,其电感为7.95nH。直流链(DC‐link)由两块铝板组成,每个端子各一块,厚度为2毫米,中间夹有0.25毫米聚酯绝缘膜,绝缘等级为20千伏。被测器件(DUT)通过顶板上的开孔直接连接到铝板上,如图4所示。电流通过一个低电感螺栓式分流电阻进行测量,该电阻用于将MOSFET的源极连接到母线排的负极板。带有电容器的直流链总电感是使用一个

图4:测试设置

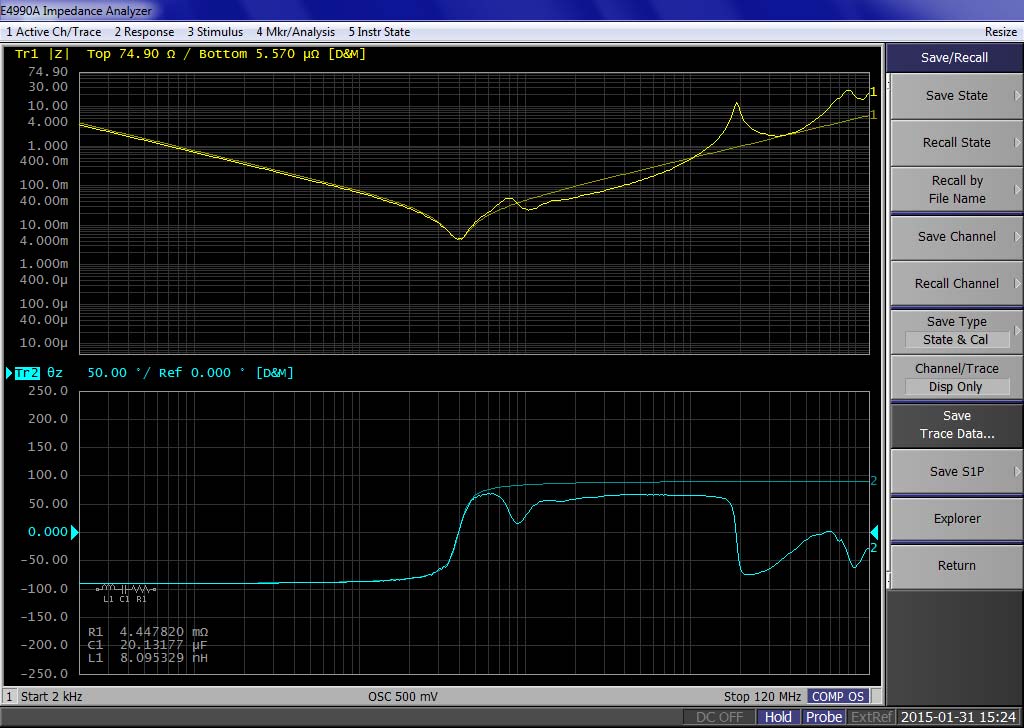

使用安捷伦E4990A阻抗分析仪测得其值为8.09纳亨,如图5所示。通过Ansys Q3D采用交流电感估算方法并使用106个三角形网格进行分析,也确认该值接近8.4纳亨。

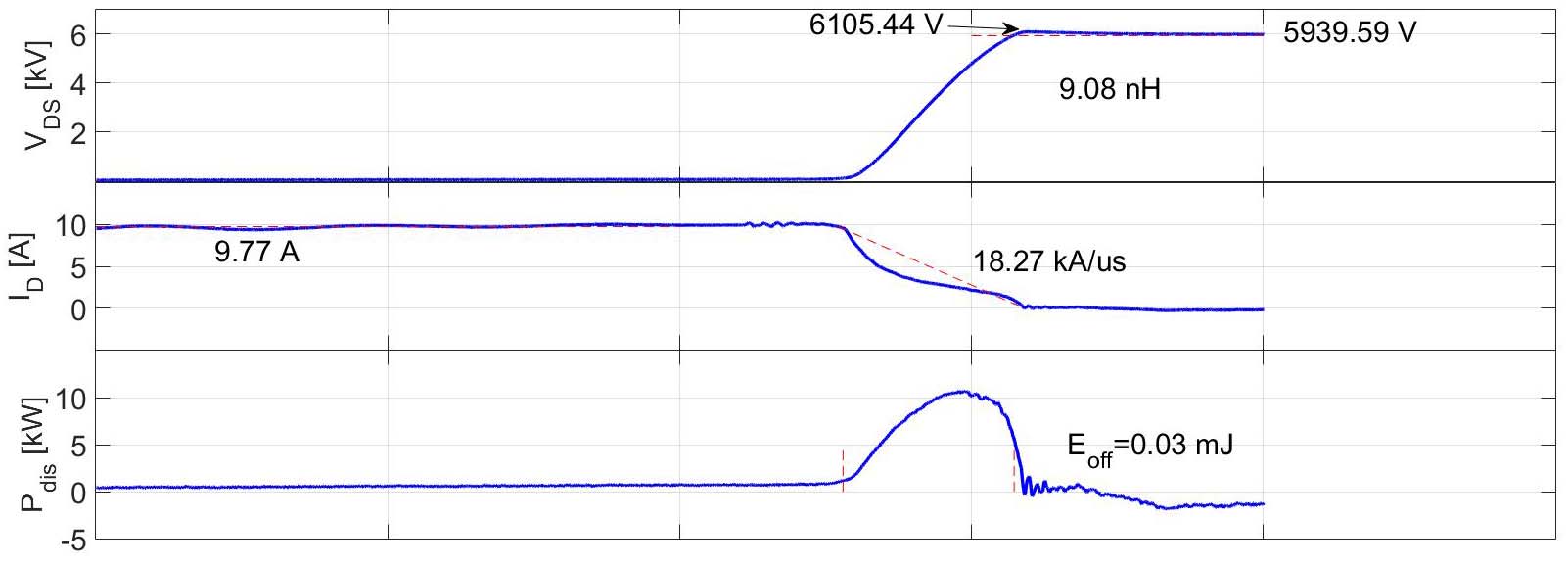

在电路中接入二极管和电感器后,进行了双脉冲测试,以测量器件的开关特性,同时计算系统的寄生电感。

对于开关电感器,制作了一个定制的20毫亨、10千伏电感器。直流链被充电至6千伏,并在室温下进行了测试。调整第一个脉冲宽度以获得约10安培的关断电流。电压和电流测量使用无源探头进行,以便在系统中尽可能减少延迟或衰减,结果如图6所示。

关断电流为9 A,$di/dt = 18.77\,kA/\mu s$。外部栅极电阻设为3,栅极电源从‐5伏特/+18伏特。

关断时,漏源电压$V_{DS}$上升至6.105千伏并稳定在5.939千伏。根据测得的电压过冲和计算的电流上升率,包括连接螺钉和螺母在内的电路寄生电感总计为9.08纳亨。总关断能量也经过计算,为0.03毫焦。

这证实了直流链寄生电感的测量与仿真结果。

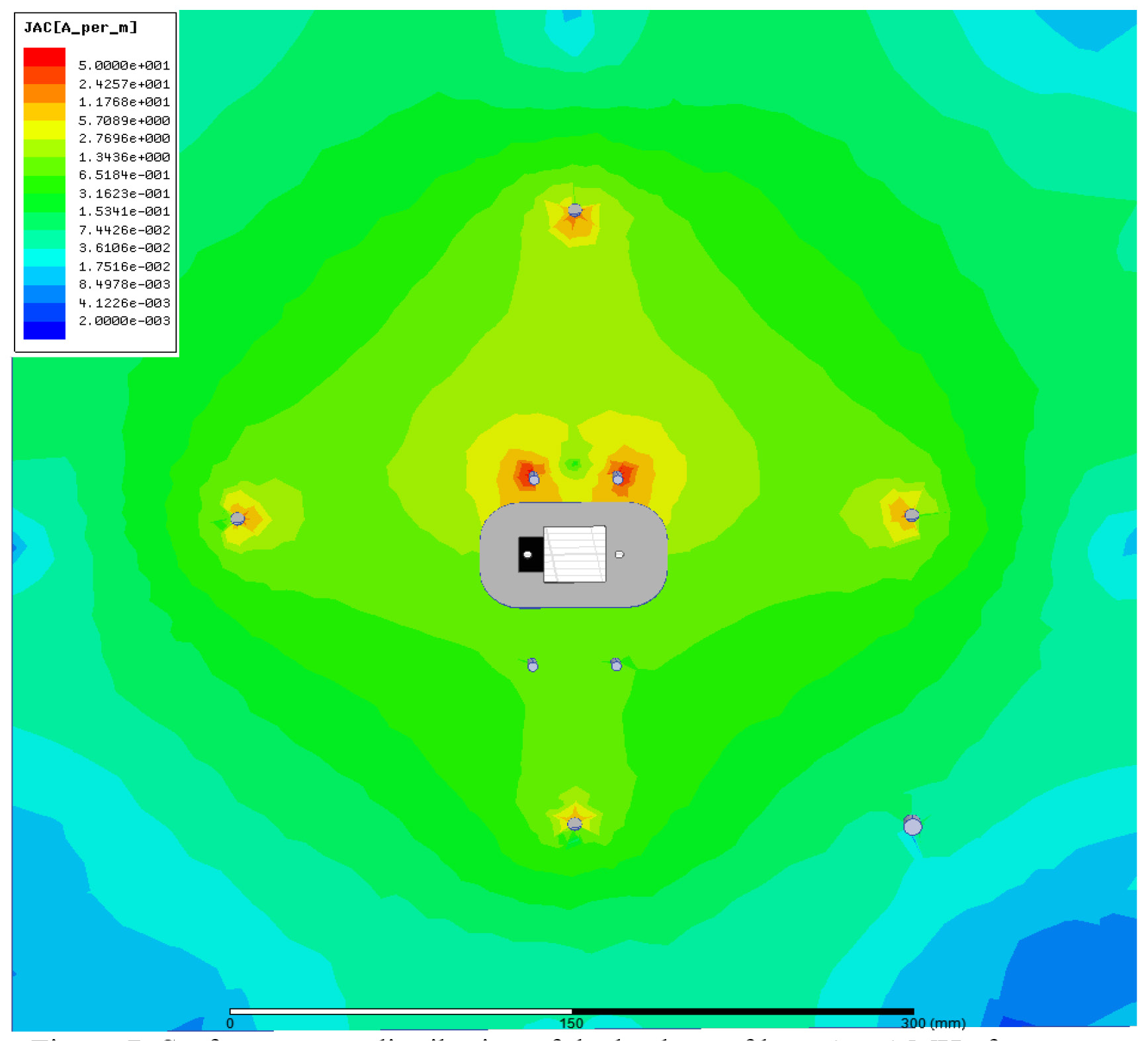

还使用相同的软件研究了并联电容器之间的电流分布。在图7中观察到它们之间的表面电流均分。

图5:使用安捷伦E4990A对母线排进行R‐C‐L测量

图6:室温下10千伏4H‐碳化硅MOSFET在6千伏和10安培条件下的关断波形,Vgs=-5V +18V

图7:环路1母线排在1兆赫兹频率下的表面电流分布

IV. 测试模式

首先测量MOSFET的传输和开关特性,以获取其初始特性。随后,使用一个简单的单脉冲对MOSFET进行测试,将器件直接连接在电容器的两端。此时,器件将承受其端子上的全部电压和能量。脉冲参数从初始时间

$$

t_{\text{Init}} = t_{\text{on,min}} + t_r + t_d + t_{\text{off}} + t_f + t_{\text{doff}}

$$

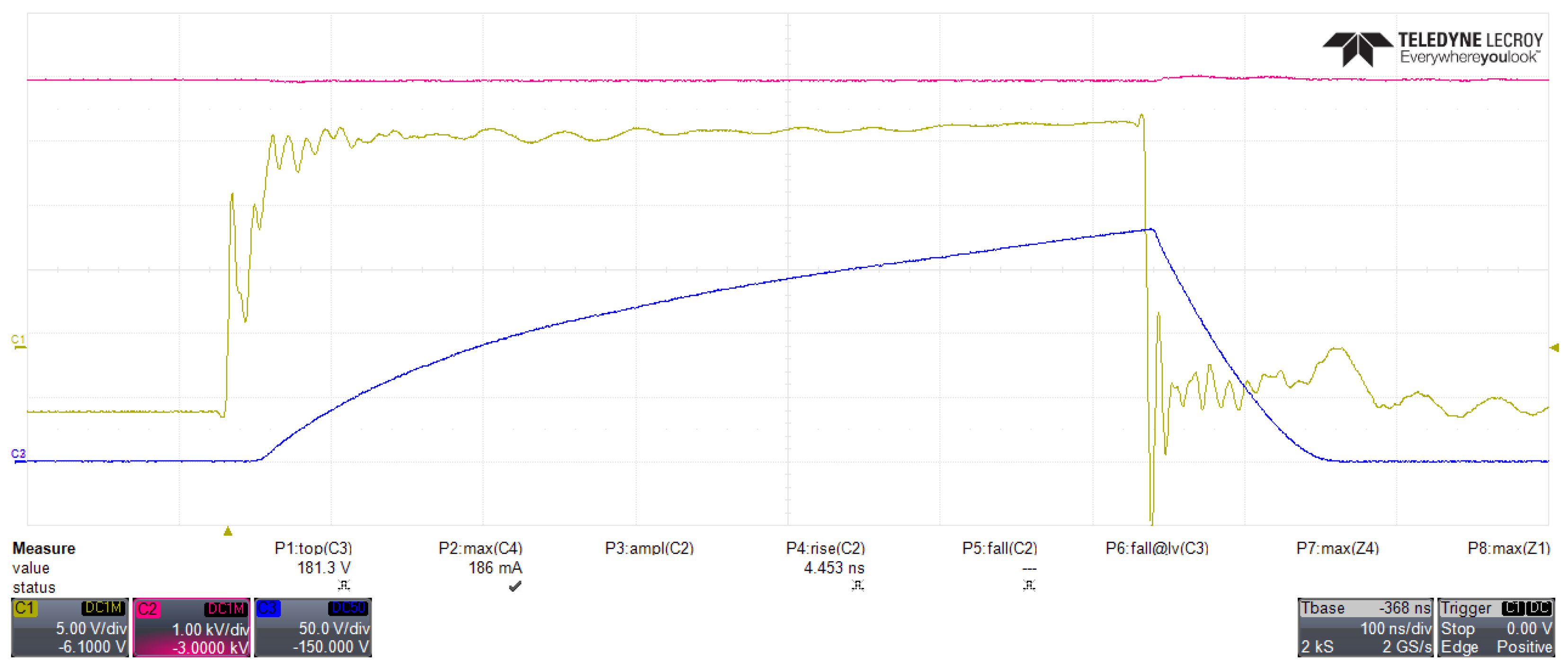

开始,然后以500纳秒为步长逐步增加,直到观察到失效为止。每一步之后,均留出足够的时间使结温得以耗散,以免影响后续的测量。在发生失效时,根据测得的波形计算临界能量CE。该值将代表阈值能量,超过该能量单个短路脉冲将导致器件失效,低于该能量则器件可恢复。典型短路波形如图8所示。通道1(浅绿色)表示栅源电压$V_{GS}$。通道2(品红色)表示漏源电压$V_{DS}$。通道3(蓝色)表示通过分流电阻测得的漏极电流$I_D$。由于示波器的限制,除非连接专用电流探头,否则无法将通道单位更改为安培。测试初始步长为500纳秒。由于直流链的寄生电感较低,关断时漏源电压$V_{DS}$的振荡可忽略不计。漏极电流$I_D$在500纳秒内上升至181安。每次短路测试后,均在双脉冲测试仪和曲线追踪仪中对器件重新表征,以观察短路对器件的影响以及栅氧化层、导通态电阻和正向压降[8]退化带来的影响。

根据计算得到的CE,进行重复短路测试,短路时间为

$$

t_{\text{SCrep}} = \frac{2 \times CE}{I^2 \times R_{\text{on}}}

$$

直到观察到退化现象为止。

每进行500次重复短路后,使用DPT和曲线追踪仪对器件重新表征,以观察老化对器件特性的影响。

V. 结论

本文提出了一种用于10千伏4H‐碳化硅MOSFET双脉冲测试和短路测试的新型设计。讨论了针对此类高电压应用的母线排设计以及现有可用元件所带来的挑战。测量和仿真结果表明,将器件置于中心并对电容器采用对称布置,可实现直流链中的均流。通过将轴向高压电容器封装在填充环氧树脂的定制设计铝罐中,实现了母线排的低电感。

通过绝缘凝胶和层压的方式,使反向电流能够彼此靠近流动,从而降低其对寄生电感的影响。换流回路的总电感约为8.5纳亨,对于此类高压母线排而言,这一数值前所未有,特别是考虑到使用了轴向电容器。

图8:10kV 4H‐SiC MOSFET在室温下的短路波形

2581

2581

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?