这期我们来看看RFSoC独有的IP核——Zynq UItrascale+ RF Data Converter如何使用。

我使用的VIVADO版本是2018.3,这个是最低版本,要开发RFSoC,VIVADO版本必须不低于2018.3。

另外电脑配置也需要很高,64位,8核@3.4GHz CPU,16GB内存,固态硬盘这样的配置只能算低配,刚勉强能跑起来。建议有条件的朋友使用工作站或者服务器。

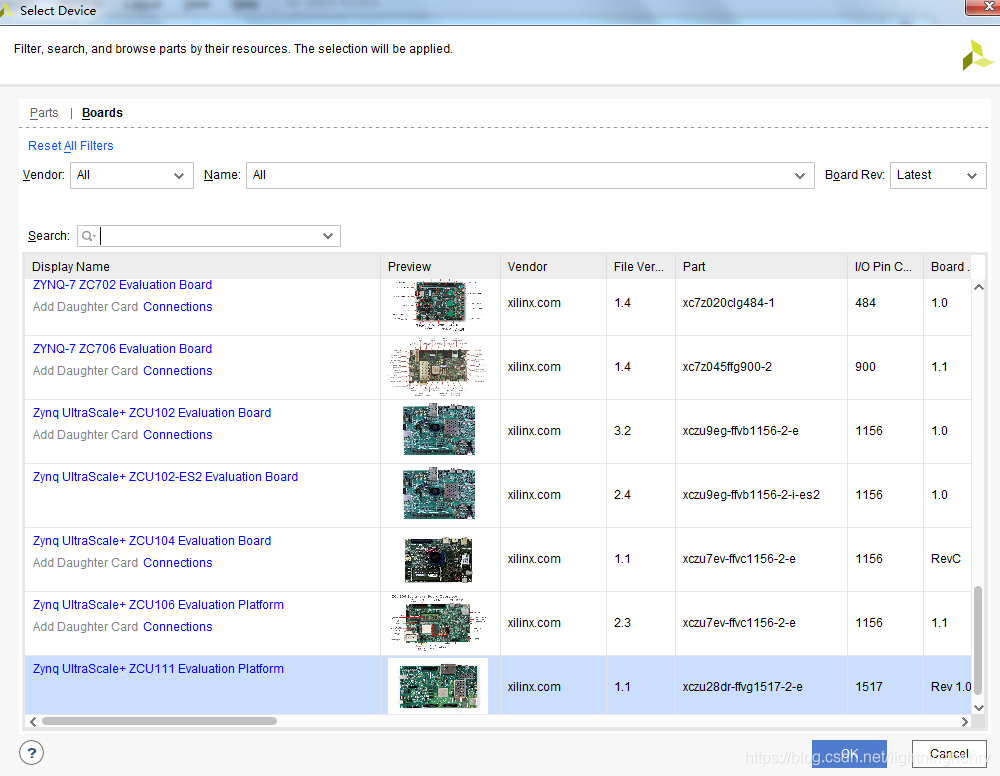

首先在VIVADO中新建一个工程,因为我使用的是xilinx官方的开发板,所以可以直接设定选board就行。

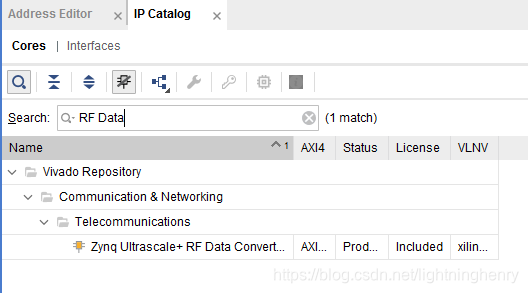

在IP Catalog中输入RF Data就能找到这个IP核。

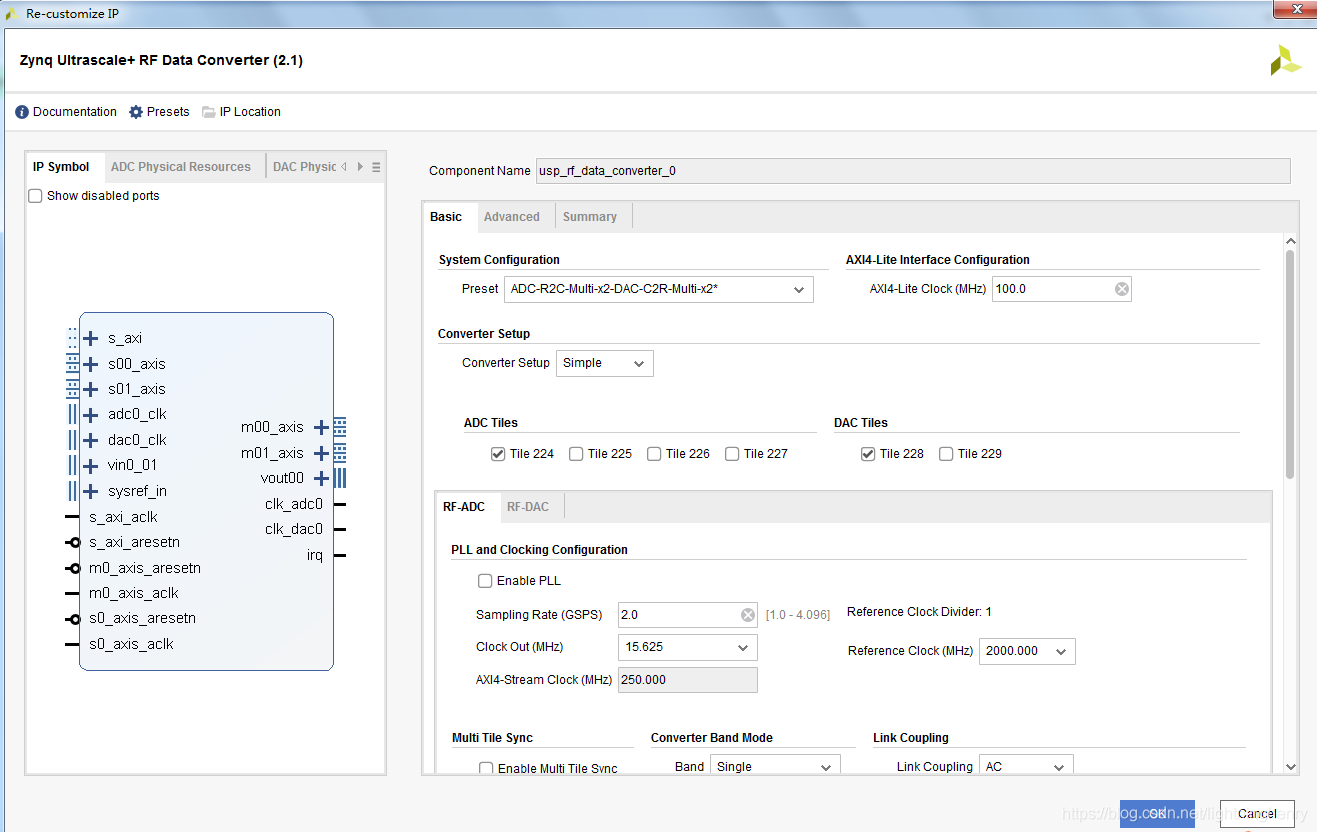

打开以后IP核的配置界面如下:

我们先配置一个简单的,单通道ADC+单通道DAC,实数转复数,单频段。

下面依次介绍界面上的选项。

目录

2. PLL and Clocking Confiquration

3. Multi Tile Sync、Converter Band、ModeLink Coupling

Basic

1. System Configuration

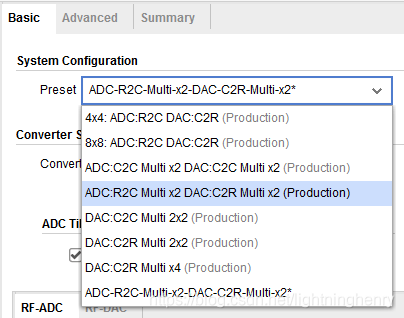

Preset可以预设几种不同的AD/DA模式:

例:8x8用在MIMO体制,8输入8输出;

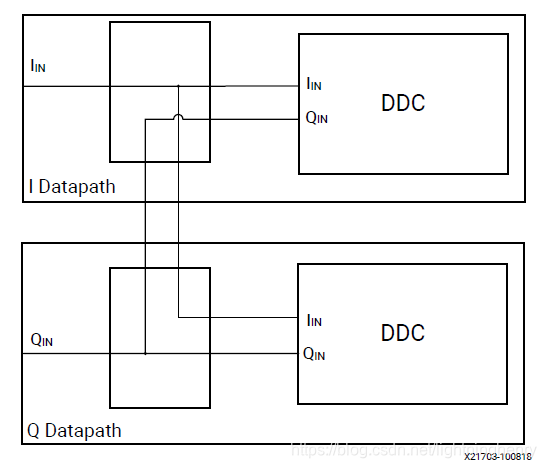

Multi x2意思为双频段,对应会将硬件配置为如下形式:

图5

还有AXI4-lite的时钟配置、简单/高级模式、tile选择等,这些选项比较简单,相信大家都明白就不赘述了。

我们这次配置的是单通道的,简单模式就可以;需要多通道并且多通道使用不同配置时才需要使用高级模式。

2. PLL and Clocking Confiquration

(1)采样率可以任意配;

(2)Clock Out。用户时钟,与数据同步。

(3)Reference Clock。ADC采

本文详细介绍了Xilinx RFSoC中Zynq Ultrascale+ RF Data Converter IP核的配置过程,包括System Configuration、PLL和Clocking Configuration、Multi Tile Sync、Converter Band和ModeLink Coupling等关键设置。内容涵盖ADC和DAC的基本配置,如采样率、时钟同步、混频器设置、模拟校正模式等,旨在帮助开发者理解并使用该IP核。

本文详细介绍了Xilinx RFSoC中Zynq Ultrascale+ RF Data Converter IP核的配置过程,包括System Configuration、PLL和Clocking Configuration、Multi Tile Sync、Converter Band和ModeLink Coupling等关键设置。内容涵盖ADC和DAC的基本配置,如采样率、时钟同步、混频器设置、模拟校正模式等,旨在帮助开发者理解并使用该IP核。

订阅专栏 解锁全文

订阅专栏 解锁全文

2万+

2万+