PCB 走线间距的设计目标,最终需通过制造工艺实现 —— 若制造精度无法满足设计的间距要求,再合理的设计也会沦为 “纸上谈兵”。不同制造工艺(如蚀刻、阻焊、钻孔)对走线间距的实现能力不同,且存在明确的工艺限制;同时,制造过程中的偏差(如蚀刻过度、阻焊偏移)也可能导致实际间距与设计值不符,引发质量问题。

一、核心制造工艺对走线间距的影响

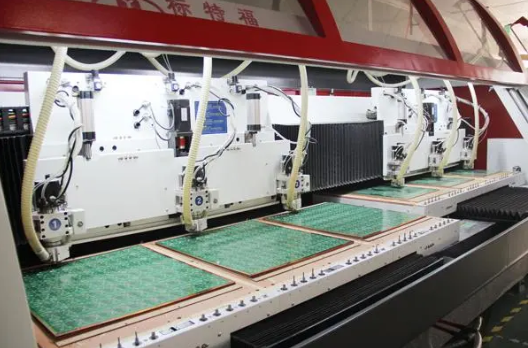

1. 蚀刻工艺:决定走线间距的 “最小精度”

蚀刻是通过化学溶液去除 PCB 基材上多余铜箔,形成走线的过程,其精度直接决定最小走线间距。蚀刻工艺的关键参数 “蚀刻公差”,会导致实际走线宽度与设计值存在偏差,进而影响间距 —— 若设计间距 0.1mm,蚀刻公差 ±0.01mm,实际间距可能缩小至 0.08mm(两侧走线均蚀刻不足,宽度增加 0.01mm)或扩大至 0.12mm(两侧走线均蚀刻过度,宽度减少 0.01mm)。

不同蚀刻工艺的精度与适用间距范围:

-

普通化学蚀刻:精度较低,蚀刻公差 ±0.02mm,适合最小间距≥0.15mm 的 PCB(如家电、普通工业设备);若设计间距 < 0.15mm,易出现走线粘连(短路)或间距过大(浪费空间)。

-

精细化学蚀刻:通过优化蚀刻液浓度(如氯化铁溶液浓度 38-42Be')、温度(45-50℃)、喷淋压力(2-3kg/cm²),将公差控制在 ±0.01mm,适合最小间距 0.1-0.15mm 的 PCB(如消费电子、小型传感器)。

-

激光蚀刻:精度最高,公差 ±0.005mm,可实现最小间距 0.05mm 的超细走线(如毫米波雷达、微型医疗设备 PCB),但成本较高,仅用于高端产品。

2. 阻焊层工艺:影响 “实际绝缘间距”

阻焊层(绿油)覆盖在 PCB 表面,起到绝缘、防氧化的作用,其涂覆精度会影响走线的 “有效间距”—— 若阻焊层偏移,覆盖了部分走线间距,会导致实际可利用的绝缘间距缩小;若阻焊层存在气泡、针孔,会暴露部分铜箔,增加短路风险。

阻焊层工艺对间距的要求:

-

阻焊层偏移量需≤0.05mm:设计时需在走线两侧预留 “阻焊边距”(≥0.05mm),避免阻焊偏移后覆盖间距。比如设计间距 0.1mm,需确保阻焊层与走线边缘的距离≥0.05mm,即使偏移 0.05mm,实际间距仍能保持 0.05mm 以上。

-

阻焊层厚度需均匀:厚度通常为 15-30μm,过厚可能导致相邻走线的阻焊层粘连,过薄则绝缘效果不足。对于高压 PCB(≥250V),阻焊层厚度需≥25μm,且无针孔(可通过 “高压测试” 检测,施加 1.5 倍工作电压,持续 1 分钟无击穿)。

3. 钻孔工艺:避免 “过孔与走线” 的间距违规

过孔是连接 PCB 不同层的导体,其位置精度会影响与相邻走线的间距 —— 若过孔钻孔偏移,可能导致过孔与走线的间距小于设计值,引发短路或信号干扰。

钻孔工艺的间距控制要求:

-

过孔与走线的最小间距≥0.1mm(普通工艺)、≥0.08mm(精细工艺),钻孔公差需≤±0.02mm(确保偏移后仍满足间距)。

-

对于高密度 PCB(如 BGA 封装区域),过孔直径小(0.1-0.2mm),需采用 “机械钻孔 + 激光修孔” 组合工艺,将钻孔精度控制在 ±0.01mm,避免过孔与周边细走线(0.08-0.1mm)的间距违规。

二、制造工艺的间距限制:设计需 “留足余量”

不同制造水平的厂商,其工艺能实现的最小间距不同,设计时需参考厂商的 “工艺能力表”,避免超出限制。目前行业主流的工艺限制范围:

-

低端厂商(中小批量、低成本):最小走线间距≥0.15mm,蚀刻公差 ±0.02mm,不支持 0.1mm 以下细间距。

-

中端厂商(批量消费电子):最小走线间距 0.1-0.15mm,蚀刻公差 ±0.01mm,可支持部分 0.08mm 间距(需额外收费)。

-

高端厂商(高端设备、精密电子):最小走线间距 0.05-0.1mm,蚀刻公差 ±0.005mm,支持激光蚀刻和超细间距。

设计时需 “留足工艺余量”:比如厂商宣称最小间距 0.1mm,设计时应将实际间距设为 0.12mm(增加 0.02mm 余量),抵消蚀刻、阻焊的偏差;若设计间距恰好为厂商的工艺下限,出现不良品的概率会大幅增加(如某厂商 0.1mm 间距的 PCB 不良率约 5%,0.12mm 则降至 0.5%)。

三、制造过程的质量控制:确保间距达标

1. 首件检测(First Article Inspection)

每批次 PCB 生产前,需制作首件,通过 “光学检测(AOI)” 和 “手动测量” 检查间距:

-

AOI 检测:通过高分辨率相机(2000 万像素以上)扫描 PCB,自动对比设计文件与实际产品的间距,识别间距过小、粘连等问题,检测精度可达 0.001mm。

-

手动测量:对 AOI 疑似违规的区域,用显微镜(50-100 倍)配合千分尺测量实际间距,确认是否符合设计要求(如设计 0.1mm,实际需≥0.09mm,避免低于下限)。

2. 批量抽检

批量生产中,按 5%-10% 的比例抽检 PCB,重点检查:

-

高压走线、高频走线的间距(这些区域对间距更敏感,偏差易引发故障)。

-

边缘区域的走线间距(PCB 边缘易出现蚀刻不均,导致间距偏差)。

-

过孔与走线的间距(钻孔偏移多发生在批量生产的中后期)。

3. 异常处理

若抽检发现间距违规(如实际间距 0.08mm < 设计 0.1mm),需立即停机,分析原因:

-

若为蚀刻过度:调整蚀刻液浓度(降低 5%-10%)、缩短蚀刻时间(减少 10%-15%),重新制作首件确认。

-

若为阻焊偏移:调整阻焊网版的对位精度(偏差控制在 0.02mm 以内),更换损坏的网版。

-

若为钻孔偏移:校准钻孔机的定位系统(精度校准至 ±0.005mm),更换磨损的钻头。

PCB 走线间距的实现依赖制造工艺的精度与质量控制,设计时需 “了解工艺限制、留足余量”,制造时需 “严格检测、及时纠偏”,才能确保最终产品的间距符合可靠性要求。

106

106

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?