传统PCB设计依赖经验与后期调试,成功率随速率提高而锐减。基于仿真的信号完整性设计方法通过建模预分析,将问题规避于设计前端,可缩短开发周期30%以上。

信号完整性模型构建:SPICE、IBIS与AMS对比

-

SPICE模型:基于晶体管级电路描述,精度高但需半导体工艺参数,多用于器件级分析。例如,HSPICE可精准模拟MOS管级行为,但计算量巨大。

-

IBIS模型:采用I/V曲线与V/T表描述I/O特性,无需公开电路拓扑,受供应商支持。如DDR4接口仿真中,IBIS模型误差可控制在2%以内,且计算效率为SPICE的10倍。

-

Verilog-AMS模型:支持行为级描述,适合系统级仿真。例如,SerDes链路可建模为差分方程而非电路网表,适配异构系统。表:信号完整性模型适用场景对比模型类型精度范围计算效率典型应用SPICE晶体管级±1%低关键网络时序分析IBIS接口级±5%高接口兼容性验证Verilog-AMS系统级±10%中跨域协同仿真

基于SI分析的设计流程重构

-

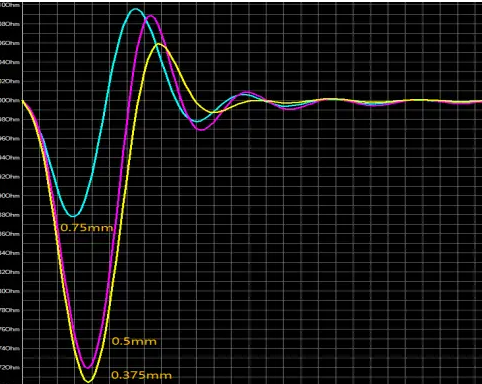

预布局阶段:解空间探索通过参数扫描确定设计边界。例如,对PCIe差分线,扫描线宽(3–6 mil)、间距(2–5 mil)、层压厚度(2–4 mil),得到阻抗-损耗曲线,确定可控参数范围。

-

约束驱动布局将电气规则(如串扰<30 mV)转换为物理规则(并行长度<500 mil)。工具如Cadence Allegro支持实时SI检查,布线时动态显示电气参数。

-

后仿真验证提取实际布线参数(线长、过孔数、拐角)反灌仿真,对比时序余量。例如,DDR5布线后需验证建立/保持时间余量>10%周期。

挑战:4×25 Gbps通道,损耗预算<3 dB@12.5 GHz。

-

措施:选用MEGTRON6板材(Df=0.004);差分线宽/间距=4/4 mil,参考地间距3 mil;过孔反焊盘扩径至0.3 mm,减小寄生电容;IBIS模型仿真确认眼图张开度>0.7 UI。

-

结果:一次投板成功,误码率<10⁻¹²。

仿真驱动的SI设计将“试错”转为“预测”,核心在于模型精度与流程整合。未来随着AI加速仿真及云平台应用,设计迭代效率有望进一步提升。下一篇文章将聚焦布线策略的具体实施。

180

180

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?