PCB 走线间距的设计是 “理论标准” 与 “实际需求” 的平衡过程 —— 既要满足电压、信号、环境的要求,又要兼顾 PCB 尺寸、制造成本的限制。设计阶段若间距规划不当,后期修改可能导致大面积重新布线,甚至 PCB 尺寸调整。

一、走线间距规则制定:先 “分类” 再 “量化”

设计前需先按 “电压等级”“信号类型”“功能模块” 对走线分类,再为每类制定明确的间距标准,避免 “一刀切” 式的间距设定(要么浪费空间,要么存在风险)。

1. 按电压等级分类制定间距

根据 PCB 上的电压范围,将走线分为低压、中压、高压三类,对应不同间距:

-

低压走线(≤30V,如芯片供电、控制信号):最小间距 0.1-0.15mm,适合消费电子、小家电等场景;若 PCB 尺寸紧张,可压缩至 0.08mm(需确认制造厂商的蚀刻精度能否达标,通常要求蚀刻公差 ±0.01mm 以内)。

-

中压走线(30V-250V,如工业设备的 24V 直流、110V 交流):最小间距 0.5-1mm,需在走线两侧预留 “安全边距”,避免与其他走线交叉;若存在裸露焊盘,焊盘与相邻走线间距需比线线间距大 50%(如线线间距 0.5mm,焊盘与线间距≥0.75mm)。

-

高压走线(≥250V,如 220V 交流、高压电源模块):最小间距≥1.5mm,且需与其他走线之间设置 “隔离带”(宽度≥1mm 的空白区域或接地铜皮),防止高压信号通过耦合干扰其他电路;若 PCB 表面有阻焊层,可适当放宽间距(但仍需≥1mm),无阻焊层则需增加 20% 间距。

2. 按信号类型分类制定间距

不同信号的干扰特性不同,需针对性设定间距,尤其避免高频信号、强功率信号干扰敏感信号:

-

高频信号(≥100MHz,如射频、时钟信号):与其他非同类信号的间距≥5 倍线宽(如线宽 0.2mm,间距≥1mm);若为差分信号(如 DDR5、5G 射频),需保持 “等间距平行布线”,差分对内部间距为线宽的 2-3 倍(如线宽 0.2mm,对内间距 0.4-0.6mm),差分对与外部走线间距≥10 倍线宽(≥2mm),减少串扰。

-

功率信号(如电机驱动、电源输出):电流越大,间距需越大(避免导线过热导致绝缘老化),比如 1A 电流的功率线间距≥0.2mm,5A 电流≥0.5mm,10A 电流≥1mm;同时,功率线与信号线间距≥2mm,防止功率波动干扰信号。

-

敏感信号(如模拟信号、传感器信号):与高频、功率信号的间距≥3mm,且需在敏感信号两侧布接地铜皮(铜皮与信号线间距 0.1-0.2mm),形成 “屏蔽走廊”;若敏感信号为小信号(如 mV 级传感器输出),间距需进一步增大至 5mm 以上,避免耦合噪声超过信号本身幅度。

二、设计软件中的间距设置:从 “规则定义” 到 “实时检查”

主流 PCB 设计软件(如 Altium Designer、Cadence Allegro、KiCad)都支持 “自定义间距规则”,需按分类设置参数,并开启实时 DRC(设计规则检查),避免违规布线。

以 Altium Designer 为例,具体操作步骤如下:

打开 “Design Rules” 对话框,在 “Electrical”→“Clearance” 中新建规则,按电压、信号类型命名(如 “LowVoltage_Clearance”“HighFreq_DiffPair”)。

为每个规则设置 “适用对象”:比如 “LowVoltage_Clearance” 适用于 “Net Class” 中的 “LowVoltage_Nets”(提前将所有低压网络归为一类),“HighFreq_DiffPair” 适用于 “Diff Pair Class” 中的 “RF_DiffPairs”。

设定 “最小间距值”:如低压规则设为 0.1mm,高压规则设为 1.5mm,差分对内间距设为 0.4mm;同时设置 “例外规则”,比如 “高压走线与接地铜皮的间距可放宽至 0.8mm”(接地铜皮能降低爬电风险)。

开启实时 DRC:在软件右下角勾选 “DRC”,布线时若间距违规,会显示红色警示线;完成布线后,执行 “Tools”→“Design Rule Check”,生成 DRC 报告,逐一排查违规项(重点关注高压、高频信号的间距问题)。

需注意,软件默认的间距规则可能不符合实际需求(如默认 0.2mm,不区分电压、信号),必须根据产品特性自定义,否则易出现设计漏洞。

三、常见设计误区:避开 “安全隐患” 与 “性能陷阱”

误区 1:为压缩 PCB 尺寸,无限制缩小间距。某智能手表 PCB 设计中,将 3.7V 电源走线与 I2C 信号线间距设为 0.06mm(低于厂商蚀刻精度 0.08mm 的下限),导致生产时 15% 的 PCB 出现短路,不得不重新修改设计、增大间距至 0.1mm,延误量产周期。

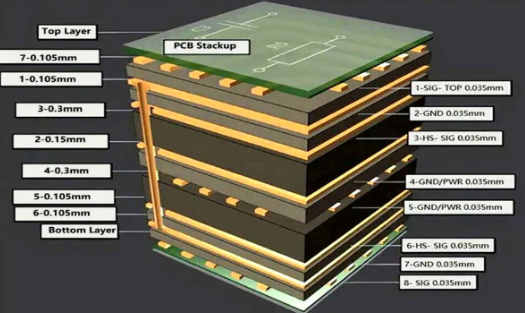

误区 2:忽略 “跨层走线” 的间距。多层 PCB 中,相邻层的走线若在垂直方向重叠,即使表层间距合格,也可能因层间电容耦合产生干扰。正确做法是:相邻层的高频走线、敏感走线避免垂直重叠,若无法避免,需在两层之间增加接地层,或增大垂直投影间距(≥0.5mm)。

误区 3:间距规则 “一刀切”。某工业 PLC PCB 设计中,将所有走线间距统一设为 0.3mm,导致 220V 高压走线与 5V 信号线间距不足,设备运行时出现信号杂波,后来将高压与信号线间距调整为 2mm,杂波问题解决。

PCB 走线间距设计需 “分类施策、软件落地、规避误区”,既要基于理论标准,又要结合实际场景灵活调整,通过规则化设计和实时检查,确保每一处走线间距都符合可靠性要求。

100

100

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?