用于低功耗和安全边缘计算的近似绝热逻辑

摘要

近似计算是一种有前景的方法,可用于在物联网(IoT)边缘设备上运行的容错应用以降低功耗。然而,近似计算容易受到侧信道攻击的影响,例如基于差分功耗分析(DPA)的攻击。通过在近似边缘计算中应用绝热逻辑,不仅可以进一步提升能效,还能增强对侧信道攻击的防护能力。作为案例研究,本文提出了两种基于绝热逻辑的近似加法器,以展示近似计算与绝热逻辑结合的优势。所提出的近似加法器利用绝热逻辑的双轨特性,以减小整体面积并进一步降低能耗。本文中,第一个设计为真和近似加法器(TSAA),第二个设计为真进位近似加法器(TCAA)。基于绝热逻辑的TSAA和TCAA相比基于CMOS的精确镜像加法器(AMA)使用的晶体管更少。在12.5 MHz工作频率和45纳米工艺节点下,绝热逻辑TSAA和TCAA相较于标准CMOS AMA实现了95.4%和95.48%的功耗节省,以及90.80%和90.96%的能耗节省。我们还表明,这两种设计在抵御DPA攻击方面更加安全。

一、引言

物联网边缘计算的发展使得处理在网络边缘进行,这需要更高能效和增强的安全解决方案[1],[2]。低功耗电路设计的新兴策略包括绝热逻辑和近似计算。在近似计算中,精度被作为降低面积的权衡。这对于在物联网边缘设备上运行的容错应用程序具有前景。然而,网络安全解决方案

尚未完全解决[3],[4]。在[3], 中,作者指出,近似加法器的输出与功耗之间存在正相关关系,且随着误差率的增加而增强。此外,由于非近似电路(如密码学电路)相较于近似电路运行在较低频率或较低供电电压下,逆向工程将更容易[4]。攻击者可能对近似电路发起多种攻击,例如侧信道攻击和逆向工程[4],[5]。

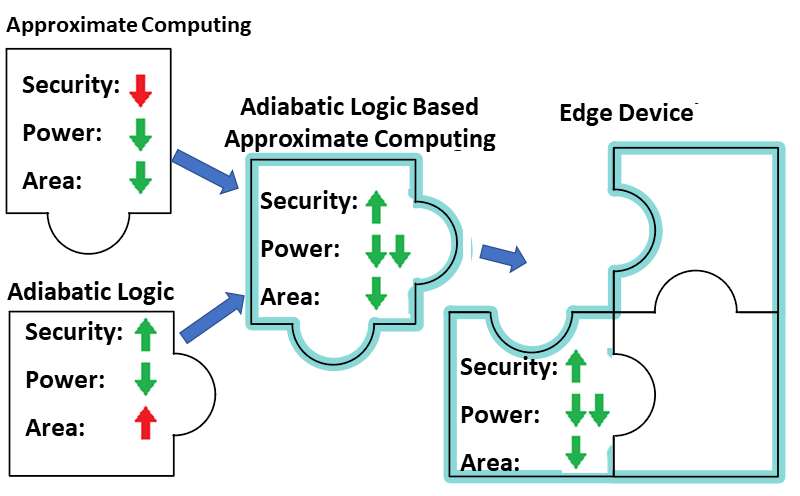

绝热逻辑通过回收负载电容[6]中存储的能量来实现高能效计算。本质上,绝热逻辑家族大多是双轨的。因此,与标准CMOS相比,绝热设计的晶体管数量更多。本文将展示,通过在绝热逻辑中使用近似计算,可以生成高能效、低功耗且面积更小的电路(图1)。我们将通过案例研究进行演示

全加器的近似电路在采用绝热逻辑实现时,能够提供对差分功耗分析(DPA)攻击等侧信道攻击的抵抗能力。

本文表明,双轨绝热逻辑可用于全加器中以近似总和或进位输出。这将有助于设计具有较少晶体管的高能效、低功耗和安全电路。本文提出的两种近似全加器设计为真和近似加法器(TSAA)和真进位近似加法器(TCAA)。

tsaa基于精确的 Sum对 Carryout进行近似,类似地,tcaa基于精确的 Carryout对Sum进行近似。为了实现这两种近似加法器,采用了高能效安全正反馈绝热逻辑(EE‐SPFAL)[7]。

仿真结果表明,基于EE‐SPFAL的TCAA设计比基于EE‐SPFAL的TSAA设计具有更高的节能性、更低的误差和更小的面积。我们还说明,基于EE‐SPFAL的TSAA比基于EE‐SPFAL的TCAA更安全。

二、背景

A. 能量回收原理

在当前的CMOS技术中,为了给电容为 CL 的输出节点充电,电源需要提供 CLV²dd 的能量。在 CLV²dd 的能量中,仅有1/2 CLV²dd 的能量被存储在电容CL中,而另一半能量则在由晶体管沟道构成的路径中耗散。与传统的CMOS电路不同,能量回收电路采用绝热开关原理,通过逐步为电容充电并在每个周期结束时回收电荷,从而实现低功耗,属于低能量电路[6]。

B. 基于功耗分析的侧信道攻击

侧信道攻击可以根据从加密硬件获取的信息来揭示密钥。侧信道攻击包括功耗攻击、时序攻击和电磁攻击等。其中,功耗分析攻击可分为简单功耗分析(SPA)、差分功耗分析 (DPA)和相关功耗分析(CPA)。简单功耗分析 (SPA):攻击者通过直接观察设备的功耗来确定所使用的加密算法的密钥。差分功耗分析 (DPA):一种侧信道攻击,通过统计分析处理数据与功耗轨迹之间的相关性来揭示加密设备的密钥。相关功耗分析(CPA):DPA的增强形式,通过使用功耗轨迹与密钥猜测中间结果值之间的统计相关系数来推导出正确密钥。这些攻击通常结合假设功耗模型来揭示密钥。

III. 提出的电路设计

高能效安全正反馈绝热逻辑(EE‐SPFAL)[7]是一种适用于设计低功耗和安全绝热电路的绝热逻辑家族。EE‐SPFAL具有均匀功耗,能够抵御基于差分功耗分析(DPA)的攻击。

图2展示了EE‐SPFAL的通用原理图,其中模块 F和模块F分别生成 Output和Output。关于绝热逻辑的更详细背景信息可参见近期的一篇文章[6]。我们提出了两种基于EE‐SPFAL的绝热近似加法器(AAA)版本。产生 Output 和 Output的功能模块分别为模块F和模块 F(图2)。因此,为了最小化总面积并降低功耗和能耗,所提出的两种近似加法器利用互补输出来近似总和或进位输出。由此,开发了两种近似加法器,即基于公式1的真和近似加法器(TSAA)和基于公式2的真进位近似加法器(TCAA)。

$$

F = \text{Sum} \quad F = \text{Sum} = \text{Cout} \tag{1}

$$

$$

F = \text{Cout} \quad F = \text{Cout} = \text{Sum} \tag{2}

$$

A. 真和近似加法器(TSAA)

基于EE‐SPFAL的tsaa示意图如图3所示,其中 Cout是 Sum的补码。我们利用绝热逻辑的双轨特性,将 Cout设计为 Sum的补码(公式3)。因此,我们无需单独的电路来计算 Cout和Cout。

$$

\text{Sum}

{TSAA} = A \oplus B \oplus C \quad \text{Cout}

{TSAA} = \text{Sum}_{TSAA} \tag{3}

$$

B. 真进位输出近似加法器(TCAA)

基于EE‐SPFAL的TCAA示意图如图4所示。在TCAA中, $\text{Sum} {TCAA}$ 被计算为 $\text{Cout} {TCAA}$(公式4)。因此,我们消除了对单独电路生成总和输出的需求。

$$

\text{Cout}

{TCAA} = B \cdot C + A \cdot C + A \cdot B \quad \text{Sum}

{TCAA} = \text{Cout}_{TCAA} \tag{4}

$$

IV. 仿真结果与讨论

为便于比较,本节使用基于EE‐SPFAL的 TSAA和TCAA、基于CMOS的精确镜像加法器 (AMA)[8]以及基于CMOS的近似镜像加法器[9]。所提出的设计在功耗、能量、面积以及针对差分功率分析(DPA)攻击的安全性方面进行了评估。仿真采用45纳米技术进行。CMOS仿真中, PMOS的宽度设为240纳米,NMOS的宽度设为 120纳米;EE‐SPFAL仿真中,PMOS的宽度设 为360纳米,NMOS的宽度设为120纳米。

A. 不同频率下的仿真

我们使用梯形波形作为输入来模拟电路。在10飞法拉下,功耗和能耗随频率变化的情况分别如表I和表II所示。表I和表II的结果表明,基于EE‐SPFAL的TCAA比基于EE‐SPFAL的 TSAA更节能高效。与基于EE‐SPFAL的 TSAA、基于CMOS的AMA[8]以及基于 CMOS的近似镜像加法器[9]相比,基于 EE‐SPFAL的TCAA具有最低的功耗和能耗。[9]中提出的四种基于CMOS的近似加法器在表I和表II中表示为CMOS Apx1、CMOSApx2、 CMOS Apx3和CMOS Apx4。与标准基于 CMOS的AMA相比,基于EE‐SPFAL的TSAA 实现了

功耗。(b) 每周期能耗。)

在12.5 MHz时功耗节省95.40%和能耗节省 90.80%。与标准基于CMOS的AMA相比,基于 EE‐SPFAL的TCAA分别实现了95.48%的功耗节省和90.96%的能耗节省。相比之下,基于 EE‐SPFAL的TCAA在较高频率下比基于 EE‐SPFAL的TSAA节省更多。

表I:基于EE‐SPFAL的提出电路设计与基于 CMOS的加法器在不同频率下的功耗(纳瓦)。

| 频率(MHz) | 1 | 12.5 | 25 | 50 |

|---|---|---|---|---|

| CMOS AMA[8] | 25.46 | 273.2 | 440.5 | 786.8 |

| CMOS Apx1[9] | 17.98 | 201.0 | 344.0 | 559.8 |

| CMOS Apx2[9] | 17.16 | 207.8 | 415.2 | 762.1 |

| CMOS Apx3[9] | 11.39 | 138.9 | 278.3 | 557.5 |

| CMOS Apx4[9] | 15.12 | 171.2 | 313.6 | 591.7 |

| EE‐SPFAL TSAA | 0.539 | 12.57 | 33.28 | 88.97 |

| EE‐SPFAL TCAA | 0.542 | 12.35 | 32.54 | 86.83 |

表II:基于EE‐SPFAL的提出电路设计和基于 CMOS的加法器在不同频率下的每周期能量(fJ/周期)。

| 频率(MHz) | 1 | 12.5 | 25 | 50 |

|---|---|---|---|---|

| CMOS AMA[8] | 12.73 | 10.93 | 8.810 | 7.868 |

| CMOS Apx1[9] | 8.991 | 8.043 | 6.880 | 5.598 |

| CMOS Apx2[9] | 8.581 | 8.313 | 8.304 | 7.621 |

| CMOS Apx3[9] | 5.695 | 5.558 | 5.566 | 5.575 |

| CMOS Apx4[9] | 7.558 | 6.846 | 6.273 | 5.916 |

| EE‐SPFAL TSAA | 0.539 | 1.006 | 1.331 | 1.780 |

| EE‐SPFAL TCAA | 0.541 | 0.988 | 1.301 | 1.736 |

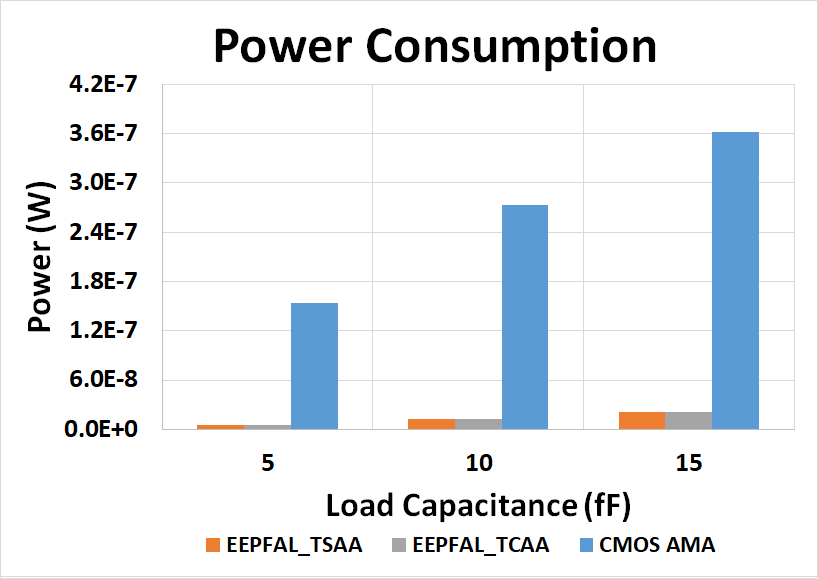

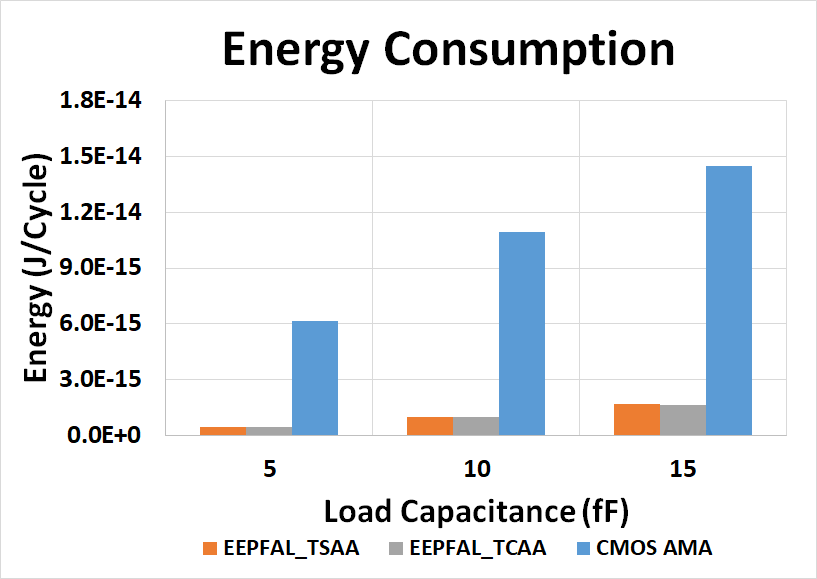

B. 不同负载电容下的仿真

我们进行了进一步的仿真,通过在12.5 MHz下调整负载电容来测试所提出的绝热近似加法器的驱动强度。图5(a)和(b)显示,基于 EE‐SPFAL的TCAA比基于EE‐SPFAL的TSAA具有更高的功耗和能量效率。表III和表IV列出了基于EE‐SPFAL的TSAA和基于EE‐SPFAL的TCAA 的功耗与能量比较结果。当负载电容为15 fF时,基于EE‐SPFAL的TSAA和基于EE‐SPFAL的 TCAA的功耗分别为21.1 nW和20.62 nW。此外,当负载电容为15 fF时,基于EE‐SPFAL的TSAA和基于EE‐SPFAL的TCAA的每周期能量分别为 1.689 fJ/周期和1.649 fJ/周期。仿真验证了基于 EE‐SPFAL的TCAA相较于基于EE‐SPFAL的 TSAA对负载电容变化的敏感性更低。

表III:不同负载电容下CMOS AMA、基于 EE‐SPFAL的TSAA和基于EE‐SPFAL的TCAA的功耗(纳瓦)。

| 负载电容(飞法) | 5 | 10 | 15 |

|---|---|---|---|

| CMOS AMA[8] | 153.8 | 273.2 | 362.5 |

| EE‐SPFAL TSAA | 5.918 | 12.57 | 21.10 |

| EE‐SPFAL TCAA | 5.916 | 12.35 | 20.62 |

表IV:CMOS AMA、基于EE‐SPFAL的tsaa和基于 EE‐SPFAL的TCAA在不同电容负载下的每周期能量(飞焦/周期)

| 负载电容(飞法) | 5 | 10 | 15 |

|---|---|---|---|

| CMOS AMA[8] | 6.15 | 10.93 | 14.50 |

| EE‐SPFAL TSAA | 0.473 | 1.006 | 1.689 |

| EE‐SPFAL TCAA | 0.473 | 0.988 | 1.649 |

C. 抗差分功耗分析攻击能力

我们展示了基于EE‐SPFAL的TCAA和 TSAA的仿真结果,以评估它们抵抗差分功耗分析攻击的能力。仿真在45 nm工艺节点上进行,负载电容为10飞法拉。图6显示了基于 EE‐SPFAL的TCAA和TSAA加法器的均匀电流特性。为了确定TCAA和TSAA抵抗DPA攻击的能力,针对所有可能的输入组合计算了两个参数。第一个参数是归一化能量偏差(NED),即最小与最大能耗之间的百分比差异;第二个参数是归一化标准偏差(NSD),表示能耗变化。计算NED和NSD的公式如公式5所示;其中 σE为能耗的标准差, Eavg为平均能耗。表V展示了TCAA和tsaa的归一化能量偏差与归一化标准偏差值。基于EE‐SPFAL的TSAA具有更低的归一化能量偏差和归一化标准偏差值,表明基于 EE‐SPFAL的TSAA比基于EE‐SPFAL的TCAA具有更均衡的能耗且更安全。基于EE‐SPFAL的TCAA的归一化能量偏差和归一化标准偏差值较大,这是由于在不同输入情况下固有电容发生变化所致。我们发现,增加基于EE‐SPFAL的TCAA的负载电容可以改善其归一化能量偏差和归一化标准偏差值。然而,基于 EE‐SPFAL的TCAA的归一化能量偏差和归一化标准偏差值仍比基于EE‐SPFAL的TSAA高出30多倍。

$$

\text{NED} = \frac{E_{\text{max}} - E_{\text{min}}}{E_{\text{max}}} \times 100\%

\quad

\text{NSD} = \frac{\sigma_E}{E_{\text{avg}}} \times 100\% \tag{5}

$$

表V:TSAA和TCAA的归一化能量偏差和归一化标准偏差。

| TCAA | TSAA | |

|---|---|---|

| $E_{\text{max}}$(J) | 1.41E‐15 | 1.53E‐15 |

| $E_{\text{min}}$(J) | 1.60E‐15 | 1.54E‐15 |

| 归一化能量偏差(%) | 11.83 | 0.275 |

| 归一化标准偏差(%) | 3.660 | 0.102 |

D. 晶体管数量评估

传统的基于CMOS的精确镜像加法器( AMA)[8],、基于CMOS的近似镜像加法器[9],、基于EE‐SPFAL的TSAA和基于EE‐SPFAL的 TCAA的晶体管数量如表VI所示。从表VI可以看出,两种提出的电路设计相比CMOS AMA均具有更少的晶体管数量。其中,基于EE‐SPFAL的 TSAA减少了33%的晶体管,基于EE‐SPFAL的 TCAA减少了41.7%的晶体管。

表VI:基于EE‐SPFAL的TSAA、TCAA和基于 CMOS的加法器的晶体管数量

| PMOS | NMOS | 总计 | |

|---|---|---|---|

| CMOS AMA[8] | 12 | 12 | 24 |

| CMOSapx1[9] | 8 | 8 | 16 |

| CMOSapx2[9] | 7 | 7 | 14 |

| CMOSapx3[9] | 6 | 5 | 11 |

| CMOSapx4[9] | 5 | 6 | 11 |

| EE‐SPFAL TSAA | 2 | 14 | 16 |

| EE‐SPFAL TCAA | 2 | 12 | 14 |

E. 平均误差距离

在本节中,我们将介绍所提出的两种加法器的精度。均值误差距离(MED)是用于确定近似电路精度的度量标准。精度与 MED 值成反比,MED 值越小,近似电路的精度越高。MED 值通过公式 6 计算得出;其中误差距离(ED)是给定输入下精确输出与近似输出之间的差值,P 是 ED 的概率,n 是加法器的位数。

$$

\text{ED} = |\text{Out}

{\text{acu}} - \text{Out}

{\text{apx}}|

\quad

\text{MED} = \sum_n \text{ED}_s^n \times P(\text{ED}_s^n) \tag{6}

$$

表VII:基于EE‐SPFAL的TSAA、TCAA和基于CMOS的近似加法器的平均误差距离值。

| 1位加法器 | 4位加法器 | |

|---|---|---|

| CMOSapx1[9] | 0.250 | 2.719 |

| CMOSapx2[9] | 0.250 | 3.617 |

| CMOSapx3[9] | 0.500 | 4.426 |

| CMOSapx4[9] | 0.375 | 5.000 |

| EE‐SPFAL TSAA | 0.500 | 5.515 |

| EE‐SPFAL TCAA | 0.250 | 3.617 |

V. 结论

我们阐明了通过近似计算与绝热逻辑的结合,可以为边缘计算开发低功耗且安全的解决方案。基于双轨绝热逻辑,提出了两种新型的绝热近似加法器。研究结果表明,与传统 CMOS设计相比,基于绝热逻辑的近似加法器在功耗和能耗方面显著降低。此外,它们还具有抗差分功耗分析攻击能力。结论指出,所提出的绝热真进位输出近似加法器(TCAA)能够提供更高的节能与降耗,晶体管数量更少,且精度更高。然而,绝热真和近似加法器(TSAA)具有更强的抗差分功耗分析攻击能力。

近似绝热加法器在边缘计算的应用

近似绝热加法器在边缘计算的应用

582

582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?