提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

本文将结合ip example工程来理解transceiver的复位,通过学习记录,力求将其复位过程理解通透。

参考工程为serdes_3g

复位模式

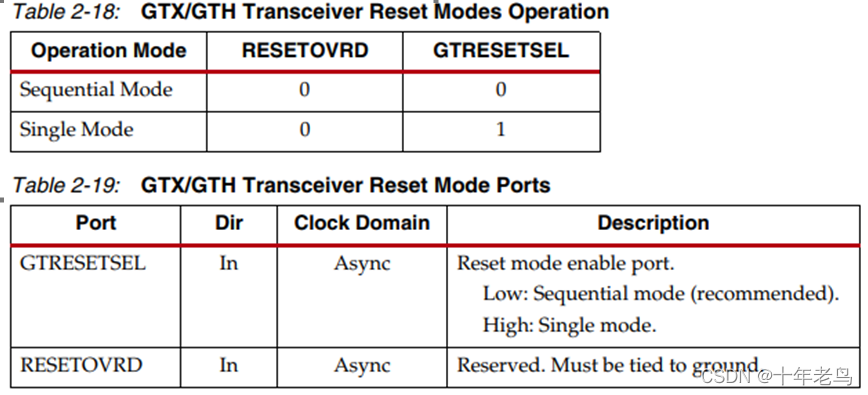

手册中提到了两种复位模式

复位模式

1、顺序模式

2、单步模式

在ip example中,是直接使用顺序模式的,而且手册也是推荐使用顺序模式,那么我们就直接研究顺序模式了,单步模式暂时不关注

//-------------------- Transceiver Reset Mode Operation --------------------

.GTRESETSEL (tied_to_ground_i

本文详细探讨了Xilinx FPGA中Transceiver的复位机制,特别是QPLL和TX链路的复位过程。通过分析GTWizard_0_TX_STARTUP_FSM模块,揭示了复位状态机的工作流程,包括QPLL锁定、GTTXRESET和TXUSERRDY的控制。文中还强调了在顺序模式下复位时的各项条件,并指出在实际应用中,通常仅使用GTTXRESET进行复位操作。

本文详细探讨了Xilinx FPGA中Transceiver的复位机制,特别是QPLL和TX链路的复位过程。通过分析GTWizard_0_TX_STARTUP_FSM模块,揭示了复位状态机的工作流程,包括QPLL锁定、GTTXRESET和TXUSERRDY的控制。文中还强调了在顺序模式下复位时的各项条件,并指出在实际应用中,通常仅使用GTTXRESET进行复位操作。

订阅专栏 解锁全文

订阅专栏 解锁全文

9689

9689

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?