1、参考标准:

Reduced Gigabit Media Independent Interface (RGMII), HP Company, V2.0 2002.4.1

2、接口概述:

RGMII接口提供了MAC和PHY之间的一种连接选择。它只需要12根信号线就可以完成GMII接口所能完成的功能。为了达到减少管脚的目的,其数据及控制信号的时钟参考沿改变为DDR的形式。

3、信号数量:

RGMII接口共12根信号线,发送时钟数据信号线1根,发送数据信号线4根,发送控制信号线1根;接收时钟数据信号线1根,接收时钟信号线4根,接收控制信号线1根。信号的名称,信号流向以及信号描述见下表:

| 信号名 | 信号流向 | 信号描述 |

| TXC | MAC→PHY | 发送时钟信号。速率为Gbit/s时,时钟速率为125MHz;速率为100Mbit/s时,速率为25MHz,速率为10Mbit/s时,速率为2.5MHz。精度要求为±50ppm |

| TD[3:0] | MAC→PHY | 发送数据信号,在时钟上升沿时为bit[3:0],时钟下降沿时为bit[7:4]。 |

| TX_CTL | MAC→PHY | 发送控制信号,在时钟上升沿时为TXEN,时钟下降沿时为TXERR。 |

| RXC | PHY→MAC | 接收时钟信号,速率为Gbit/s时,时钟速率为125MHz;速率为100Mbit/s时,速率为25MHz,速率为10Mbit/s时,速率为2.5MHz。精度要求为±50ppm |

| RD[3:0] | PHY→MAC | 接收数据信号,在时钟上升沿时为bit[3:0],时钟下降沿时为bit[7:4]。 |

| RX-CTL | PHY→MAC | 接收控制信号,在时钟上升沿时为RXDV,时钟下降沿时为RXERR。 |

4、信号电平:

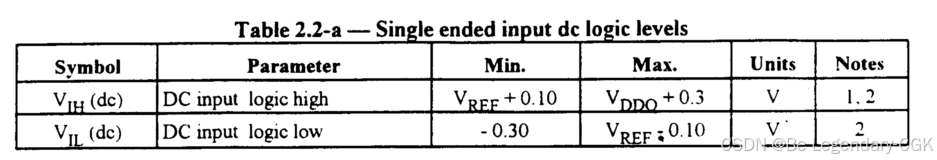

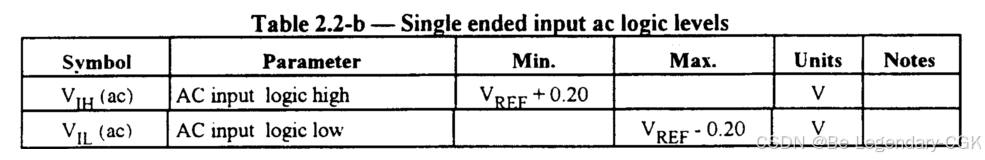

RGMII接口规范V2.0中规定:信号电平符合JESD8-6规范的中Class 1的驱动器和接收器的标准。下表中给出其接收端的信号电平指标。

说明:VDDQ一般为1.5V,VREF一般为VDDQ*0.5.

说明:VDDQ一般为1.5V,VREF一般为VDDQ*0.5.

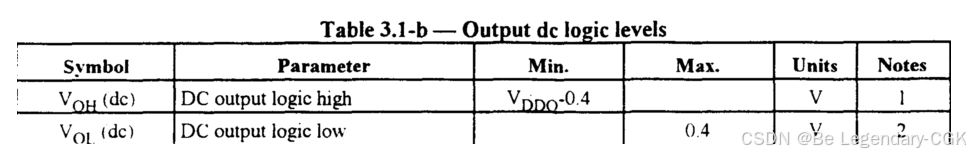

其发送端的电平指标应满足一下指标:

其发送端的电平指标应满足一下指标:

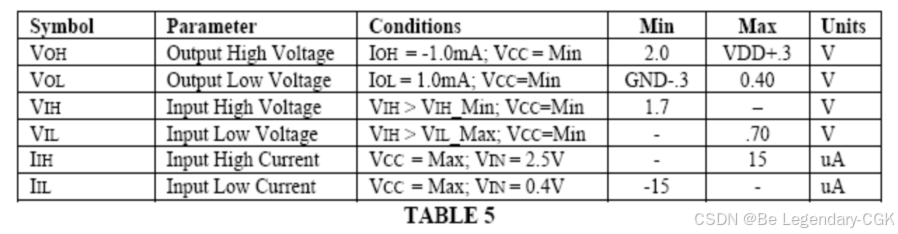

但是,目前我们使用的芯片的RGMII接口均使用的2.5V的CMOS接口,使用该信号电平时,其发送和接收的电平参数应满足RGMII V1.3a的规范标准,下表给出了当RGMII接口工作与2.5V的CMOS接口时,应满足的电平参数指标。

但是,目前我们使用的芯片的RGMII接口均使用的2.5V的CMOS接口,使用该信号电平时,其发送和接收的电平参数应满足RGMII V1.3a的规范标准,下表给出了当RGMII接口工作与2.5V的CMOS接口时,应满足的电平参数指标。

5、PCB及原理设计要求:

5、PCB及原理设计要求:

规范中未对RGMII的原理设计提出要求。但是在设计中应该根据走线长短及芯片特性加入串接电阻以改善信号指标。

对于关于PCB的Layout,应注意以下几点:

(1)若芯片中未集成CLK信号的延迟调整的功能时,CLK信号线相对于数据信号线需要在PCB布线长度上增加1.5ns至2.0ns的延迟,以满足RGMII时序指标的要求。

(2)AC和PHY之间走线的特性阻抗应控制在50欧。

(3)数据信号间的走线长度差别应不大于9.8mm,以确保数据的Skew指标小于0.07ns。

(4)接收信号及发送信号应相互远离,并且信号线在布线时应远离模拟及时钟信号以降低串绕。

6、信号速率与带宽:

当RGMII接口工作与千兆模式时,RGMII接口的时钟信号为125MHz,由于采用DDR的接口形式,故数据速率将乘以2。由于有4根数据线,故单向的数据带宽为1000兆。当工作于全双工模式时,双向带宽为2000兆。

7、编码方式及对应传输帧格式:

RGMII接口的编码形式同GMII接口。其与GMII不同点主要在于:

(1)RGMII采用双沿采样,在上升沿时,传送的数据为bit[3:0],在下降沿时,传送的数据为bit[7:4]。

(2)发送控制信号在上升沿时代表的含义为TXEN,在下降沿时代表的数据为TXERR;接收控制信号在上升沿时代表的含义为RXDV,在下降沿时代表的含义为RXERR。

TXERR的定义为:GMII_TX_ER(XOR)GMII_TX_EN

RXERR的定义为:GMII_RX_ER(XOR)GMII_RX_DV

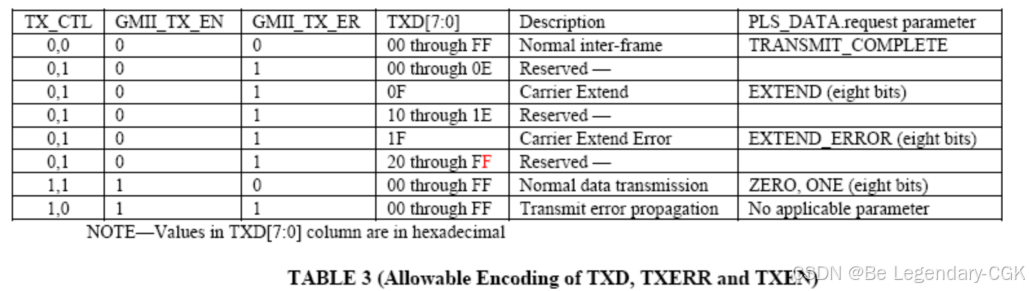

下面给出了TXD,TXERR,TXEN所允许的编码内容:

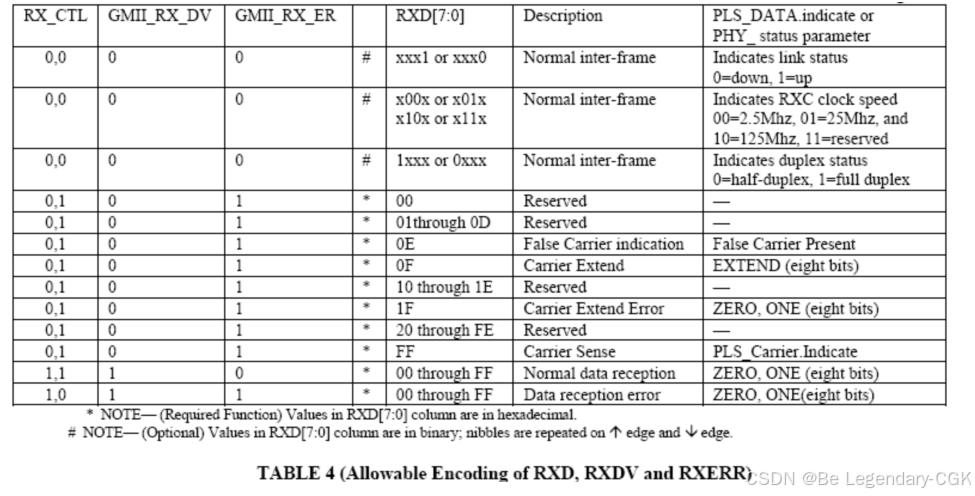

下面给出了RXDV,RXERR,RXD所允许的编码内容:

下面给出了RXDV,RXERR,RXD所允许的编码内容:

8、测试指标:

8、测试指标:

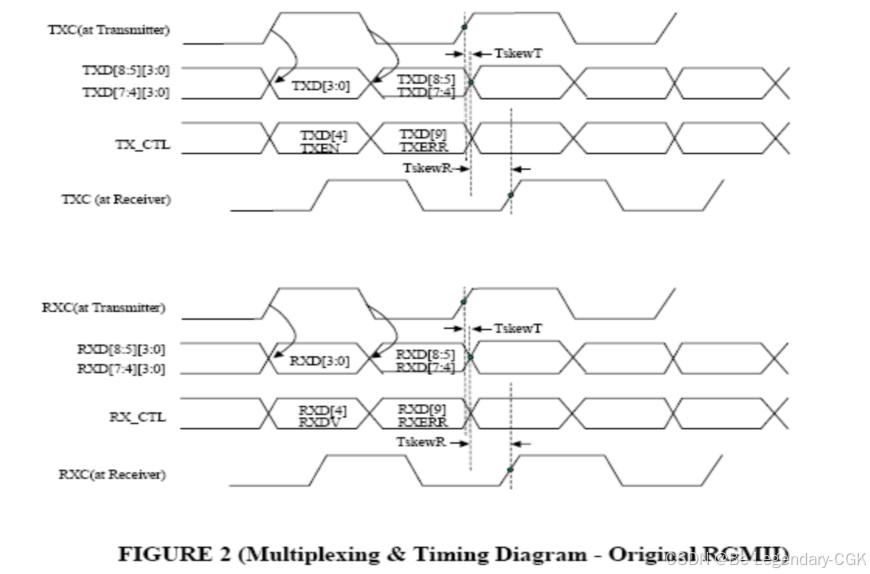

对于RGMII接口,在信号的发送端,时钟和数据是同时变化,但在数据的接收端,数据在时钟的上升或下降沿采样,故要求在PCB布线时,CLK信号要比数据信号多引入大于1.5ns,小于2ns的时延。RGMII接口的信号波形示意图如下:

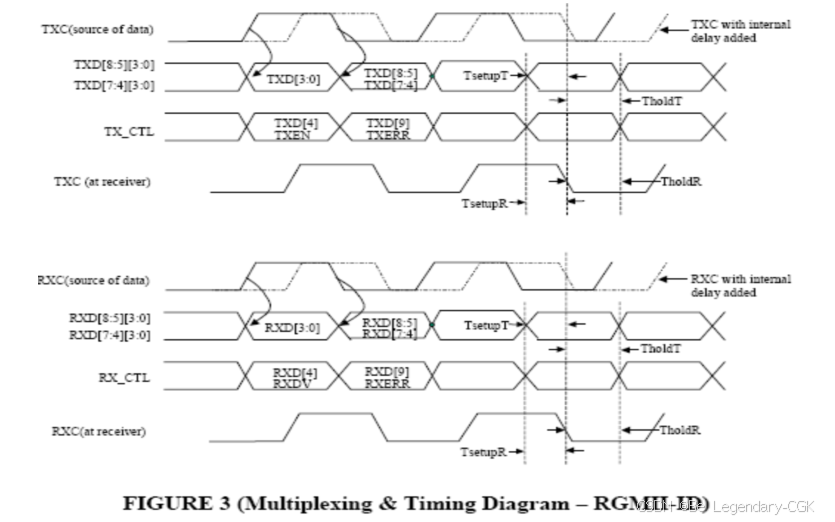

在V2.0的RGMII规范中,允许在RGMII接口器件的内部,对CLK信号增加额外的延迟。这样的好处在于在PCB走线时,只要数据信号和时钟信号等长处理即可,不需要进行额外的延迟处理。RGMII接口规范中也给出了RGMII接口器件中集成了CLK延迟功能的时序示意图:

在V2.0的RGMII规范中,允许在RGMII接口器件的内部,对CLK信号增加额外的延迟。这样的好处在于在PCB走线时,只要数据信号和时钟信号等长处理即可,不需要进行额外的延迟处理。RGMII接口规范中也给出了RGMII接口器件中集成了CLK延迟功能的时序示意图:

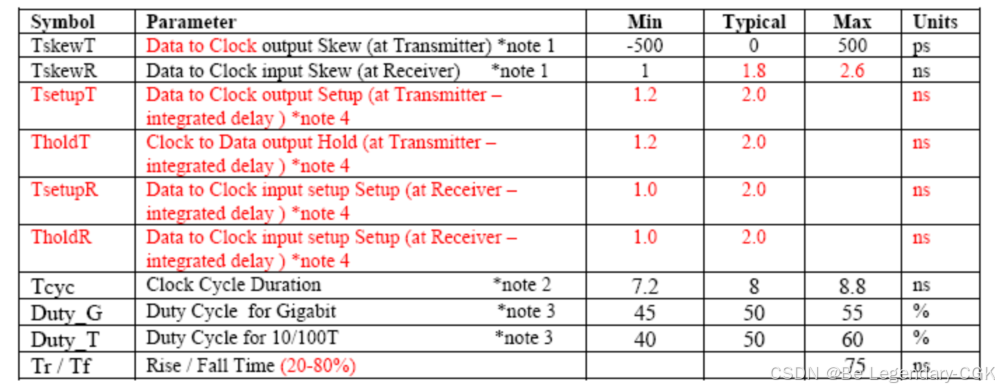

规范中给出了RGMII接口的测试指标,见下表:

规范中给出了RGMII接口的测试指标,见下表:

9、测试方法

RGMII接口测试表格:

| 测试项 | 测试参考指标 | 测试点 | 测试结果 | 备注 | |

| TXD测试 | 高电平 | >1.7V(2.5V标准) >0.95V(1.5V标准) | 输入端 | ||

| 低电平 | <0.7V(2.5V标准) <0.55V(1.5V标准) | 输入端 | |||

| TXCLK周期 | (7.2ns,8.8ns) | 输入端 | |||

| TXCLK占空比 | (0.4,0.6) | 输入端 | |||

| CLK上升时间 | <0.75ns | 输入端 | 20%-80% | ||

| CLK下降时间 | <0.75ns | 输入端 | 20%-80% | ||

| Setup Time | >1.0ns | 输入端 | |||

| Hold Time | >1.0ns | 输入端 | |||

| RXD测试 | 高电平 | >1.7V(2.5V标准) >0.95V(1.5V标准) | 输入端 | ||

| 低电平 | <0.7V(2.5V标准) <0.55V(1.5V标准) | 输入端 | |||

| RXCLK周期 | (7.2ns,8.8ns) | 输入端 | |||

| RXCLK占空比 | (0.4,0.6) | 输入端 | |||

| CLK上升时间 | <0.75ns | 输入端 | 20%-80% | ||

| CLK下降时间 | <0.75ns | 输入端 | 20%-80% | ||

| Setup Time | >1.0ns | 输入端 | |||

| Hold Time | >1.0ns | 输入端 | |||

说明:实际测试中的测试指标以芯片DATASHEET为准。

10、应用环境:

RGMII接口应用于千兆MAC和千兆PHY之间的连接。

1394

1394

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?