目录

欢迎订阅FPGA/MATLAB/Simulink系列教程

1.卷积编码原理

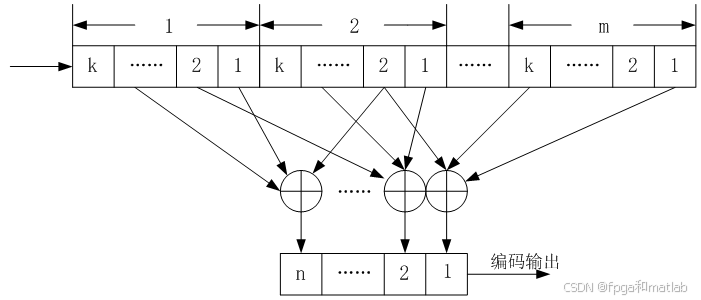

卷积编码是一种前向纠错编码方式,通过卷积算子将信息序列映射成冗余度更高的码字序列,以提高数据传输的可靠性。在通信领域,卷积码编码器一般用(n, k, m)来描述 ,其中:

k:每次输入到卷积编码器的 bit 数。

n:每个 k 元组码字对应的卷积码输出 n 元组码字。

m:编码存储度,即卷积编码器中 k 元组的级数,m + 1 称为编码约束度 ,m 称为约束长度。

因此,卷积码的编码器的形式可以表示为:

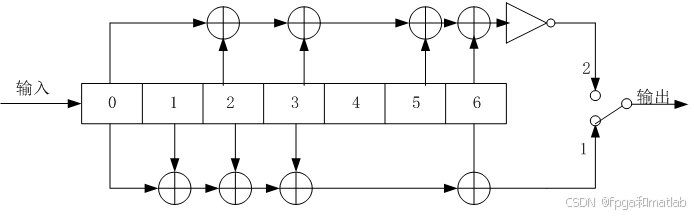

以(2, 1, 7)卷积码为例:

k = 1:表示每次输入到卷积编码器的信息比特为 1 位。

n = 2:表示每输入1个信息比特,会输出2个编码比特。

m = 7:说明编码存储度为7,即编码器的输出不仅与当前输入的信息比特有关,还与前面 6 个输入的信息比特有关(因为约束长度 m 表示与当前输入相关联的前面的段数 )。

卷积码编码器的核心部件包括移位寄存器和模二加法器。其编码过程基于生成多项式,生成多项式描述了输入信息比特与输出编码比特之间的关系。

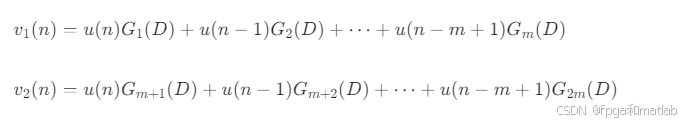

假设输入信息序列为u(n) ,卷积编码器的两个生成多项式为G1(D) 和G2(D) (对应生成多项式矩阵G的两行 ),D 是延迟算子 。则编码输出v(n) 可以表示为:

其中v1(n) 和v2(n) 是两个编码输出比特,m是约束长度。在实际计算中,如 MATLAB 程序里,是通过矩阵运算inputs*G'实现,这里inputs包含了当前输入信息比特和移位寄存器中的历史比特信息,G'是生成多项式矩阵的转置,运算结果再取模 2 得到最终编码比特。

2.Viterbi译码原理

维特比译码是一种用于最大似然序列估计的动态规划算法,广泛应用于卷积编码以及其他序列编码的译码过程中。其基本思想是在由卷积码定义的网格图(trellis diagram )上,根据接收序列找到一条与接收序列距离(或其他量度)最小的路径,这条路径对应的码字序列就是最有可能的原始发送序列,从而实现纠错译码。

在卷积码的网格图中,每一列代表一个时间点,每一行代表编码器的一个状态,状态之间的转移由输入比特决定(通常实线表示输入为 1 时的状态转移,虚线表示输入为 0 时的状态转移 ),转移时产生相应的输出编码比特。维特比译码过程就是在这个网格图上,根据接收的编码序列,计算到达每个状态的路径度量(通常用汉明距离或欧氏距离衡量接收序列与可能路径输出的距离 ),并不断更新到达每个状态的最优路径,最终找到全局最优路径,该路径对应的输入信息序列就是译码结果。

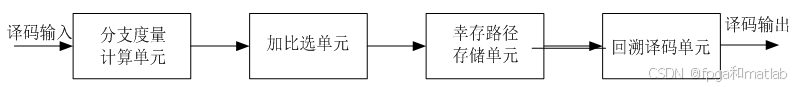

维特比译码的实现过程主要包含以下几个关键步骤:

初始化:设置初始路径度量值(通常将所有状态的初始路径度量设为 0 或一个较大的数 )和初始状态(一般设为全零状态 )。在 MATLAB 程序中虽未完整展示译码部分,但理论上这是起始步骤。

分支量度计算:对于每个时间点接收到的一对编码符号(对应卷积码输出的两个比特 ),计算其与从当前状态出发的所有可能分支的输出符号之间的距离(如汉明距离 ),这个距离就是分支量度。例如,若接收符号为[1 0] ,从某状态出发有两条可能路径,输出分别为[0 0]和[1 1] ,则与这两条路径输出的汉明距离分别为 1 和 2,这两个距离就是对应的分支量度。

路径量度更新:进入某一状态的所有分支量度与其前状态路径量度累加求和,得到新的路径量度。比如,某状态有两条路径进入,前状态路径量度分别为 3 和 5,当前分支量度分别为 1 和 2,则新的路径量度分别为 3 + 1 = 4 和 5 + 2 = 7 。

幸存路径选择:比较到达当前状态的所有新路径量度的大小,选择最小(或最大,取决于度量定义 )的路径量度作为该状态的新路径量度,并保存与此路径对应的码字,这条路径就称为幸存路径。

回溯判决:在所有时间点的运算完成后,在最后时刻选择路径量度最优(如最小 )的状态,然后从该状态开始回溯,根据保存的幸存路径信息,得到最可能的原始信息序列,即译码结果。

3.卷积编码与Viterbi译码的FPGA设计构架

本系统,整体设计构架如下:

卷积编码(后续章节将详细介绍卷积编码器的实现过程):

维特比译码(后续章节将详细介绍维特比译码的实现过程):

针对这个结构,我们将要学习的卷积编码与Viterbi译码工作步骤和内容如下:

1.通过MATLAB编写一个卷积编码与Viterbi译码算法,作为FPGA设计时的参考依据;

2.实现基于FPGA的217卷积编码器;

3.实现基于FPGA的维特比译码器——BM分支度量模块;

4.实现基于FPGA的维特比译码器——ACS加比选单元;

5.实现基于FPGA的维特比译码器——幸存路径存储单元;

6.实现基于FPGA的维特比译码器——回溯译码单元;

7.卷积编码+维特比译码整体实现;

8.卷积编码+维特比译码的编码增益分析和FPGA误码率统计;

4.参考文献

[1]赵旦峰,刘会红.卷积码Viterbi译码算法的FPGA实现[J].现代电子技术, 2004, 27(1):3.DOI:10.3969/j.issn.1004-373X.2004.01.015.

[2]刘少阳,邹永.(2,1,7)卷积编码及其维特比译码算法的软件实现[J].信息与电子工程(6):467-469[2025-05-01].DOI:10.3969/j.issn.1672-2892.2006.06.016.

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?