目录

中断1

来自PL的中断,接前一篇。

SPI中断(来自PL)

中断号

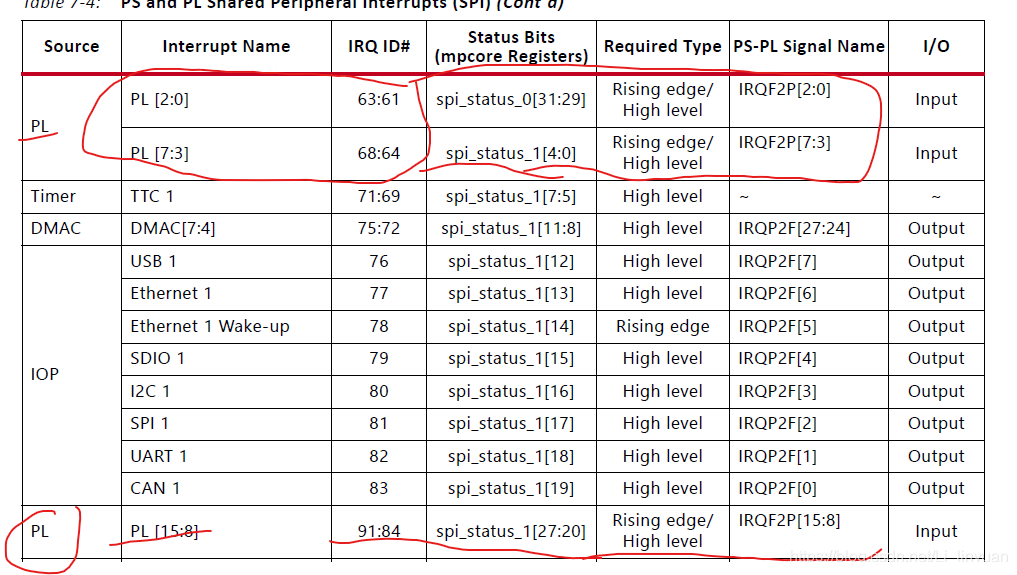

来自PL的中断信号是属于SPI中断,在中断表中可以看到

具体的中断号为61~68和84~91共16个中断,可供给PL使用。

中断配置

中断信号的敏感表和优先级是可以配置的,修改指定的寄存器即可。

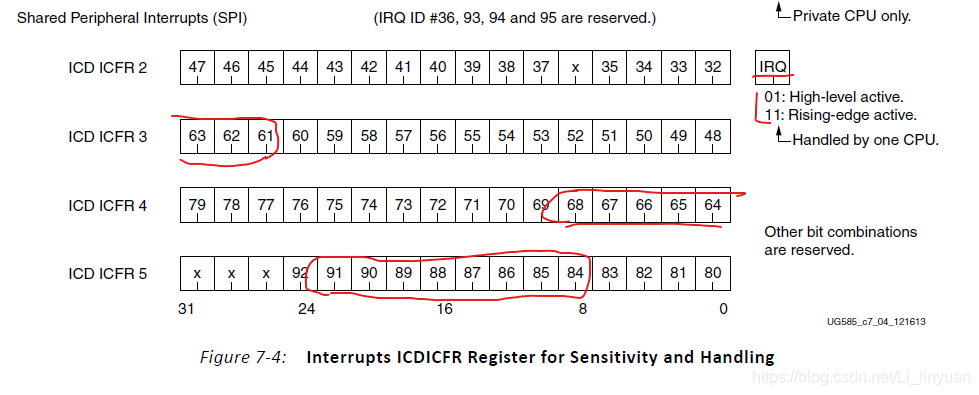

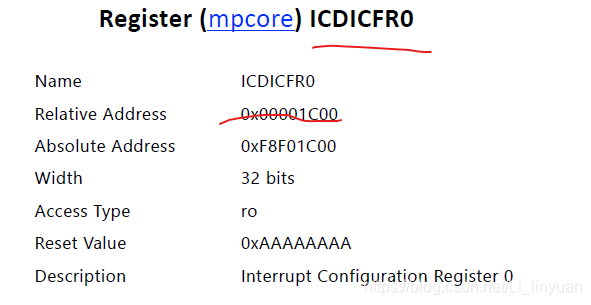

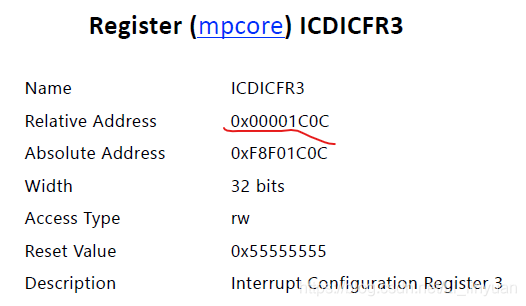

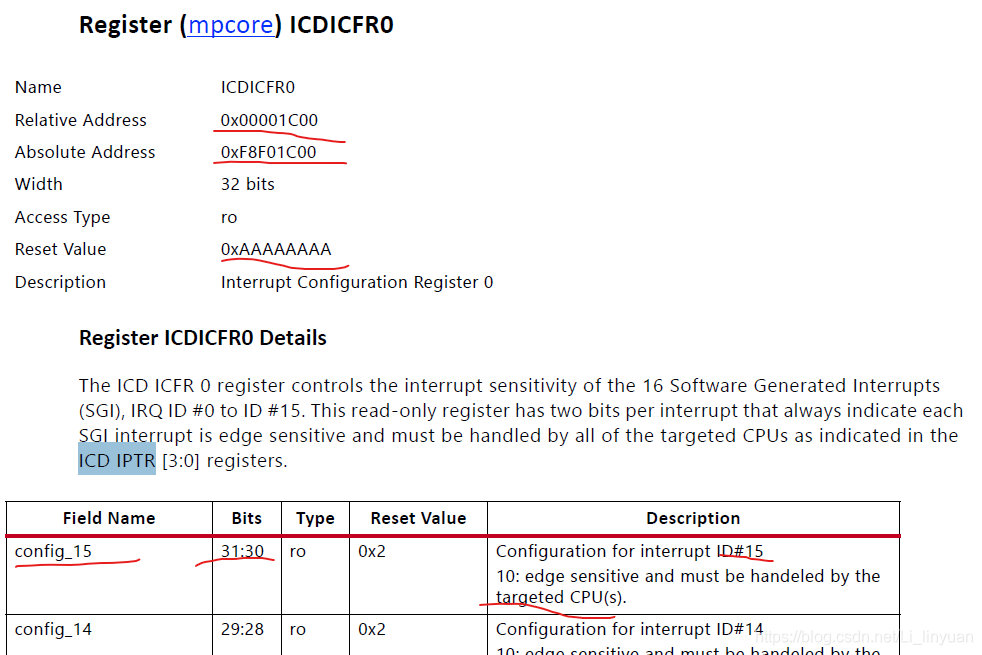

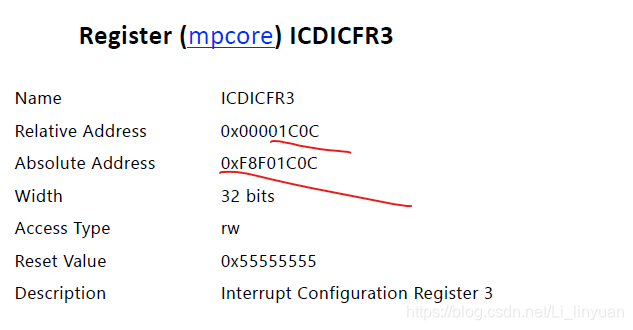

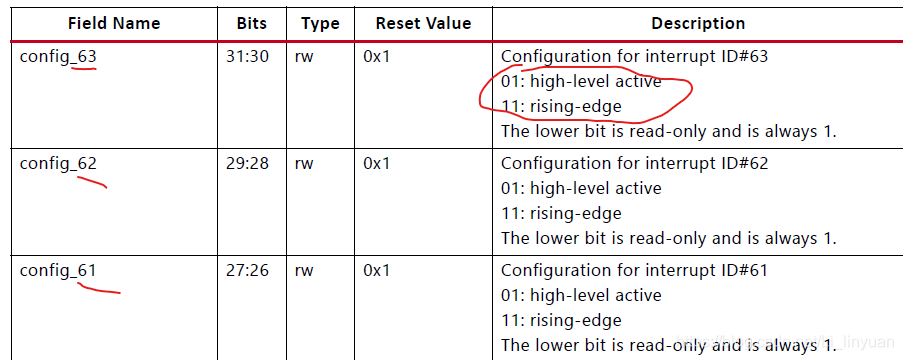

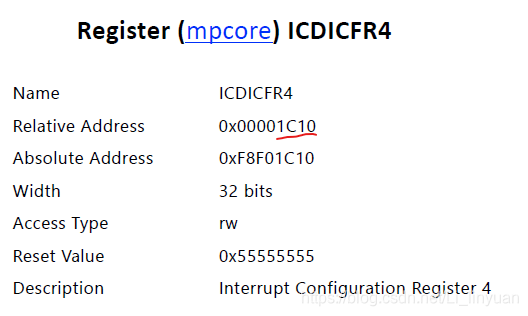

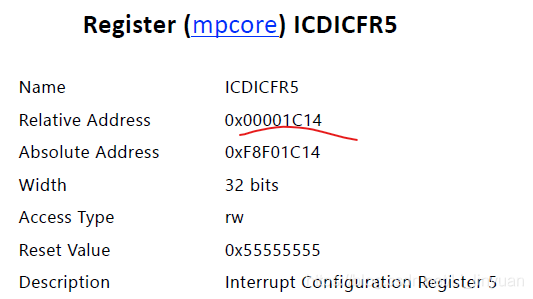

触发敏感表

每个中断信号有2Bit的控制位。

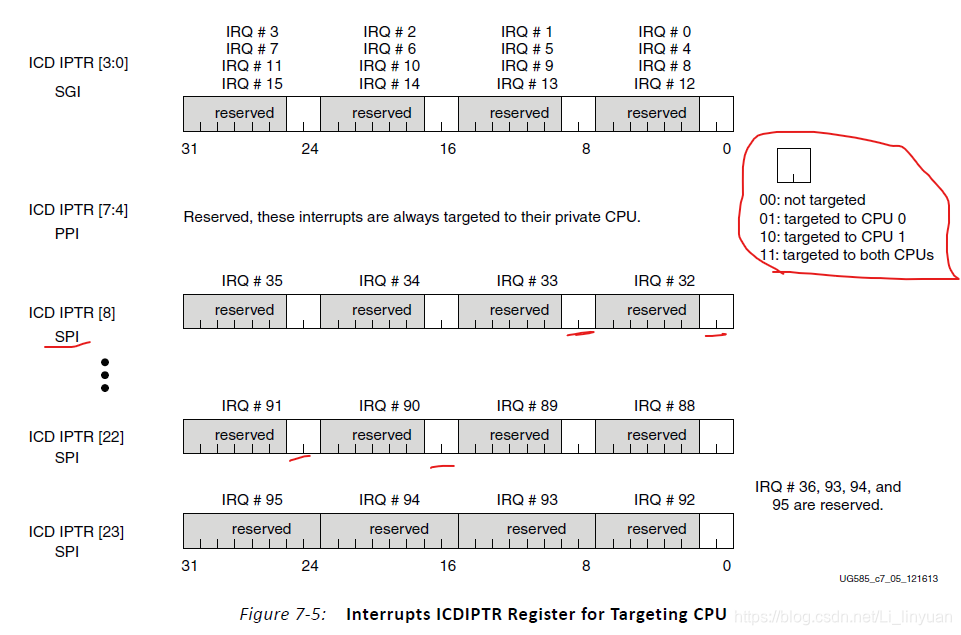

Targeted to CPU

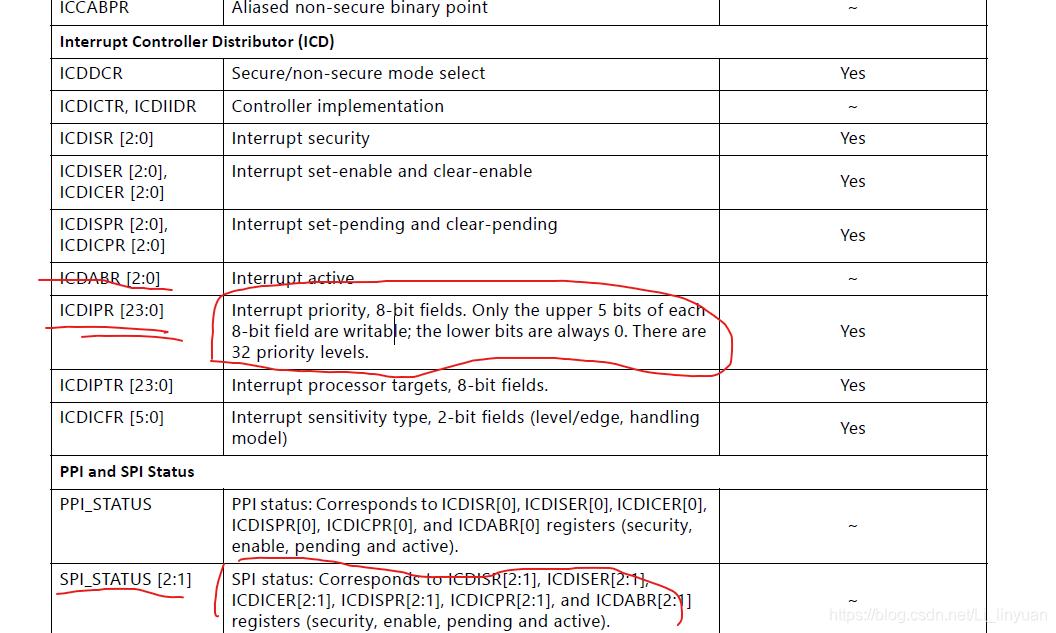

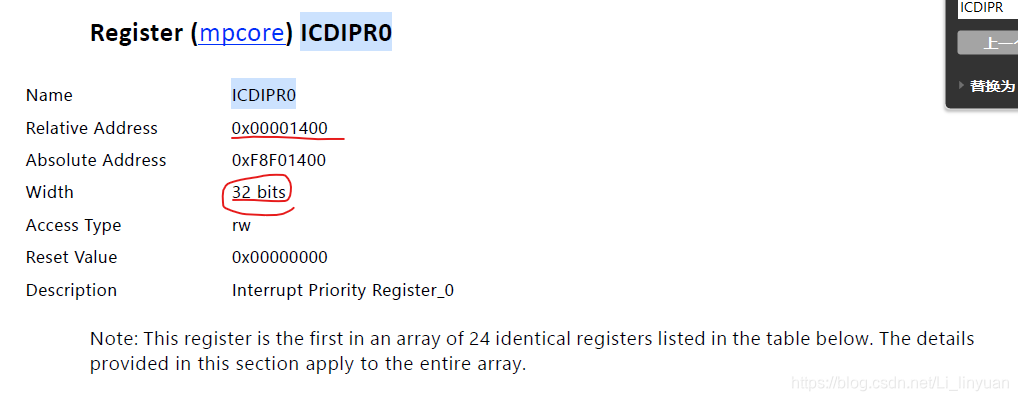

优先级Priority

共24个32位寄存器组成优先级表。每字节只有高5bit可写,低3bit为0,

共有32个等级。

寄存器

硬件系统

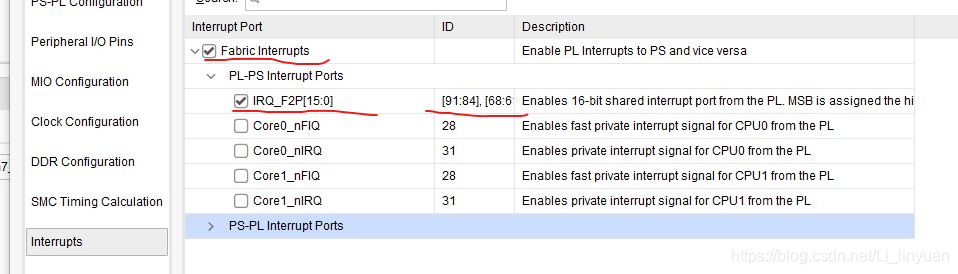

在之前的GPIO的硬件上做修改,在ZYNQ设置页面,勾选中断

选择第一个SPI中断接口。

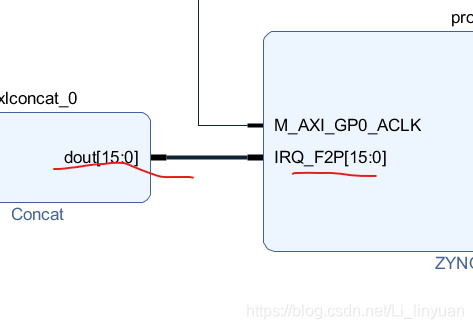

这里我使用一个16位宽的GPIO连接16根中断引脚。

如果多个使用concat合并连接

软件系统

PL中断

初始化中断控制器。打开中断,连接中断操作。

这里我使用一个16位宽的GPIO连接16根中断引脚。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

147

147

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?