1 分析

- floorplan兼封装岗

-

优势:项目初期项目部协同各个部门确定项目规划时,该岗位需协同硬件部门/soc部门/封装部门,去评估封装和floorplan兼容的合理性,评估芯片大致面积,以及评估power架构设计是否可行。该阶段时间长,定了整个芯片的大概基调,该岗位对整个芯片的宏观属性是最为了解的。最为重要的是,整体工作量就前期忙,如果还做整芯片PV的话,就是前期和后期忙,能够持续的在项目中做PL。

-

缺点:对于芯片时钟架构/具体的数据流/timing收敛等知识缺乏,而芯片后端部门的主要工作都集中于此,该岗位对外和其他部门交流畅通,但是对内对接PR遇到的问题时,会显得乏力。

-

- top PR岗

-

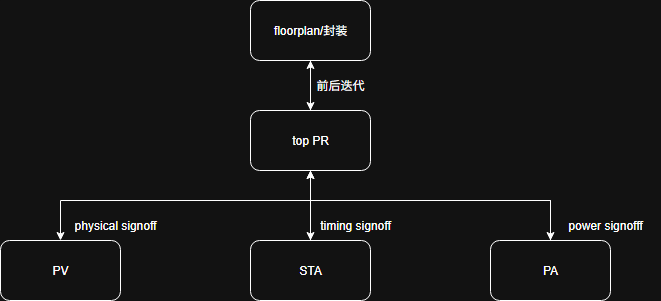

优势:作为后端部门工作量最大的岗位,top PR会协调floorplan/各个sys/STA/PV/PA之间的工作运转,是后端部门名副其实的核心。同时在深入设计方面,与IP/SOC也交流遇到的问题,对芯片架构/power架构/时钟架构都有非常深入的了解。项目前期,工作量小,作为PL参与前期flooprlan和封装的会议讨论,中期和STA/各个sys进行项目迭代,后期和STA/各个sys进行timing最后收敛工作,和PV进行DRC/LVS/ANT消除工作,和PA进行Power signoff工作。

-

缺点:工作量太大,如果作为PL完整参与一个项目后,精力会严重消耗,需要休息和缓解。很难连续作为项目的PL。

-

- block PR

-

相对来说信息量封闭一点,交流协作的东西较少。

-

缺乏floorplan对整芯片的宏观属性把控,也缺乏top PR对整芯片的数据流把控。

-

- STA

-

对物理方面知识了解太少,很多决定无法把控。

-

- PV

-

知识面更为封闭

-

- PA

-

知识面最为封闭

-

2 总结

就我看来,top PR作为后端部门的核心,协同后端各个岗位进行协同作战,如果兼具了解floorplan/封装岗位,和各个部门协商芯片的前期规划,那相当于既串联起了后端部门在整个项目中与各个部门的协同交流,也串联起了后端部门内部的协同交流,这无疑是成长最快的阶段。

9719

9719

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?