一,用户FPGA逻辑接口和搭建FPGA工程

AXI4 从接口块:AXI4 从站接口将 AXI4 事务映射到 UI,以向内存控制器提供行业标准总线协议接口。

用户界面块:UI 块向用户提供 FPGA 逻辑块。它通过呈现平面地址空间和缓冲读写数据来提供对本机接口的简单替代。

内存控制器和本机接口:内存控制器(MC)的前端显示 UI 块的本机接口。本地接口允许用户设计提交存储器读写请求,并提供将数据从用户设计移动到外部存储器件的机制,反之亦然。内存控制器的后端连接到物理接口,并处理该模块的所有接口要求。 内存控制器还提供了重新排序选项,重新排序接收的请求以优化数据吞吐量和延迟。

用户接口:连接到 FPGA 用户设计,以允许访问外部存储设备。

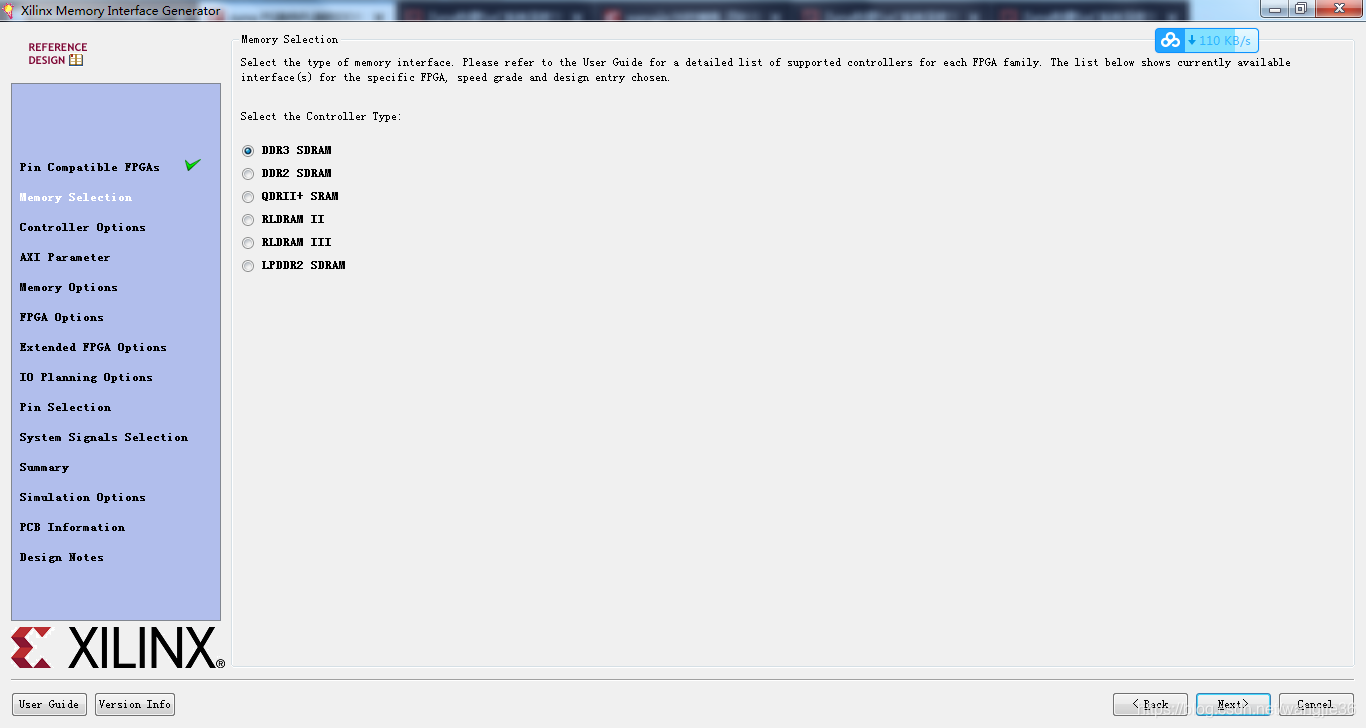

1,一路NEXT选择芯片型号

2,设置 MIG 内核时钟频率为

本文详细介绍了如何在ZYNQ FPGA中配置和使用内存控制器进行DDR内存的读写测试。首先,讲解了AXI4从接口和用户界面块的作用,然后阐述了内存控制器的功能及本地接口的设置。接着,逐步指导了MIG内核的配置,包括时钟频率、输入频率、终端阻抗的选择等。最后,提到了FPGA逻辑接口的修改和测试代码的编写,以及仿真时钟的调整。整个过程涵盖了从硬件配置到软件逻辑的完整步骤。

本文详细介绍了如何在ZYNQ FPGA中配置和使用内存控制器进行DDR内存的读写测试。首先,讲解了AXI4从接口和用户界面块的作用,然后阐述了内存控制器的功能及本地接口的设置。接着,逐步指导了MIG内核的配置,包括时钟频率、输入频率、终端阻抗的选择等。最后,提到了FPGA逻辑接口的修改和测试代码的编写,以及仿真时钟的调整。整个过程涵盖了从硬件配置到软件逻辑的完整步骤。

订阅专栏 解锁全文

订阅专栏 解锁全文

4104

4104

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?