目录

1 问题场景

在先进工艺(如TSMC 22nm)中,CTS阶段优化Skew时,若忽略IR Drop影响,可能导致:

- 关键路径时序违例(即使满足理论Skew要求)

- 时钟抖动(Jitter)恶化 → 降低芯片最高频率

2 物理机制:为什么IR Drop会扭曲Skew?

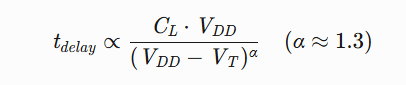

- 时钟缓冲器(Clock Buffer)的延迟公式:

-

- 关键点:延迟对VDD高度敏感!

- IR Drop导致VDD局部降低 → 该区域Buffer延迟增大 → 实际Skew ≠ 理论Skew

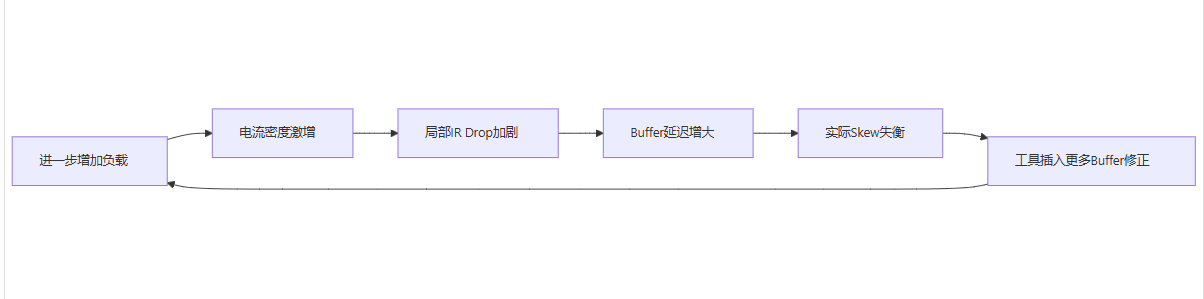

3 后端设计中的恶性循环

4 物理设计对策(Sign-off阶段必须验证)

4 物理设计对策(Sign-off阶段必须验证)

-

协同优化方法:

阶段 措施 工具实现 CTS前 基于电源网络IR Map预标记高阻区域 RedHawk/Voltus生成电压敏感图 Buffer插入 避免在IR Drop高危区集中放置Buffer Innovus/ICC2中设置Voltage-Aware CTS 签核 动态IR Drop分析 + 时序仿真联动 PrimeTime + Voltus联合验证 -

工程技巧:

- 在时钟路径上增加去耦电容(Decap) → 稳定局部电压(注意面积开销)

- 采用网格型时钟结构(Clock Mesh) → 降低单点IR Drop影响(功耗换稳定性)

5 Sign-off Checklist

在交付CTS结果前,必须验证:

- 最差IR Drop场景下,满足skew要求

- 时钟路径电压降 ΔV < 5% VDD

- 关键寄存器时钟端抖动 Jitter < 0.15 UI(UI = 1/Frequency)

6 为什么传统CTS工具的“理想电源”模式会导致硅失效?

理想电源假设下优化的Buffer布局,在真实IR Drop分布下会产生反向Skew(预期快的路径变慢,反之亦然)

1988

1988

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?