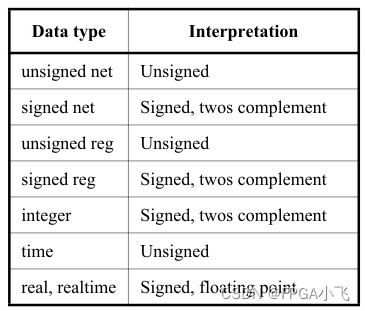

分配给 reg变量或 net 的值应默认视为无符号值,除非 reg变量或 net 已明确声明为有符号值。分配给integer变量、real变量或realtime变量的值默认应视为有符号值。分配给time变量的值应视为无符号值。有符号值(分配给real变量和realtime变量的值除外)应使用二进制表示。分配给real变量和realtime变量的值应使用浮点表示。有符号值与无符号值之间的转换应保持相同的位表示,只是解释发生变化。下表1列出了算术运算符如何解释每种数据类型:

表1:算术运算符对数据类型的解释

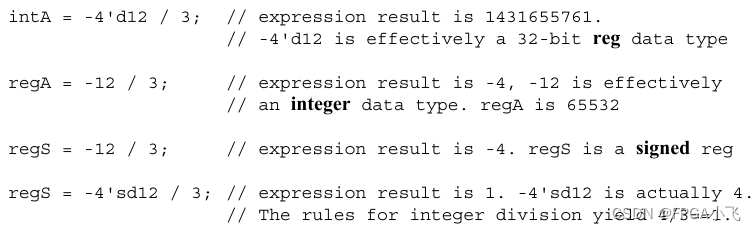

下面的示例展示了"-12 除以 3 "的各种方法--在表达式中使用integer和 reg 数据类型:

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起系统学习verilog最终标准IEEE Std 1364-2005吧!

1197

1197

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?