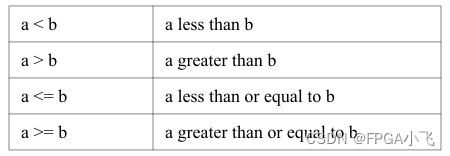

Verilog的关系运算符如下表1所示:

表1:关系运算符

如果指定的关系为假,则使用这些关系运算符的表达式将产生标量值 0;如果指定的关系为真,则表达式将产生标量值 1。如果关系运算符的任一操作数包含未知数 ( x ) 或高阻抗 ( z ) 值,则结果应为 1 位未知数 (x)。

当关系表达式的一个或两个操作数都是无符号时,表达式应被解释为无符号值之间的比较。如果操作数的位宽不相等,较小的操作数应被零扩展到较大操作数的大小。

当两个操作数都是带符号时,表达式应被解释为带符号值之间的比较。如果操作数的位宽不相等,较小的操作数应按较大操作数的位宽大小进行符号扩展。

如果其中一个操作数是实数操作数,则另一个操作数应转换为等价实数值,表达式应被解释为实值之间的比较。

所有关系运算符的优先级相同,关系运算符的优先级低于算术运算符。

举例如下:下面的示例说明了这一优先规则的含义:

当 foo - (1 < a) 求值时,关系表达式首先求值,然后从 foo 中减去 0 或 1。当 foo - 1 < a 求值时,操作数 foo 的值减 1,然后与 a 比较。

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起系统学习verilog最终标准IEEE Std 1364-2005吧!

1562

1562

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?