一、CS5269AN介召

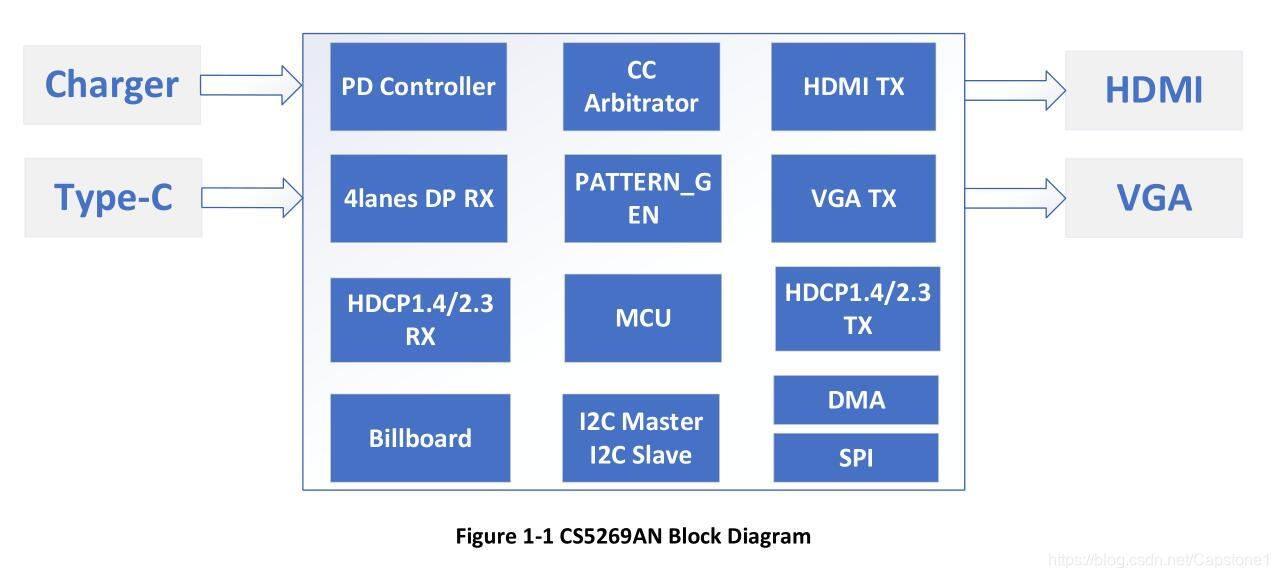

Capstone CS5269AN是一款高性能Type-C/DP1.4至HDMI2.0b和VGA转换器,设计用于USB Type-C源或DP1.4源连接到HDMI2.0b接收器。CS5269AN集成了DP1.4兼容接收机、兼容HDMI2.0b的发射机和VGA输出接口。另外,两个CC控制器包括CC通信,以实现DP Alt模式和PD传输功能,一个用于上游Type-C端口和另一个用于下游端口。

DP接口包括4条主通道、辅助通道和HPD信号。最高支持5.4Gbps(HBR2)的数据速率。DP接收机兼容HDCP1.4和HDCP2.3内容保护方案具有嵌入式密钥,用于数字音视频内容的安全传输。

HDMI接口包括4个TMDS时钟/数据对、DDC和HPD信号。HDMI发射能够支持高达6Gpbs的数据速率,足以处理高达FHD 1080p 120Hz的视频分辨率和UHD 4k 60Hz格式。HDMI发射包含支持HDCP1.4和HDCP2.3。由于包含HDCP,CS5269AN允许安全传输受保护的内容,嵌入式密钥可提供最高级别的HDCP密钥安全性。

CS5269AN是一种高度集成的单芯片,适用于多个细分市场和显示应用,如适配器、扩展坞等。

图1-1 CS5269AN框图

二、CS5269AN特性

总则

Ÿ USB Type-C 规范 1.2

兼容VESA DisplayPort TM (DP) v1.4

兼容HDMI规范v2.0b,数据速率高达每通道6-Gbps。

兼容USB Power Delivery(PD) v 3.0 t

支持所有USB Type-C Channel Configuration (CC)通道配置

内置晶振,无需外部晶振

内置MCU和SPI flash

嵌入式V-sync/H-sync

嵌入式EDID(如果终端设备没有,CS5269AN将响应EDID)

支持HDCP 1.4和HDCP2.3,带on-chip keys以支持HDCP中继器。

支持RGB 4:4:4 8/10位bpc和YCbCr 4:4:4、4:2:2、4:2:0 8/10位bpc

192KHz x8通道的最大音频采样率

LPCM和压缩音频编码格式

用于芯片控制的辅助通道、I2C主机接口

USB Type-C DisplayPort(DP)Alt模式输入(接收器)

USB Type-C规范1.2和向后兼容Type-C规范1.0

VESA DisplayPort TM v1.4兼容。支持4-lane

内置CC控制器,用于插头和方向检测

用于充电器和正常通信的双CC端口

高达HBR2(5.4-Gbps)输入。内置高性能自适应均衡器。支持1-MHz AUX

USB Type-C通道配置(CC)功能

USB Power Delivery Spec 3.0 兼容集成USB Power Delivery (PD-BMC) PHY. Support for Message Protocol. 支持Policy Engine. 支持basic Device Policy Manager

支持热插拔检测(HPD)

HDMI数字输出

兼容HDMI 2.0b

每个通道的最大数据速率高达6-Gbps

支持高达3840 x2160@60Hz 或者4096x2160@60Hz

音频流处理

LPCM和压缩音频编码格式

192k Hz x8通道的最大音频采样率支持高动态范围(HDR)元数据处理

VGA输出接口

时钟频率高达210MHz的三重8位DAC(数模转换器)

支持高达1920x1200@60Hz, 1920x1440@60Hz (降低消隐),2048x1152@60Hz (降低消隐),以及2048x1536@60Hz (降低消隐)

嵌入式V-sync/H-sync缓冲

符合VESA VSIS v1r2

其它

支持I2C主从高达400 kHz。

HBM 4KV用于连接器引脚

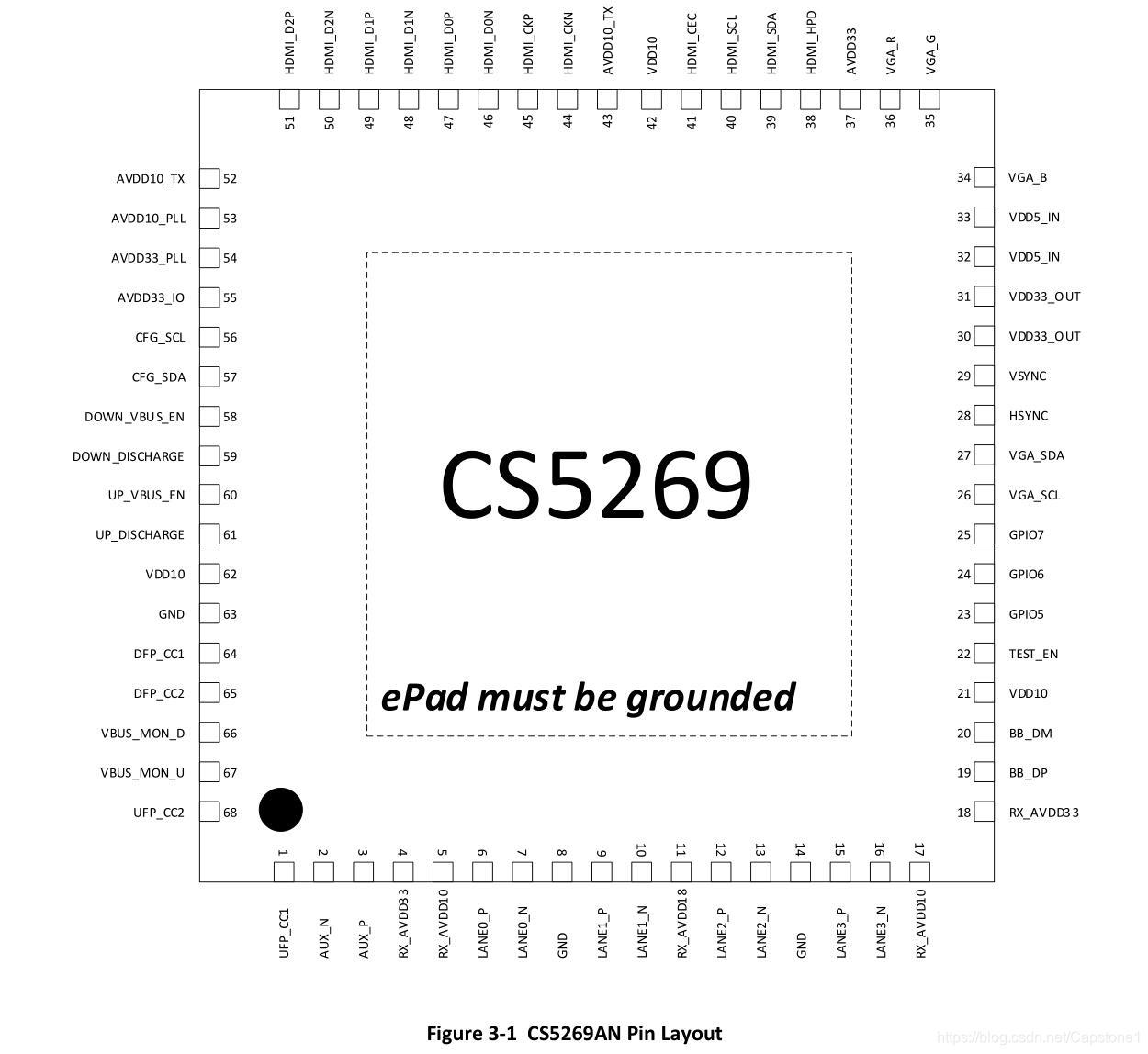

8*8mm 68针QFN68封装,带e-Pad

Power 技术

5V/1.0V系统电压,集成3.3V LDO和1.8V LDO。

三、引脚定义

3.1、引脚分配

图3-1 CS5269AN引脚布局

更详细的全套设计资料请与我联系或留言邮件,我再发出整套的设计资料。

CS5269AN是一款集成型转换器,支持Type-C/DP1.4到HDMI2.0b和VGA的转换,适用于适配器和扩展坞等应用。它具备DP1.4接收机、HDMI2.0b发射机及VGA输出接口,支持HDCP1.4和HDCP2.3内容保护,内置CC控制器和晶振,提供高数据速率和多种音频采样率。此外,该芯片还具有自适应均衡器、嵌入式EDID和热插拔检测功能。

CS5269AN是一款集成型转换器,支持Type-C/DP1.4到HDMI2.0b和VGA的转换,适用于适配器和扩展坞等应用。它具备DP1.4接收机、HDMI2.0b发射机及VGA输出接口,支持HDCP1.4和HDCP2.3内容保护,内置CC控制器和晶振,提供高数据速率和多种音频采样率。此外,该芯片还具有自适应均衡器、嵌入式EDID和热插拔检测功能。

2807

2807