一 引言

在现代FPGA系统中,传统的内存映射接口在处理高速数据流时显得力不从心。AXI4-Stream协议应运而生,它专为连续、单向、高速数据流设计,以其简洁高效的架构成为视频处理、网络通信和实时数据采集等应用的理想选择。

与复杂的AXI4-FULL协议相比,AXI4-Stream摒弃了地址概念,专注于数据的高效流动。本文将结合详细的时序图,深入解析这一重要协议。

二 核心架构:极简主义设计哲学

1 信号精简设计

AXI4-Stream通过最小化信号数量实现高效传输:

// 必需信号

input wire [DATA_WIDTH-1:0] s_axis_tdata, // 数据

input wire s_axis_tvalid, // 数据有效

output wire s_axis_tready, // 接收就绪

// 可选信号

input wire s_axis_tlast, // 包结束

input wire [DATA_WIDTH/8-1:0] s_axis_tkeep, // 字节有效

input wire [USER_WIDTH-1:0] s_axis_tuser // 用户自定义

2 握手机制:VALID/READY时序详解

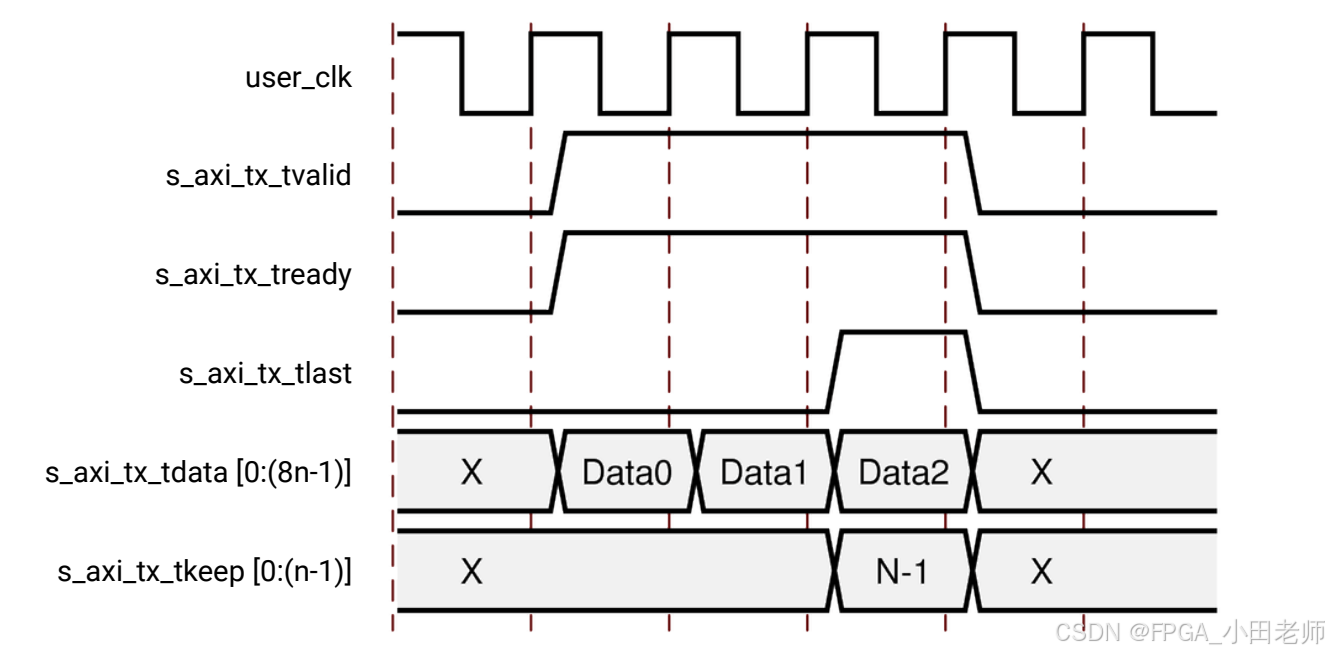

AXI4-Stream的核心是基于VALID/READY的握手机制。让我们通过时序图深入理解这一关键机制。

2.1 三种典型场景

-

理想情况:TVALID和TREADY同时有效,每个周期传输一个数据

-

源端等待:TVALID先有效,等待TREADY响应

-

目的端等待:TREADY先有效,等待TVALID数据

2.2 关键规则

-

TVALID一旦置高,必须保持直到握手完成

-

TREADY可以随时置高或置低,实现流量控制

-

数据传输发生在TVALID和TREADY同时为高的时钟上升沿

2.3 关键信号深度解析

TLAST:数据包边界

TLAST是构建高层协议的基础,它标识数据包的结束:

// 使用TLAST进行数据包计数

always @(posedge clk) begin

if (s_axis_tvalid && s_axis_tready && s_axis_tlast) begin

packet_counter <= packet_counter + 1;

end

end

应用场景:

-

以太网帧结束标识

-

视频行结束标记

-

自定义协议包边界

TKEEP:稀疏数据传输

TKEEP指示哪些字节是有效的,支持非对齐数据传输:

// 处理部分有效数据

always @(posedge clk) begin

if (s_axis_tvalid && s_axis_tready) begin

for (int i = 0; i < DATA_WIDTH/8; i++) begin

if (s_axis_tkeep[i]) begin

output_buffer[i*8+:8] <= s_axis_tdata[i*8+:8];

end

end

end

end

TUSER:元数据传输

TUSER传递与数据相关的附加信息:

// 视频流中的同步信号传递

assign s_axis_tuser[0] = vertical_sync; // 场同步

assign s_axis_tuser[1] = horizontal_sync; // 行同步

三 实战应用案例

案例1:视频处理流水线

module video_processing #(

parameter DATA_WIDTH = 24

)(

input wire clk,

input wire rst_n,

// 输入视频流

input wire [DATA_WIDTH-1:0] s_axis_tdata,

input wire s_axis_tvalid,

output wire s_axis_tready,

input wire s_axis_tuser, // 帧/行同步

input wire s_axis_tlast, // 行结束

// 输出处理后的视频流

output wire [DATA_WIDTH-1:0] m_axis_tdata,

output wire m_axis_tvalid,

input wire m_axis_tready,

output wire m_axis_tuser,

output wire m_axis_tlast

);

// 色彩空间转换、滤波等处理逻辑

// 保持流式处理,极低延迟

endmodule

案例2:数据包解析器

module packet_parser #(

parameter DATA_WIDTH = 32

)(

input wire clk,

input wire rst_n,

// AXI4-Stream输入

input wire [DATA_WIDTH-1:0] s_axis_tdata,

input wire s_axis_tvalid,

output wire s_axis_tready,

input wire s_axis_tlast,

// 解析结果

output reg [15:0] packet_length,

output reg [7:0] packet_type,

output reg packet_valid

);

reg [1:0] parse_state;

reg [15:0] byte_counter;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

parse_state <= 2'b00;

packet_valid <= 1'b0;

end else if (s_axis_tvalid && s_axis_tready) begin

case (parse_state)

2'b00: begin // 解析包头

packet_type <= s_axis_tdata[7:0];

packet_length <= s_axis_tdata[31:16];

parse_state <= 2'b01;

end

2'b01: begin // 处理包体

if (s_axis_tlast) begin

packet_valid <= 1'b1;

parse_state <= 2'b00;

end

end

endcase

end else begin

packet_valid <= 1'b0;

end

end

assign s_axis_tready = 1'b1; // 始终准备接收数据

endmodule

四 调试技巧和问题排查

ILA监控:实时观察TVALID/TREADY握手时序

常见问题排查

-

死锁:检查TVALID/TREADY的依赖关系

-

数据丢失:确认背压机制是否正确实现

-

性能瓶颈:分析关键路径和资源利用率

五 总结

AXI4-Stream协议以其简洁高效的设计,成为FPGA数据流处理的首选方案。掌握其核心要点:

-

理解握手机制:VALID/READY是协议的灵魂

-

善用可选信号:TLAST、TKEEP、TUSER提升系统功能

-

优化流水线设计:平衡吞吐量、延迟和资源消耗

-

掌握调试方法:快速定位和解决性能瓶颈

在实际项目中,AXI4-Stream能够显著简化数据流架构设计,提高系统性能。无论是视频处理、网络通信还是高速数据采集,它都是构建高效FPGA系统的利器。

AXI4-Stream协议深度解析

AXI4-Stream协议深度解析

1050

1050

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?