在之前的文章中,我们介绍了如何封装AXI_Reg配置寄存器IP核Vivado实战:封装AXI4-Lite配置寄存器IP核(AXI_Reg)。本文将重点介绍如何使用AXI Verification IP(AXI VIP)FPGA验证利器:全方位解析AXI Verification IP (AXI VIP)对这个IP核进行全面的仿真验证,确保其功能的正确性和可靠性。

一、仿真环境搭建

1.1 仿真工程结构

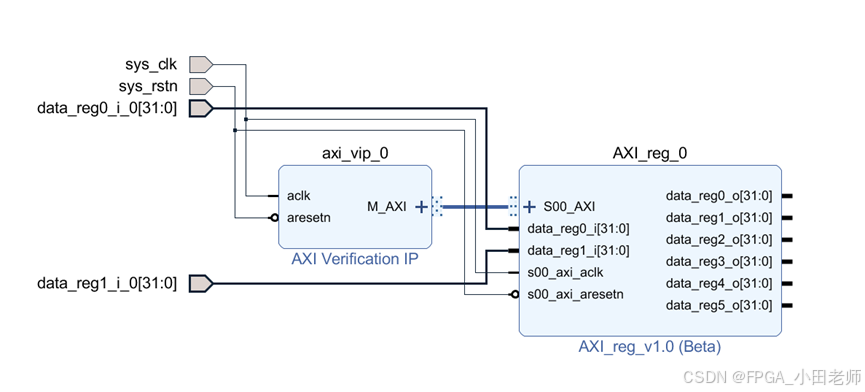

我们搭建的仿真环境包含以下组件:

-

AXI VIP:作为AXI主设备,模拟处理器对IP核的访问

-

AXI_Reg IP核:待测试的配置寄存器模块

-

时钟和复位发生器:提供系统时钟和复位信号

仿真环境结构图:

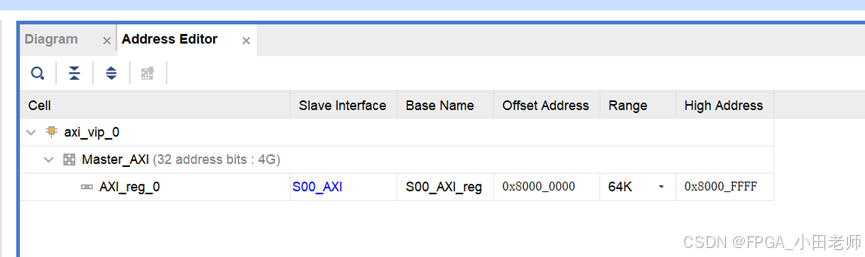

1.2 地址空间分配

在仿真中,我们为AXI_Reg IP核分配了以下地址空间:

-

基地址:

0x8000_0000 -

写地址范围:

0x8000_0000-0x8000_001C(对应8个配置寄存器) -

读地址范围:

0x8000_0020-0x8000_003C(对应8个状态寄存器)

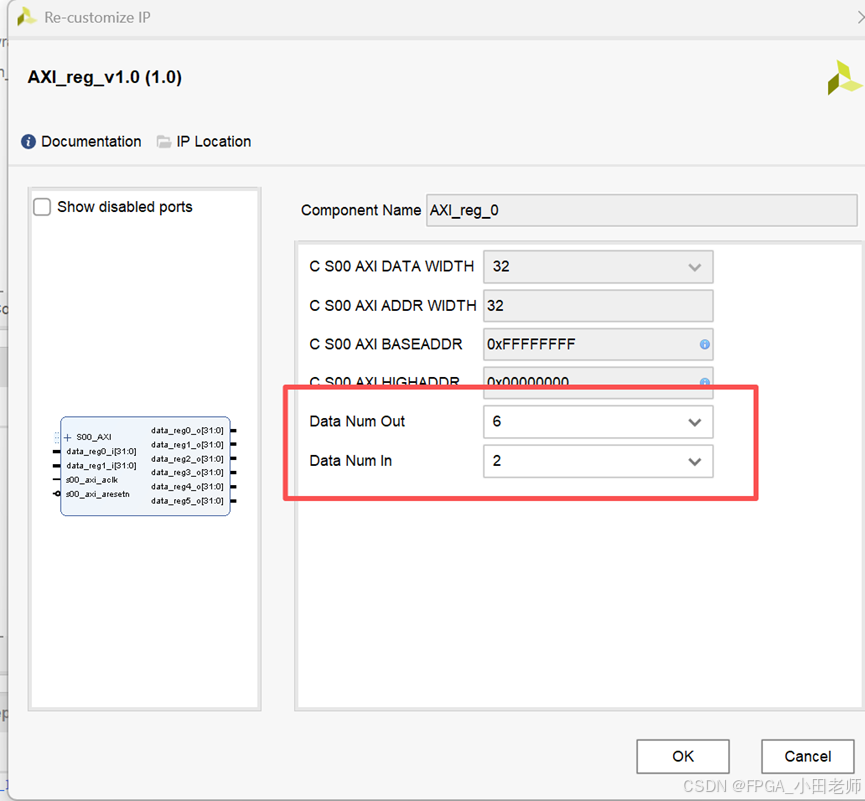

1.3 IP核配置

我们将AXI_Reg IP核配置为:

-

输出寄存器数量:6个(

data_reg0_o-data_reg5_o) -

输入寄存器数量:2个(

data_reg0_i-data_reg1_i) -

数据位宽:32位

-

地址位宽:32位

配置界面截图:

二、测试平台设计

2.1 测试平台代码

以下是测试平台代码,展示了如何使用AXI VIP对AXI_Reg IP核进行读写测试,完整代码请自行下载

//Main process

initial begin

mst_agent = new("master vip agent",DUT.design_1_i.axi_vip_0.inst.IF);

mst_agent.set_agent_tag("Master VIP");

mst_agent.start_master();

mst_agent.AXI4LITE_WRITE_BURST(32'h8000_0000,0,32'h5A5A_5A5A,mtestBresp);

mst_agent.AXI4LITE_WRITE_BURST(32'h8000_0004,0,32'hA5A5_A5A5,mtestBresp);

mst_agent.AXI4LITE_WRITE_BURST(32'h8000_0008,0,32'h1B1B_1B1B,mtestBresp);

mst_agent.AXI4LITE_WRITE_BURST(32'h8000_000C,0,32'h2C2C_2C2C,mtestBresp);

mst_agent.AXI4LITE_WRITE_BURST(32'h8000_0010,0,32'h3D3D_3D3D,mtestBresp);

mst_agent.AXI4LITE_WRITE_BURST(32'h8000_0014,0,32'h4E4E_4E4E,mtestBresp);

#3000;

mst_agent.AXI4LITE_READ_BURST(32'h8000_0000,0,mtestRData,mtestRresp);

mst_agent.AXI4LITE_READ_BURST(32'h8000_0004,0,mtestRData,mtestRresp);

mst_agent.AXI4LITE_READ_BURST(32'h8000_0008,0,mtestRData,mtestRresp);

mst_agent.AXI4LITE_READ_BURST(32'h8000_000C,0,mtestRData,mtestRresp);

mst_agent.AXI4LITE_READ_BURST(32'h8000_0010,0,mtestRData,mtestRresp);

mst_agent.AXI4LITE_READ_BURST(32'h8000_0014,0,mtestRData,mtestRresp);

#300;

mst_agent.AXI4LITE_READ_BURST(32'h8000_0020,0,mtestRData,mtestRresp);

mst_agent.AXI4LITE_READ_BURST(32'h8000_0024,0,mtestRData,mtestRresp);

end

design_1_wrapper DUT(

.data_reg0_i_0 (32'haaaa_1111),

.data_reg1_i_0 (32'hbbbb_2222),

.sys_clk (clock),

.sys_rstn (resetn)

);三、仿真结果分析

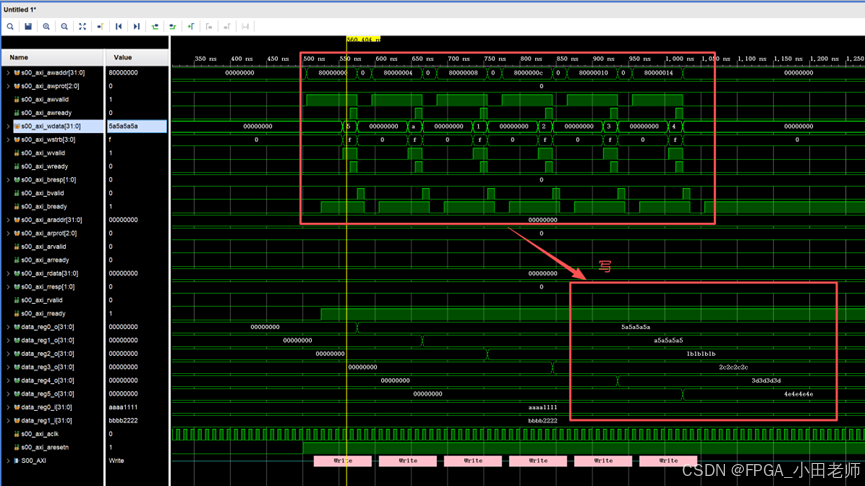

3.1 写操作验证

仿真波形显示,通过AXI VIP向AXI_Reg IP核执行写操作:

| 写入地址 | 写入数据 | 输出寄存器 | 观测值 | 结果 |

|---|---|---|---|---|

| 0x80000000 | 0x5a5a5a5a | data_reg0_o | 0x5a5a5a5a | ✅通过 |

| 0x80000004 | 0xa5a5a5a5 | data_reg1_o | 0xa5a5a5a5 | ✅通过 |

| 0x80000008 | 0x1b1b1b1b | data_reg2_o | 0x1b1b1b1b | ✅通过 |

| 0x8000000C | 0x2c2c2c2c | data_reg3_o | 0x2c2c2c2c | ✅通过 |

| 0x80000010 | 0x3d3d3d3d | data_reg4_o | 0x3d3d3d3d | ✅通过 |

| 0x80000014 | 0x4e4e4e4e | data_reg5_o | 0x4e4e4e4e | ✅通过 |

波形截图:

在仿真波形中,可以清晰地看到:

-

当时钟上升沿到来且AXI写使能有效时

-

对应地址的寄存器被正确更新

-

输出端口立即反映写入的数据值

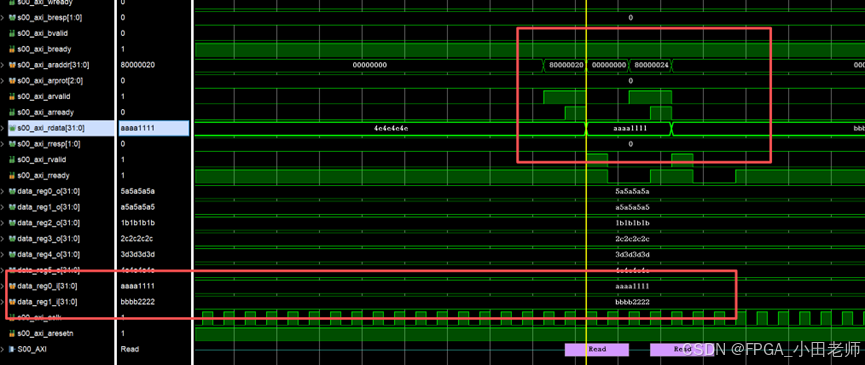

3.2 读操作验证

通过设置输入寄存器值并执行读操作:

| 输入寄存器 | 设置值 | 读取地址 | 读取数据 | 结果 |

|---|---|---|---|---|

| data_reg0_i | 0xaaaa1111 | 0x80000020 | 0xaaaa1111 | ✅通过 |

| data_reg1_i | 0xbbbb2222 | 0x80000024 | 0xbbbb2222 | ✅通过 |

波形截图:

读操作波形显示:

-

输入寄存器值正确传递到AXI读数据总线

-

读地址正确解码

-

读响应信号正常

四、结论与项目应用

4.1 仿真结论

通过全面的仿真验证,我们确认:

-

✅ 写功能正常:配置寄存器能够正确接收并锁存写入的数据

-

✅ 读功能正常:状态寄存器值能够正确通过AXI接口读出

-

✅ 地址解码正确:读写地址空间映射符合设计预期

-

✅ 时序符合要求:所有操作都在AXI协议规定的时序内完成

4.2 在反射内存项目中的应用

这个经过验证的AXI_Reg IP核将在我们的反射内存项目中发挥重要作用:

配置功能:

-

设置数据传输模式(FAST模式/同步模式)

-

配置看门狗时间参数

-

使能/禁用中断功能

状态监控:

-

读取链路状态信息

-

获取传输错误统计

-

监控中断状态寄存器

4.3 后续工作

基于本次仿真验证的成功,我们可以:

-

集成到主系统:将AXI_Reg IP核集成到完整的反射内存从板设计中

-

软件驱动开发:基于验证过的寄存器映射开发对应的设备驱动程序

-

系统级验证:在更大的系统环境中进行集成测试

五、总结

本文详细介绍了使用AXI VIP对自定义AXI_Reg配置寄存器IP核进行仿真的完整流程。通过这种方法,我们能够在实际硬件实现之前充分验证IP核的功能正确性,大大提高了开发效率和代码质量。

仿真验证的价值:

-

早期发现设计缺陷,降低后期调试成本

-

确保IP核符合AXI协议规范

-

为系统集成提供可靠的基础模块

这个经过充分验证的AXI_Reg IP核为我们的反射内存项目奠定了坚实的基础,后续我们将在此基础上构建更复杂的功能模块。

1063

1063

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?