目录

前言

在verilog的使用过程中,always语句块的使用是时许逻辑的起始点,本文就来和大家讨论一下always语句块及它们是如何使用的。

一、always语句块是什么?

alway是语句块又被称为过程块,在过程块中赋值的语句就是过程赋值语句,没错就是我们在assign学习中提到的与连续性赋值语句相对应的语句,我们先来看看它长嘛样?

举个例子

always @(posedge CLK)

Q = D;

原来是这屌样,so easy!

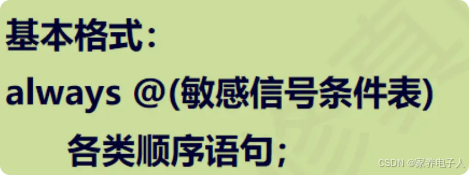

从它的格式和我们举得例子中可以看出来,这个语句只有两个部分需要我们关注:敏感信号条件表和各类的顺序语句;

首先我们所以说敏感信号条件表,从例子中我们看到是 posedge CLk ,它就是敏感信号,而 Q = D ;就是各类顺序语句,什么?你只看到一句?那是因为我善,哈哈哈只写了一句!

二、always语句的特点

1.always语句本身没有什么意义,而是和其内部封装的顺序语句构成语句块,也就是过程块,这才使得它有了底气,成为最常用的语句之一,always语句就像一层包装纸,只有它里面的东西才是它的卖点。

2.在always语句中他的赋值

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2557

2557

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?