前言

在前文中我们单独讨论了assign与always,可能有些小伙伴还是觉得有点迷糊,那我们就继续来探讨一下他们之间的区别,加深一下理解。

assign语句和always语句的主要区别?

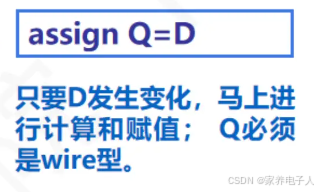

正如我们之前所说assign语句属于连续赋值语句,就像是水流一样,一直是连续的,总是处于激活状态,只要操作数有变化马上进行计算和赋值。

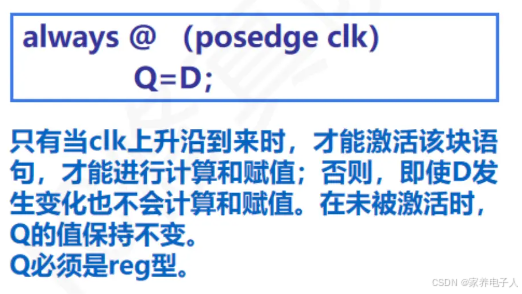

而always语句是过程赋值语句,就像是阶梯一样的,只有在阶梯上,也就是只有当激活该过程时,才会进行计算和赋值,如果该过程没有被激活,即使操作数发生变化也不会计算和赋值。

verilog中规定他们赋值目标的数据类型有差异,assign中的赋值目标必须是wire型的,而always语句中的赋值目标必须是reg型的。

always语句块中除了可以使用表达式赋值以外,还可以使用if,case等行为描述语句,还能够描述边沿变化,因此其功能比assign语句更强大(assign语句不能使用if等语句,也不能描述边沿变化)

module DFF2 (CLK,D,Q,RST,EN)

input CLK,D,RST,EN;

output Q;

reg Q;

always @(posedge CLK or negedge RST)

begin

if (!RST)

Q<=0;

else if(EN)

Q<=D

end

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2563

2563

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?