新思SYN43752芯片在低速率下把功率做得比较陡,这是因为IEEE对flatness的要求一直在放宽,低速率尖尖的是为了有更好的band edge可以更容易地通过FCC/CE等认证, 如果客户因为flatness指标有超标的话而需要调整这个功率的形状,可按如下步骤进行:

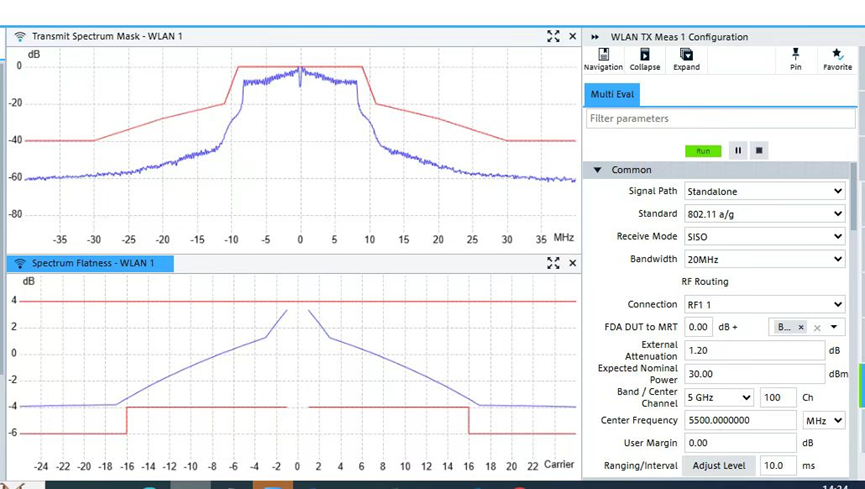

1, 默认的参数在低速率下的功率平坦度形状。如下图:

图1,测试仪器的数据

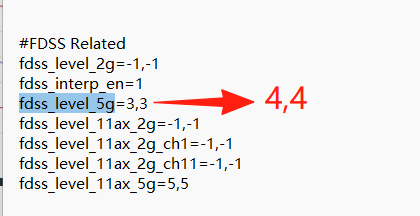

2, 在nvram文件里找到下面的参数,把调整为4,4 ,以5G为例。

图2,nvram文件中的参数

3, 保存nvram文件,并push进板子里替换原来的nvram文件,重启,并加载mfgtest 固件进入测试。

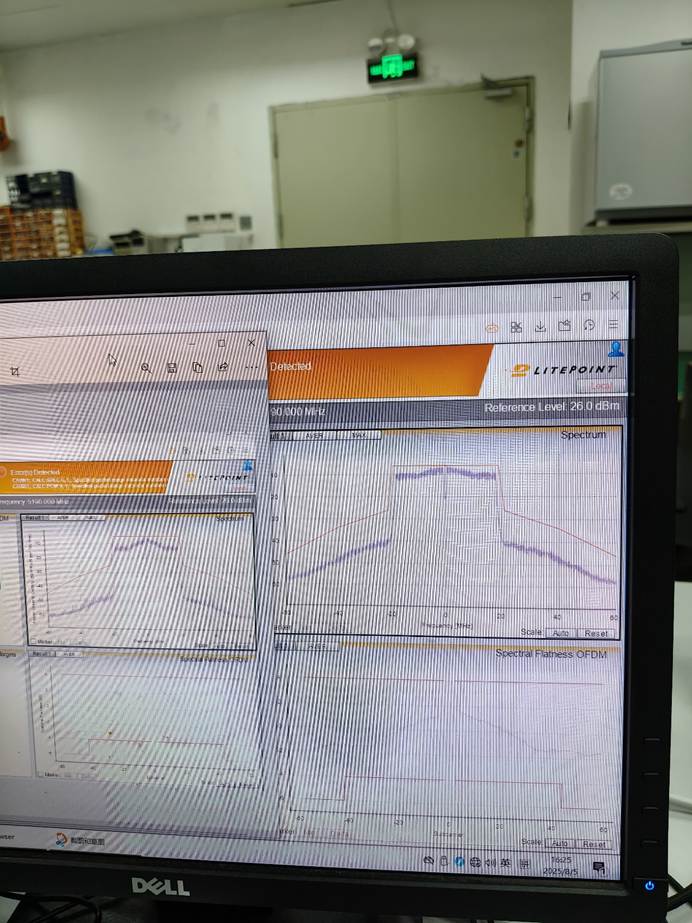

4, 左边为默认参数的功率形状, 右边为新参数的功率形状,可见功率更平了。

图3,测试仪器的数据界面

常见问题解答(FAQ)

问题1:Flatness指标在SYN43752中的明确定义是什么?

答案:

在SYN43752中,Flatness 通常指 S21插入损耗(Insertion Loss)在目标频带内的峰峰值波动(Peak-to-Peak Variation)。

· 定义:在IP核的工作频率范围内(如0至Nyquist频率),S21曲线的最大与最小值之差(单位:dB)。

· 典型场景:适用于PCIe/CXL/USB等高速接口的通道响应平坦度评估,确保信号在传输中不因频域畸变导致时序抖动恶化。

· 示例值:数据手册可能规定在0-16 GHz频段内,Flatness ≤ ±2 dB(具体需查证规格书)。

问题2:SYN43752的Flatness保证值及测试条件是什么?

答案:

保证值:

· 典型值:±1.5 dB(如8-16 GHz频段)

· 最大值:±3.0 dB(全频段,视速率模式而定)

测试条件:

· 参考负载:50Ω单端或100Ω差分阻抗

· 封装模型:包含IBIS/AMI封装寄生参数(如2.5D/3D封装)

· 环境:室温(25°C)、标称电压(如0.8V)

· 一致性标准:需满足PCIe 6.0/CXL 3.0等协议规定的眼图模板(如3.5dB ILD容忍度)。

问题3:哪些设计因素对SYN43752的Flatness影响最大?

答案:

关键影响因素包括:

1. 封装设计:BGA焊球电感、基板走线阻抗不连续。

2. PCB通道:过孔残桩(Stub)、层间介质材料(Dk/Df值)。

3. 均衡器配置:

o CTLE:高频增益补偿可改善Flatness,但过度补偿会放大噪声。

o DFE:对残留峰峰抖动有抑制作用,间接优化平坦度。

4. 工艺角(PVT):高温/低电压下放大器带宽下降,导致高频Flatness恶化。

问题4:如何通过仿真验证SYN43752的Flatness指标?

答案:

推荐工具与流程:

1. 建模:

o 使用HFSS/Q3D提取封装/PCB的S参数模型。

o 在PrimeSim HSPICE中集成SYN43752的IBIS-AMI模型。

2. 仿真设置:

o 激励:PRBS31码型,速率按IP配置(如112G PAM4)。

o 分析:执行通道频域响应(S21)及时域眼图仿真。

3. Flatness提取:

o 从Touchstone文件(.s4p)中计算目标频段(如0-32 GHz)的S21峰峰值波动。

o 脚本示例:使用Python scikit-rf库处理S参数,输出波动值。

问题5:若Flatness超标,新思提供哪些调试建议?

答案:

官方优化方案:

1. PCB层叠优化:

o 缩短高速信号参考层切换距离,减少阻抗突变。

o 选用超低损耗介质材料(如Megtron 6)。

2. SerDes配置调整:

o 启用CTLE的“Peaking Mode”提升高频增益(需权衡噪声)。

o 调整DFE抽头权重补偿特定频点凹陷。

3. 封装改进:

o 采用硅中介层(Si Interposer)减少焊球电感。

o 优化BGA escape区域走线长度匹配。

4. 诊断工具:

o 使用Synopsys PrimeWave平台执行灵敏度分析,定位Flatness瓶颈。

231

231

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?