需求分析

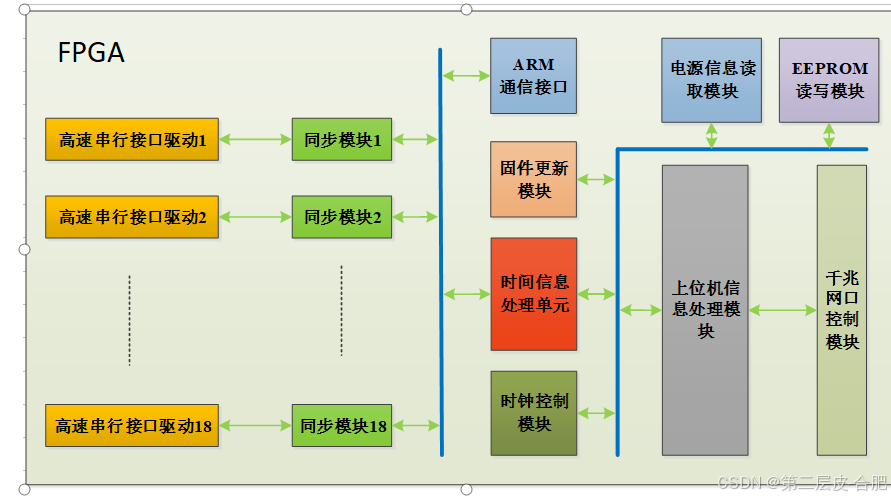

同步控制系统FPGA的功能主要是同步和上位机通信。同步主要利用FPGA的高速串行接口资源与从设备交换信息,从而使主从设备实现时间的绝对同步,上位机通信主要是利用千兆网口接收来自软件的控制信号。同步控制系统同时还能够接收外部输入的时间信息,然后对时间信息进行分发。

信号处理架构

FPGA信号处理采用模块化自顶向下进行设计,每个功能模块进行单独封装,然后由顶层实现各功能模块协同工作。FPGA固件功能模块

功能模块分解

高速串行接口驱动模块

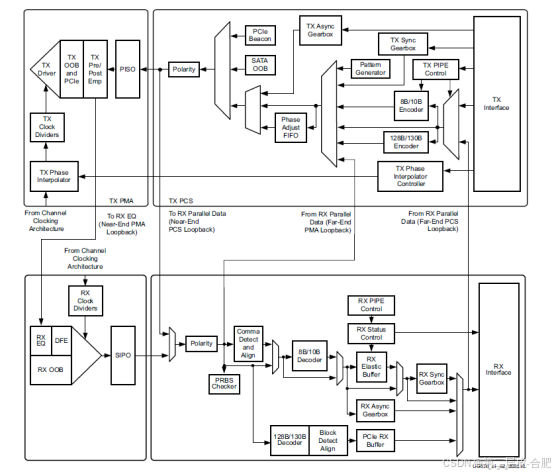

同步控制系统需要使用FPGA的高速串行接口硬核资源,该硬核资源功能非常强大,可以基于该硬核构建很多常用的高速串行接口协议。如图 62是Xilinx ultrascale Kintex FPGA的高速串行接口硬核接口图。图中可以看出其包含接收和发送两部分,每部分又包含PMA和PCS,内部资源比较丰富。

同步控制系统需要编写基于此硬核的发送和接收的驱动程序,xilinx提供了该硬核的IP核,由于同步控制系统是自定义协议,在IP核选择时,只需要8B/10B编码即可,如图 所示。

订阅专栏 解锁全文

订阅专栏 解锁全文

26

26

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?